随着RISC-V处理器的快速发展,如何保证其正确性成为了一个重要的问题。传统的测试方法只能覆盖一部分错误情况,而且无法完全保证处理器的正确性。因此,基于形式验证的方法成为了一个非常有前途的方法,可以更加全面地验证处理器的正确性。本文将介绍一种基于形式验证的高效RISC-V处理器验证方法。

1、RISC-V处理器简介

RISC-V是一种开源指令集架构,其设计简单、灵活、可扩展,因此被广泛应用于各种设备中,如手机、笔记本电脑、TLC272CDR服务器等。RISC-V指令集架构不仅仅具有开放性和可扩展性,还具有良好的性能和能耗特性,能够满足各种应用场景的需求。由于RISC-V处理器的普及,如何保证其正确性成为了一个非常重要的问题。

2、基于形式验证的方法

基于形式验证的方法是通过数学推理来证明程序的正确性。这种方法可以完全覆盖所有可能的错误情况,因此可以保证程序的正确性。但是,这种方法需要大量的人力和时间来完成,所以一般用于关键应用场景中,如航空航天、铁路交通等。

3、高效RISC-V处理器验证方法

为了提高基于形式验证的效率,可以采用以下方法:

3.1、抽象模型

在进行形式验证时,可以对处理器进行抽象,将其抽象成一个数学模型。这样可以简化处理器的复杂性,提高验证效率。抽象模型应该尽可能简单,但又不能失去关键信息。

3.2、自动化验证

自动化验证是指利用计算机程序来执行形式验证。自动化验证可以大大提高验证效率,减少人力成本。自动化验证可以用模型检查、定理证明等方法来实现。

3.3、增量验证

增量验证是指将整个处理器的验证拆分成多个小的部分进行验证,然后将这些小部分逐步合并成一个整体。这样可以大大降低验证的难度和复杂度,提高验证效率。

4、结论

基于形式验证的方法可以保证RISC-V处理器的正确性,但是需要大量的人力和时间来完成。为了提高验证效率,可以采用抽象模型、自动化验证和增量验证等方法。这些方法可以大大降低验证的难度和复杂度,提高验证效率。

-

处理器

+关注

关注

68文章

19222浏览量

229518 -

形式验证

+关注

关注

0文章

8浏览量

5695 -

RISC-V

+关注

关注

44文章

2254浏览量

46097

发布评论请先 登录

相关推荐

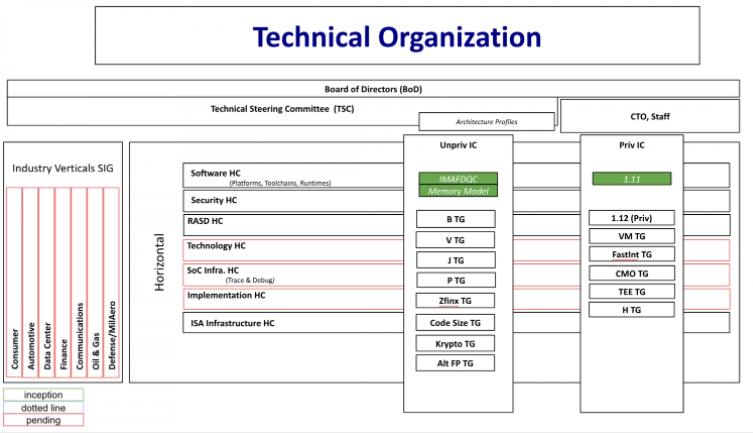

Codasip携手西门子打造RISC-V领域最完整形式验证

RISC-V是通用RISC处理器还是可定制的处理器?

创新引领|芯华章联手芯来科技提升RISC-V处理器设计验证

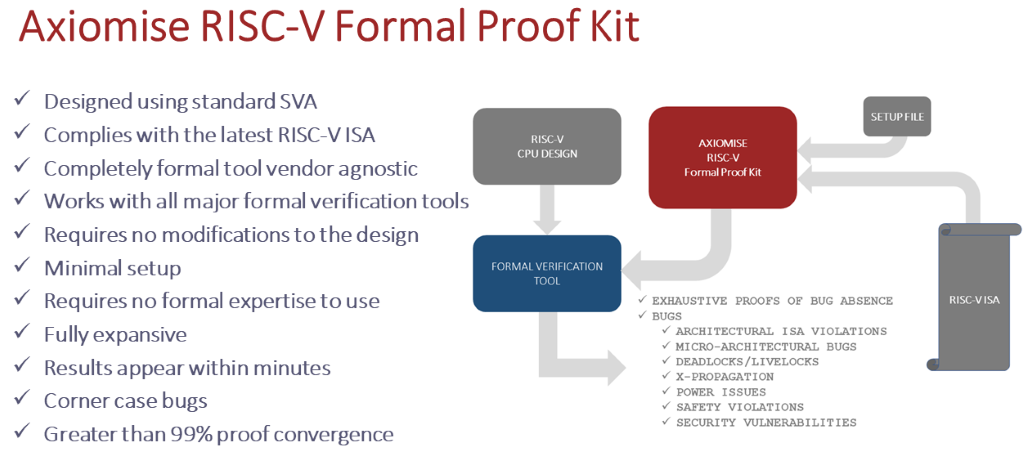

Axiomise通过形式验证公理化RISC-V处理器

关于RISC-V 处理器验证的问题

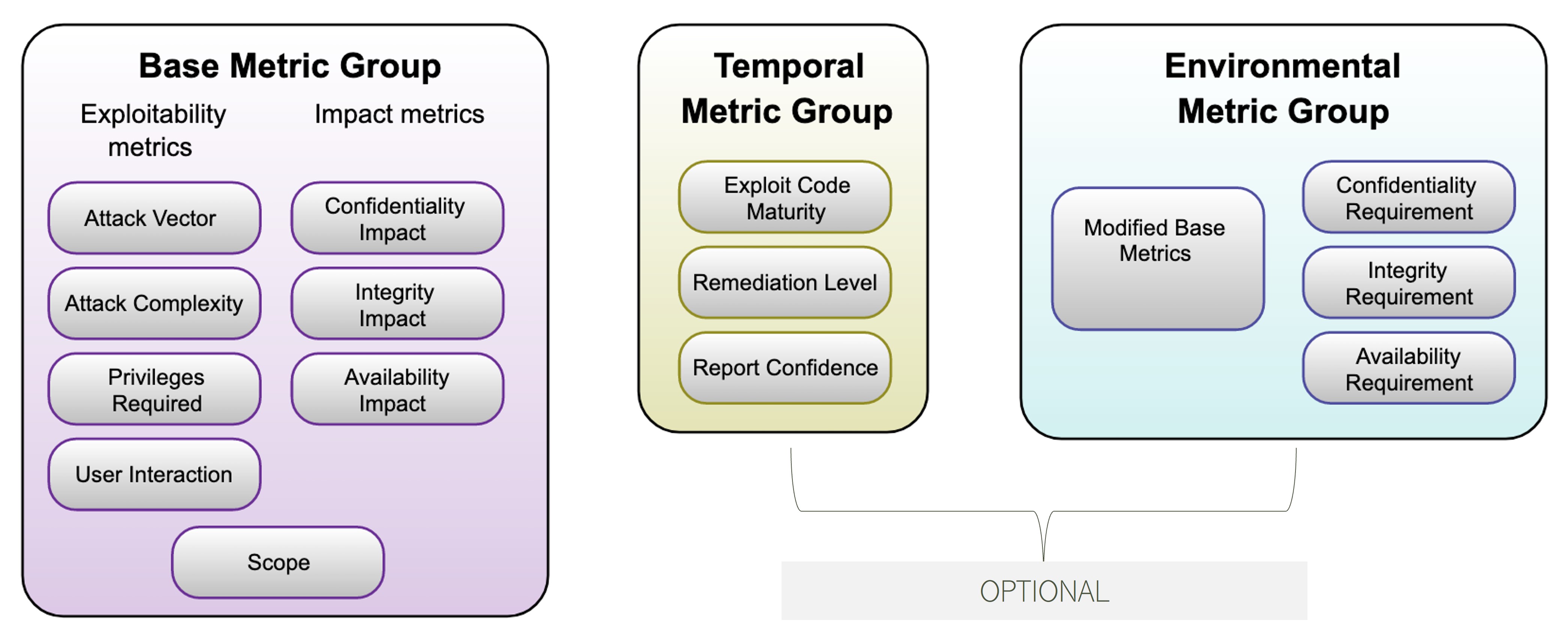

如何利用形式化验证提高RISC-V处理器质量?

利用先进形式验证工具来高效完成RISC-V处理器验证

基于形式的高效 RISC-V 处理器验证方法

思尔芯原型验证助力香山RISC-V处理器迭代加速

思尔芯原型验证助力香山RISC-V处理器迭代加速

基于形式验证的高效RISC-V处理器验证方法

基于形式验证的高效RISC-V处理器验证方法

评论