说明:这部分内容比较零散,且很多不好理解,所以这里只能选择性介绍一些内容。

使用interface代替driver部分功能

方法:

- 在interface中可以定义任务与函数,也可以使用always语句和initial语句,也可以实例化其他interface。可用其做一些低层次的转换, 如8b10b转换、 曼彻斯特编码等。这些转换动作是与transaction完全无关的。

好处:

- 让driver从底层繁杂的数据处理中解脱出来, 更加专注于处理高层数据

- 有更多的数据出现在interface中, 这会对调试起到很大的帮助(因为interface中的信号在波形文件中有记录的)

可变时钟的三种需求及对应实现方法

- 在不同测试用例之间时钟频率不同, 但是在同一测试用例中保持不变

- 例如:HDMI协议中会依据图像分辨率采用不同的时钟

- 方法一:将时钟独立成一个文件,通过include不同的时钟实现

- 方法二:在测试用例中使用config_db的set方法设置一个变量,然后在时钟实现的地方使用get方法获取该变量,将其作为时钟周期。

- 在同一个测试用例中存在时钟频率变换的情况

- 例如:PLL过渡期前和过渡期后的时钟是不一样的

- 方法一:在测试用例中使用config_db的set方法随着时间不同为时钟周期变量设置不同值。

- 既关心过渡期前后的时钟, 也关心PLL在过渡期的行为,即要求时钟变量不止是简单的可变,而且是正弦变化的。

- 例如:关心PLL过渡期内时钟行为,实际工作中时钟频率也是存在一定抖动的

- 方法一:建立一个clk的interface,然后通过config_db将对clk的驱动放在一个时钟component中,这样的话,要实现任意对clk的驱动只需要重载这个时钟component即可。

layer sequence的引入

以太网包、IP包、 UDP包、 TCP包,数据是层层封装的,为了提高测试用例的可重用性,方法有:

- 方法一: sequence中调用子sequence ——将与ip相关的代码写成一个函数, 而与mac相关的代码写成另外一个函数, 将这些基本的函数放在base_sequence中。在新建测试用例时, 从base_sequence派生新的sequence, 并调用之前写好的函数。---- 感觉更适合并列关系的测试用例

- 方法二: 使用layer sequence ——一个sequence负责产生ip_transaction, 另外sequence负责产生my_transaction, 前者将产生的ip_transaction交给后者。--- 感觉更适合包含关系的测试用例

layer sequence的示例

聚合参数的优势与问题

优势:

- 可以将interface也放入此聚合参数类中

- 使用聚合类减少了config_db::set的使用, 也会大大降低出错的概率

问题:

- 本质上是将一些属于某个uvm_component的变量变成对所有的uvm_component可见

- 在一定程度上降低了验证平台的可重用性

总结:

- 在参数聚合程度/粒度上需要权衡:更好方便的使用vs代码可重用性

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

HDMI接口

+关注

关注

1文章

134浏览量

34050 -

UVM

+关注

关注

0文章

182浏览量

19171 -

PLL电路

+关注

关注

0文章

92浏览量

6408 -

TCP通信

+关注

关注

0文章

146浏览量

4223

发布评论请先 登录

相关推荐

IC验证"为什么要学习UVM呢"

验证的基本常识,将会散落在各个章节之间。UVM的一些高级功能,如何灵活地使用sequence机制、factory机制等。如何编写代码才能保证可重用性。可重用性是目前IC界提及最多的几个词汇之一,它包含

发表于 12-01 15:09

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...

原文链接:https://zhuanlan.zhihu.com/p/345775995大家好,我是一哥,上章内容主要讲述两个内容,芯片验证以及验证计划。那本章我们主要讲述的内容有介绍什么是uvm

发表于 01-21 16:00

什么是uvm?uvm的特点有哪些呢

大家好,我是一哥,上章内容我们介绍什么是uvm?uvm的特点以及uvm为用户提供了哪些资源?本章内容我们来看一看一个典型的uvm验证平台应该是什么样子的,来看一个典型的

发表于 02-14 06:46

谈谈UVM中的uvm_info打印

uvm_info宏的定义如下: `define uvm_info(ID,MSG,VERBOSITY) \ begin \ if (uvm_report_enabled(VERBOSITY

发表于 03-17 16:41

UVM中seq.start()和default_sequence执行顺序

1. 问题 假如用以下两种方式启动sequence,方法1用sequence的start()方法启动seq1,方法2用UVM的default_sequence机制启动seq2。那么seq1

发表于 04-04 17:15

Modelsim uvm库编译及执行

第一句话是设置uvm环境变量,指定uvm的dpi位置。

第二句话是创建work工作目录。

第三句话是编译源文件,并且通过-L指定几个编译库。

第三句是执行仿真,调用uvm库uvm

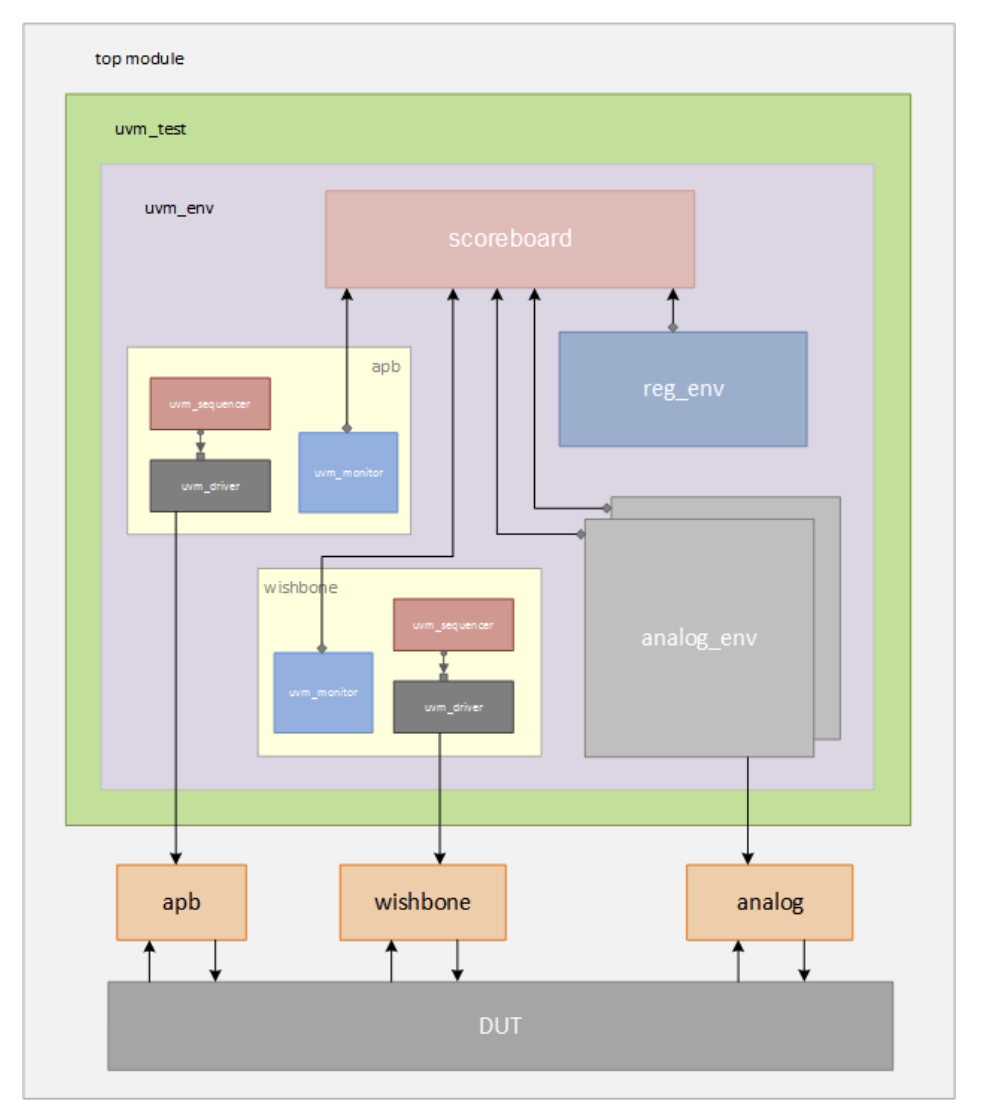

什么是UVM environment?

UVM environment**包含多个可重用的验证组件,并根据test case的需求进行相应的配置。例如,UVM environment可能具有多个agent(对应不同的interface)、scoreboard、functional coverage collec

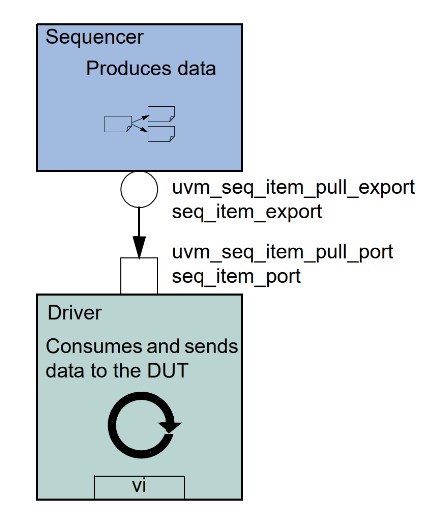

UVM driver和sequencer的通信

sequencer生成激励数据,并将其传递给driver执行。UVM类库提供了uvm_sequencer基类,其参数为request和response数据类型。

UVM中uvm_config_db机制背后的大功臣

本次讲一下UVM中的uvm_config_db,在UVM中提供了一个内部数据库,可以在其中存储给定名称下的值,之后可以由其它TB组件去检索。

UVM中uvm_config_db机制背后的大功臣

本次讲一下UVM中的uvm_config_db,在UVM中提供了一个内部数据库,可以在其中存储给定名称下的值,之后可以由其它TB组件去检索。

一文详解UVM设计模式

本篇是对UVM设计模式 ( 二 ) 参数化类、静态变量/方法/类、单例模式、UVM_ROOT、工厂模式、UVM_FACTORY[1]中单例模式的补充,分析静态类的使用,UVM中资源池的

UVM高级应用

UVM高级应用

评论