PCI Express® 5.0规范,达到32GT / s的传输速率,同时保持低功耗和与前几代威廉希尔官方网站 的向后兼容性。为此,Synopsys 还宣布与 Astera Labs 合作开发业界首款 PCIe 5.0 重定时器 SoC。人工智能、云、数据中心和 5G 等新兴应用一直在推动带宽需求的指数级增长,而 PCIe 已经不断发展以满足这些不断增长的需求。

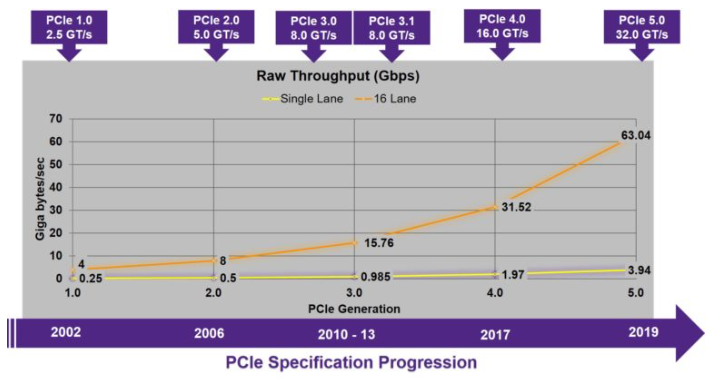

PCIe 协议在过去 15+ 年中迅速发展,从 2 年第 5 代的 2002.1GT/s 原始比特率,到今天最新的 PCIe 32.5 的 0GT/s。PCI Express 从桌面计算到云的采用,对增加吞吐量、减少延迟、占用空间和功耗的需求不断增长,一直在推动 PCIe 标准的创新。

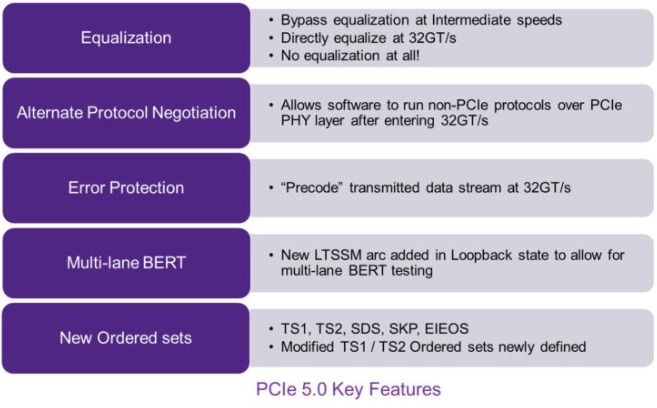

PCIe 5.0 增加了重要的新功能,例如新的均衡选项和备用协议协商 (APN),以满足系统要求,具有可预测和稳定的带宽、延迟和功率(见下文)。

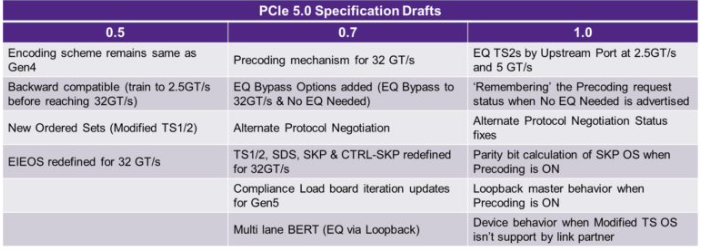

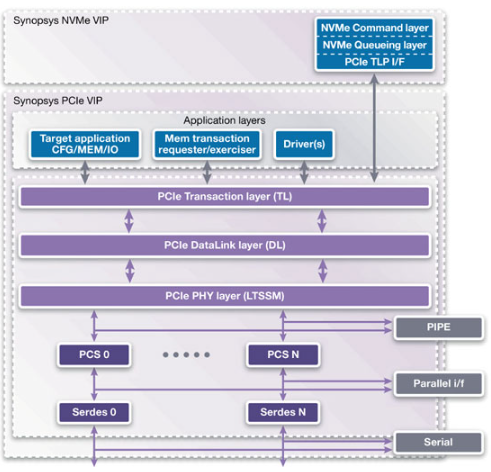

自规范最初构思以来,适用于 PCIe 5.0 的 Synopsys VIP 和源代码测试套件已被从事下一代云、数据中心、5G 和 HPC 设计的行业领导者广泛采用。VIP功能和测试套件与这些领先的PCIe Gen5采用者合作得到增强和成熟,以系统地降低每个规范草案中发布的新功能的设计实施风险(见下文)。

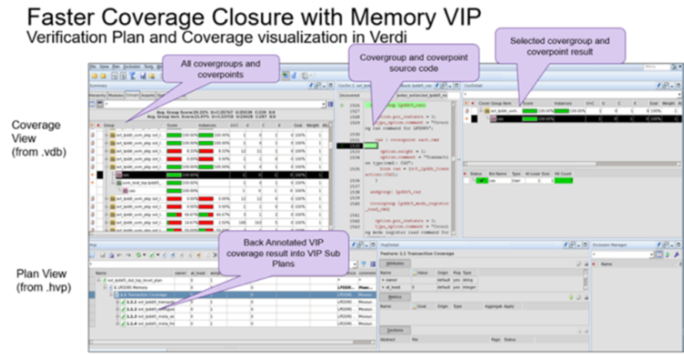

Synopsys VIP 通过其原生 SV/UVM 实施以及与 Synopsys VCS 和 Verdi Protocol Analyzer 的原生集成,提高了性能和验证效率。Synopsys VIP 提供内置功能覆盖范围和源代码第 5 代测试套件,以加快验证收敛并实现一次性质量设计的流片。

审核编辑:郭婷

-

定时器

+关注

关注

23文章

3246浏览量

114739 -

数据中心

+关注

关注

16文章

4764浏览量

72100 -

人工智能

+关注

关注

1791文章

47208浏览量

238287

发布评论请先 登录

相关推荐

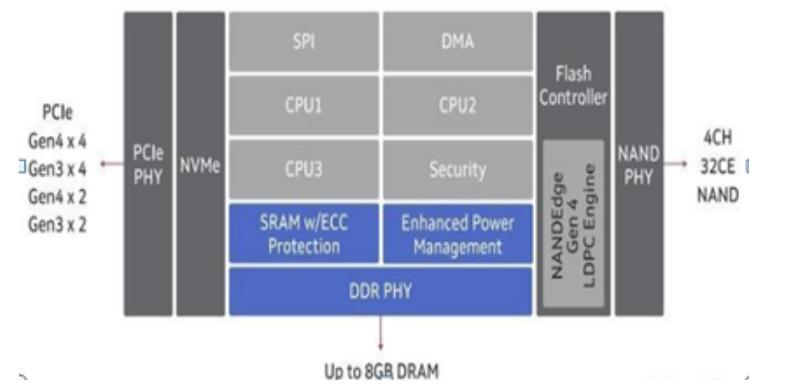

硬盘开启PCIe 5.0时代

Synopsys为更快速的SoC验证推出下一代验证IP

基于FPGA的PCIe总线接口的DMA控制器的实现并进行仿真验证

PCIe 5.0时代正式拉开序幕

PCIe 5.0对互联芯片的性能验证要求

什么是 PCIe 5.0? PCIe 5.0规范以及挑战

microchip全新的PCIe 5.0交换芯片怎么样

Cadence推出新一代CXL VIP和系统VIP工具

覆盖模型 – 填补内存VIP的漏洞

什么是PCIe?PCIe有什么用途?PCIe 5.0有何不同?

新思科技PCIe 7.0验证IP(VIP)的特性

使用Synopsys VIP签署PCIe 5.0验证

使用Synopsys VIP签署PCIe 5.0验证

评论