本文分别对quartus和vivado防止信号被优化的方法进行介绍。

为什么要防止信号被优化

在FPGA开发调试阶段,经常遇到这样的情况,需要临时添加信号,观察信号变化,用来定位代码中存在的问题,很多时候这些临时添加的信号会被综合工具优化掉,为了防止这种情况的发生,可以使用添加虚拟引脚(quartus)和代码中添加属性(vivado)。

下面分别对两种方法进行说明,在原有代码中加入如下代码,观察cnt信号是否被优化,能否通过逻辑分析仪进行观测。

reg [3:0] cnt;

always@(posedge clk,negedge locked)

begin

if(!locked)

cnt <= 4'd0;

else

cnt <= cnt + 1'b1;

end

Quartus中如何设置虚拟引脚

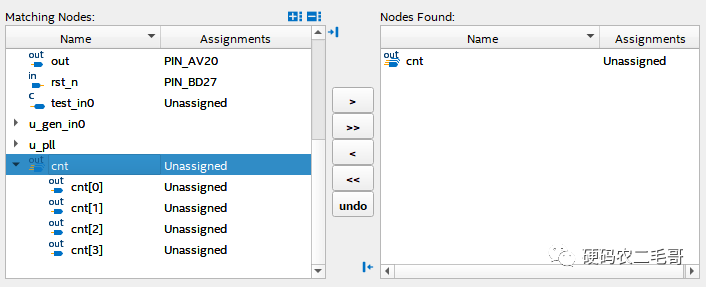

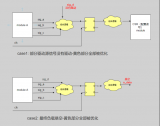

在quartus中加入上述代码后,将cnt信号设置成输出引脚。 下面将cnt信号设置为虚拟引脚。

方法1:

在qsf文件中添加如下内容:

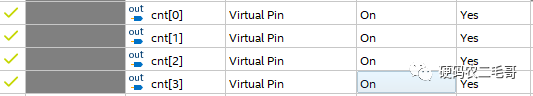

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[0]

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[1]

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[2]

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[3]

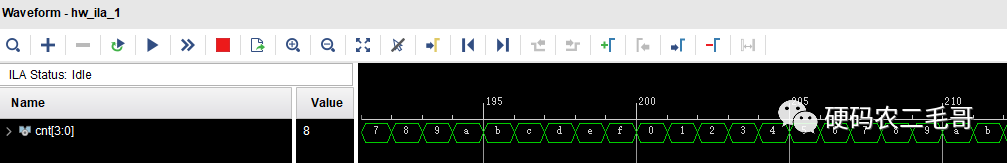

编译后,添加signal tap,cnt信号可以添加,说明没有被优化。

方法2:

将cnt信号设置成输出后,打开Assignment Editor,进行如下设置。

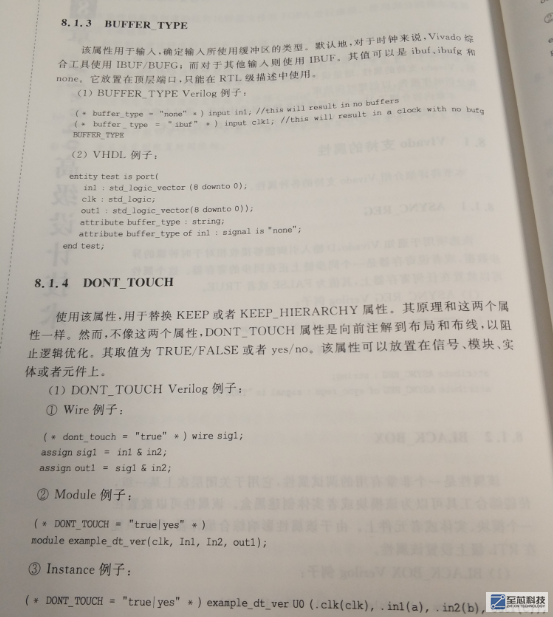

Vivado中防止信号被优化

在代码中加入(* dont_touch = "true" *) 。

(* dont_touch = "true" *) reg [3:0] cnt;

always@(posedge clk,negedge locked)

begin

if(!locked)

cnt <= 4'd0;

else

cnt <= cnt + 1'b1;

end

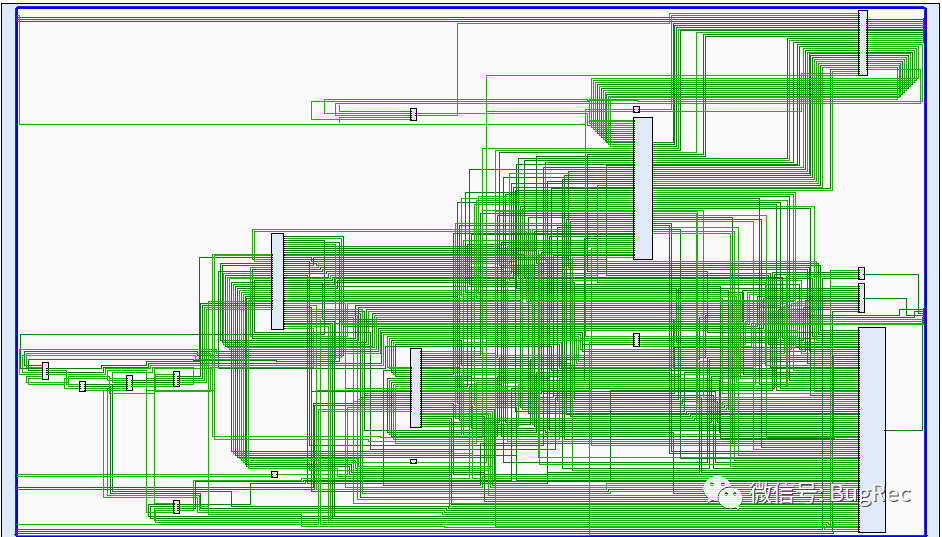

重新编译后,使用ila观测cnt,ila中有信号,证明信号没有被优化。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1629文章

21729浏览量

603017 -

信号

+关注

关注

11文章

2790浏览量

76731 -

引脚

+关注

关注

16文章

1194浏览量

50414 -

quartus

+关注

关注

16文章

171浏览量

74623 -

Vivado

+关注

关注

19文章

812浏览量

66473

发布评论请先 登录

相关推荐

FPGA中的I_O时序优化设计

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种

发表于 08-12 11:57

今日说“法”:如何防止reg、wire型信号在使用逻辑分析仪时被优化

)对于reg型信号,为了防止Altera自带综合器将其优化掉,可以添加noprune属性。这样就可以防止某些寄存器信号

发表于 05-16 17:48

如何有效防止FPGA设计被克隆?

如何有效防止FPGA设计被克隆?

据估计,目前盛行的假冒电子产品已经占到整个市场份额的10%,这一数据得到了美国反灰色市场和反假冒联盟(AGMA)的支持。AGMA是由惠普

发表于 01-04 15:32

•1402次阅读

防止Wi-Fi信号被截获的墙纸(英国开发)

防止Wi-Fi信号被截获的墙纸(英国开发)

近日英国一家公司开发出了一种特殊的墙纸,可以有效的防止 Wi-Fi网络信号

发表于 01-14 17:05

•1489次阅读

FPGA信号处理算法设计、实现以及优化(南京)

利用FPGA实现信号处理算法是一个难度颇高的应用,不仅涉及到对信号处理算法、FPGA芯片和开发工具的学习,还意味着要改变传统利用软件在DSP上实现算法的习惯,从面向硬件实现的算法设计、

发表于 12-26 17:26

•12次下载

信号管脚任务可进行多个FPGA的I/O优化

信号销任务之间可以自动优化PCB上的多个fpga同时尊重pin-specific规则和约束。减少路由层,减少跨界车和整体跟踪PCB上的长度,并减少信号完整性问题较高的毕业率和更短的

PCB设计中的高速信号传输优化技巧

在现代电子设计中,高速信号的传输已成为不可避免的需求。高速信号传输的成功与否,直接影响整个电子系统的性能和稳定性。因此,PCB设计中的高速信号

FPGA在线调试信号被优化原因分析及防止优化方法总结

而我们常常会使用代码中的信号名来抓取信号,后期布局布线阶段,无法找到对应的电路信号,可能会导致无法抓取信号或者布局布线失败。

发表于 06-20 10:32

•2206次阅读

FPGA设计中如何防止信号被优化

FPGA设计中如何防止信号被优化

评论