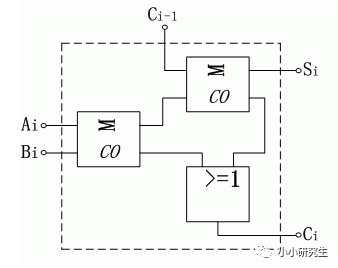

全加器可看作两个半加器和一个或门组成。

首先半加器是A+B构成了{C,S}。由于全加器多了一个低位的进位,就是将{C,S}再加上Ci-1。此时再使用一个半加器将S与Ci-1相加,结果的低位就是全加器的低位Si。全加器的高位Ci来自于两个半加器的高位,如果有一个高位为1,结果就为1。

设计规划

本例中将采用3个按键作为输入in1,in2和进位信号cin,并采用两个LED灯作为信号输出count和sum。根据上一节中全加器真值表,可以画出波形图:

编写代码

module full_adder

(

input wire in1 ,

input wire in2 ,

input wire cin ,

output wire sum ,

output wire cout

);

//wire define

wire h0_sum ;

wire h0_cout;

wire h1_cout;

//------------------------half_adder_inst0------------------------

half_adder half_adder_inst0

(

.in1 (in1 ),

.in2 (in2 ),

.sum (h0_sum ),

.cout (h0_cout)

);

//------------------------half_adder_inst1------------------------

half_adder half_adder_inst1

(

.in1 (h0_sum ),

.in2 (cin ),

.sum (sum ),

.cout (h1_cout)

);

assign cout = h0_cout|h1_cout;

endmodule

还记得FPGA从入门到精通(一)中的移位寄存器的实例化练习吗?以module模块名(输入,输出)开头,以endmodule结尾。

上一节中已经封装好了half_adder函数,内部的逻辑就不用再次写了,只需要将外部端口和full_adder的端口对应好就可以直接调用。这就是verilog的方便之处,否则完成这个程序,需要将半加器的代码写两次。

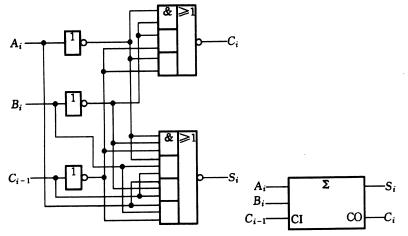

再上面的全加器结构图中可以看到端口的对应,其中除了全加器的5个端口外,还需要引入三根连线。需要定义wire变量h0_count,h1_count和h0_sum。

下面完成两次实例化,上一节中的半加器有in1,in2,cout,sum四个端口,第一个半加器分别对应着全加器的输入端口in1,in2,h0_count,h0_sum,第二个半加器分别对应着上一个半加器的结果的低位h0_sum和低位进位cin,h1_count1,全加器的结果的低位sum。全加器的结果的高位count是h0_count和h1_count的或。

现在将.v文件综合一定会报错,因为还没有将half_adder模块添加进来。所以调用时找不到半加器的函数。因此需要将half_adder.v复制到文件夹中并添加到Files中:

看RTL视图,两个half_adder模块是可以展开的:

编写testbench

`timescale 1ns/1ns

module tb_full_adder();

reg in1;

reg in2;

reg cin;

wire sum ;

wire cout;

initial begin

in1 <= 1'b0;

in2 <= 1'b0;

cin <= 1'b0;

end

always #10 in1 <= {$random} % 2;

always #10 in2 <= {$random} % 2;

always #10 cin <= {$random} % 2;

//------------------------------------------------------------

initial begin

$timeformat(-9, 0, "ns", 6);

$monitor("@time %t:in1=%b in2=%b cin=%b sum=%b cout=%b",$time,in1,in2,cin,sum,cout);

end

//------------------------------------------------------------

//---------------full_adder_inst------------------

full_adder full_adder_inst(

.in1 (in1),

.in2 (in2),

.cin (cin),

.sum (sum),

.cout (cout)

);

endmodule

这里testbench依然是先声明变量,其中输入是reg类型,输出是wire类型。初始化令变量都为0,延时10ns给输入随机赋值0或1,然后实例化将tb_full_adder模块和full_adder模块端口进行连接,就可以观察波形。

需要注意的是!!!在本例中引入了打印模块,可以直观看到随机输入对应输出的真值表。

$timeformat(units_number, precision_number, suffix_string, minimum_field_wdith);

timefomat的语法:

第一个参数units_number表示打印的时间值的单位,取0 到-15 之间的整数值:0 表示秒,-3 表示毫秒,-6 表示微秒,-9 表示纳秒, -12 表示皮秒, -15 表示飞秒

第二个参数precision_number表示打印时间值时,小数点后保留的位数。

第三个参数suffix_string在时间值后面打印时间单位。其默认值为空字符串,如果用ns作为单位可以打印ns。

第四个参数MinFieldWidth 是时间值与单位字符串的最小长度,不足这个长度,则在字符串之前补空格。其默认值为20。

monitor的语法:

$monitor (“format_string”, parameter1, parameter2, … );

当在monitor调用时对多个变量进行监控,当monitor监控的变量中任何一个发生变化时,将会打印出当前仿真时刻的值;如果$monitor监控的所有变量在某一时刻均不改变,将不会打印任何信息。本例中会打印出时间和5个端口值。

对比波形

当端口多了之后,看波形相对不直观了,这里可以通过观察我们刚才打印的数据进行判断。通过View-transcript可以观察transcript窗口:

表格的方式相对直观多了,且输出和预期一致。

分配管脚

全编译后分配引脚,这里的按键和LED灯管脚我们已经非常熟悉了。在location这一栏分配引脚,不要和fitterlocation弄混了。

现在cin,in1,in2对应S0,S1,S2,cout对应LED0,sum对应LED1。那么cin,in1,in2按下去表示为0,点亮的LED表示对应为输出为低电平。都不按下去时,应该都熄灭,按下去一个时,LED0亮,按下两个时,LED1亮,按下三个时,两个LED同时亮。

全编译后上板验证

一个都不按下时,都不亮

按下一个时,LED0亮

按下两个时,LED1亮

全部按下时,两个都亮

组合逻辑电路的实例就结束了,后面是简单的时序逻辑电路实例。

-

FPGA

+关注

关注

1629文章

21729浏览量

603051 -

led灯

+关注

关注

22文章

1592浏览量

107957 -

移位寄存器

+关注

关注

3文章

258浏览量

22270 -

全加器

+关注

关注

10文章

62浏览量

28497 -

半加器

+关注

关注

1文章

29浏览量

8791

发布评论请先 登录

相关推荐

Altium如何创建层次化的原理图形式

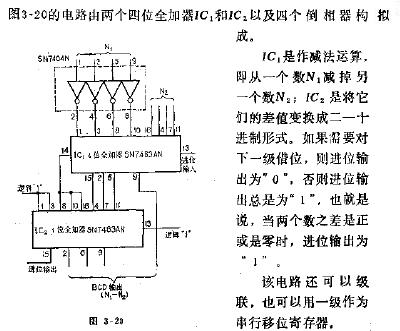

什么是8位全加器和8为带超前进位的全加器?

一种基于单电子晶体管的全加器电路设计

监控系统设备构成的分层次结构详析

全加器是什么?全加器和半加器的区别?

全加器的真值表

层次化设计构成全加器

层次化设计构成全加器

评论