PCIE Zero-Length read

1、Zero-Length Write

PCIe协议提出了zero-length的读写操作,并且做了如下说明

Zero-Length Write的含义

A Memory Write Request of 1 DW with no bytes enabled, 即Memory Write 类型tlp中只有1DW的data,且length字段为1,并且tlp header中的First DW BE[3:0] 和Last DW BE[3:0]均为0。

A Memory Write Request of 1 DW with “zero-length Write,”

Zero-Length Write的作用

Zero-Length Write has no effect at the Completer unless otherwise specified. 正常情况下Zero-Length Write不会对完成者造成任何影响,除非特别指定。例如:正常情况下,一颗芯片中的PCIe作为endpoint,收到Zero-Length Write时,此Zero-Length Write不会改写当前tlp中addr对应的寄存器(or RAM)的数值,也不会产生对应地址的写脉冲,更不会应该此写操作造成芯片功能的变化

A Memory Write 通常在特定的协议中去使用,已达到额外的效果,例如LN protocol.(没深入看)

2、Zero-Length Read

PCIe协议提出了zero-length的读操作,并且做了如下说明

Zero-Length Read的含义

A Memory Read Request of 1 DW with no bytes enabled。即Memory Read 类型tlp中且length字段为1,并且tlp header中的First DW BE[3:0] 和Last DW BE[3:0]均为0。

Zero-Length Write的作用

协议原文描述如下:

Zero-Length Read may be used by devices as a type of flush Request. For a Requester, the flush semantic allows a device to ensure that previously issued Posted Writes have been completed at their PCI Express destination. To be effective in all cases, the address for the zero-length Read must target the same device as the Posted Writes that are being flushed. One recommended approach is using the same address as one of the Posted Writes being flushed.

即:

Zero-Length Read 通常作为一种刷新操作,用于确保之前发起的Posted Writes已经被completer完成了。假设master在T0时刻已经发起mem_write(addrA),T1时刻发起zero_mem_rd(addA),T3时刻master收到对应的cpld。此时在T3时刻,master就知道了mem_write(addrA)已经被slave正确执行了。

对Zero-Length Write的要求:

If a Read Request of 1 DW specifies that no bytes are enabled to be read (First DW BE[3:0] field = 0000b), the corresponding Completion must specify a Length of 1 DW, and include a data payload of 1 DW.The contents of the data payload within the Completion packet is unspecified and may be any value。即对应cpl的长度必须指定为1DW,且必须包含1DW的data payload,并且data的数值没有要求,可以是任意值。

3、Zero-Length Read相对于正常读操作有什么优势呢?

假设目标地址的读写操作均会触发芯片内部不同功能的启动,而Zero-Length Read实际不要求真正去执行一次memory read操作。同样都能确保之前Posted Writes已经被执行,但是真实的读操作可能会改变芯片功能状态,而Zero-Length Read不会,因此Zero-Length Read更有优势。

谈谈bus master en

Bus master en信号

Type0的function:控制function发起Memory and I/O Read/Write Requests

1.Bus Master Enable为0,不允许function发起Memory and I/O Read/Write Requests

2.PF的Bus Master Enable 位于PF配置空间的Command Register的bit2,仅仅控制PF自身的请求,不会控制所属VF的请求

3.VF的Bus Master Enable,位于VF配置空间的Command Register的bit2,仅仅控制VF自身的请求

Type1的function:控制function向Upstream方向转发Memory and I/O Read/Write Requests

1.Switch upstream port的Bus Master Enable为0,

(1)会将downstream side收到的Memory and I/O Read/Write Requests当做UR处理

(2)Switch upstream port自身不允许向upstream 方向发出Memory and I/O Read/Write Requests

ECRC 与 credit 信用量

1、ECRC 是不算在信用量范围内的

从PCIe协议上可以看出,信用量仅仅包含三类:CPL credit/Post credit/non-post credit,其中每种包含data credit和header credit。

ECRC 是额外添加的校验字段,在TLP内是1DW,即4byte,不属于data payload,也不属于header字段。因此ECRC不在信用量的考量范围内。

2、Buffer size的注意事项

支持ECRC check功能的PCIE 在设计rx buffer时,需要考虑到当所有收到的TLP都带ECRC字段时,buffer是否会溢出。

审核编辑 :李倩

-

芯片

+关注

关注

455文章

50711浏览量

423077 -

寄存器

+关注

关注

31文章

5334浏览量

120221 -

PCIe

+关注

关注

15文章

1234浏览量

82572

原文标题:PCIE知识点:谈谈bus master en等

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

计算机组成原理考研知识点归纳

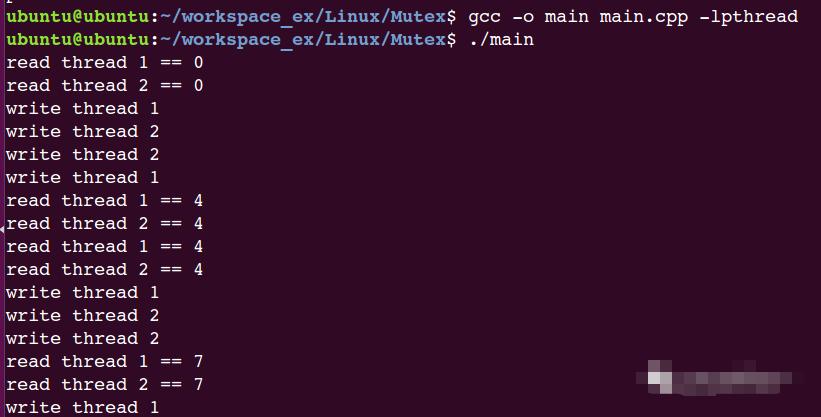

Linux中多线程编程的知识点

PCIE知识点:谈谈bus master en等

PCIE知识点:谈谈bus master en等

评论