1串扰的基本信息

串扰是指有害信号从一个网络转移到相邻网络。任何一对网络之间都存在串扰。通常把噪声源所在网络称为动态网络或攻击网络。把受影响的网络称为静态网络或者受害网络。

串扰不仅仅出现在信号路径,在返回路径上也可能出现。从动态网络上耦合到静态网络上的电压与静态网络上原有的电压完全无关。如果静态线上本身的电压为3.3V,从动态线耦合过来的噪声是150mV,那么静态线上的电压总合是3.45V。

如果有两条动态线都在干扰同一条静态线,那么静态线上的噪声是两条动态线噪声总合。

静态线上的噪声和其他信号一样,在静态线上能感受到特性阻抗的变换。噪声在静态线阻抗变化点,也会发生反射和失真。因此串扰的影响不仅仅体现在噪声信号幅度上,也会体现在噪声信号的失真。

2串扰的噪声源

当信号沿着传输线传播时,信号路径和返回路径之间都会有电场和磁场产生,由此带来电力线和磁力线。它充斥在信号路径和返回路径之间的空间中。把这些延伸出去的场称为边缘场。距离信号路径和返回路径越远的地方,边缘场越少。

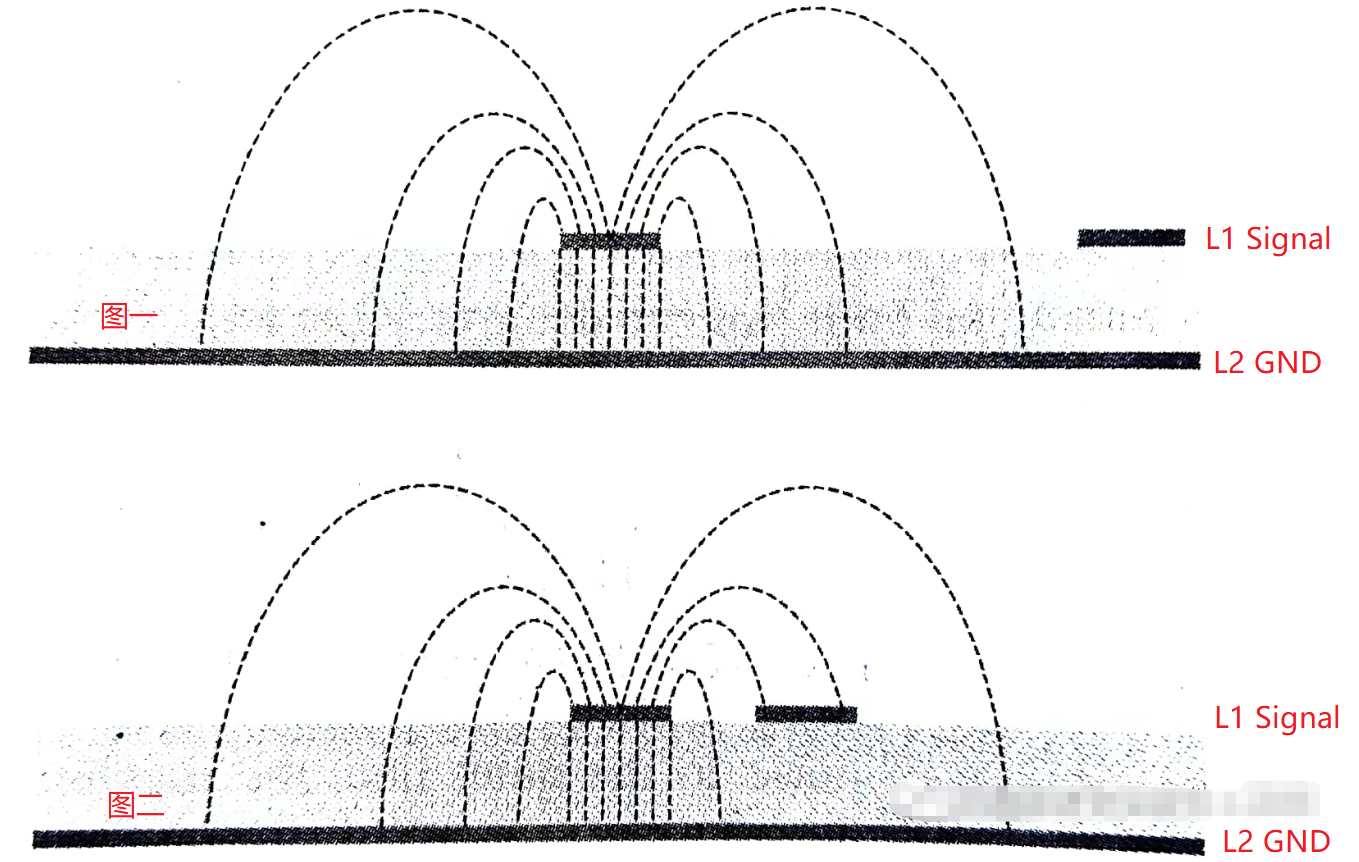

如下图的图一,右边的静态线远离中间的动态线,不在动态线的边缘场范围内,基本不受动态线干扰。下图的图二,右边的静态线靠近动态线,受到动态线干扰。

当动态线上信号的电压和电流发生变化时,变化的电流会造成变化的电场和磁场。由此在静态线上产生电流和电压噪声。

边缘场是串扰的根本原因。减小串扰的主要办法就是增加动态线和静态线之间的距离,使它们之间的边缘场影响最小。一个PCB上,任何两个网络之间总会有边缘场产生的容性耦合和感性耦合,称为互容和互感。增大网络之间的距离,就会减小互容和互感。

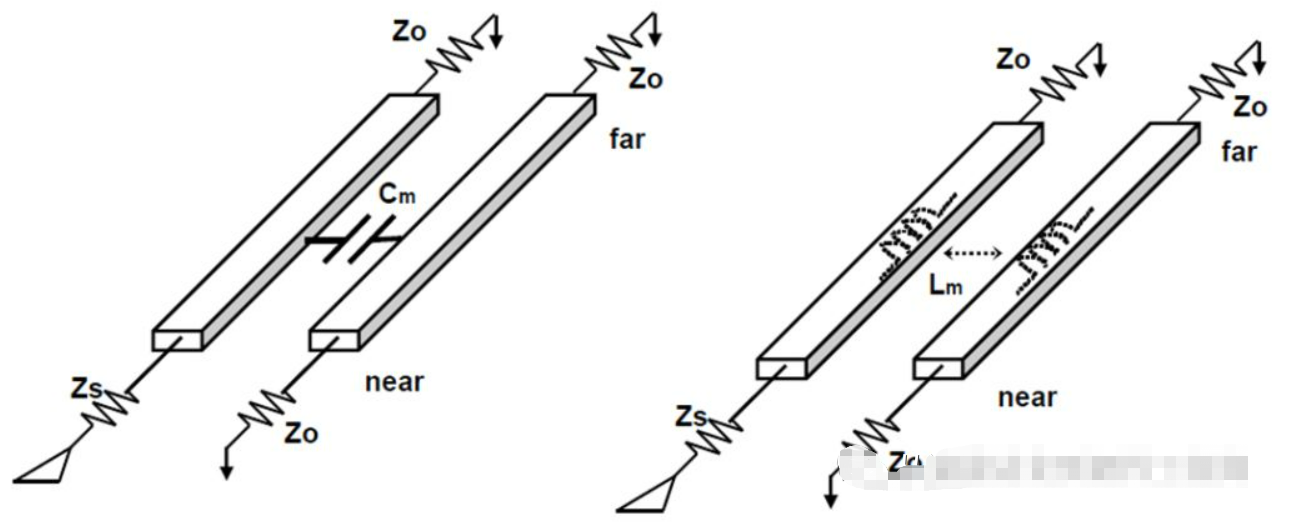

3近端串扰和远端串扰

信号从源端输出,经过动态传输线到达负载端。在静态传输线上可以看到串扰过来的噪声。而且在静态传输线的两端看到的噪声不同。把靠近源端的静态线端称为“近端”,把远离源端的静态线称为“远端”。近端是信号传输方向的相反方向,远端是信号传输前进的方向。

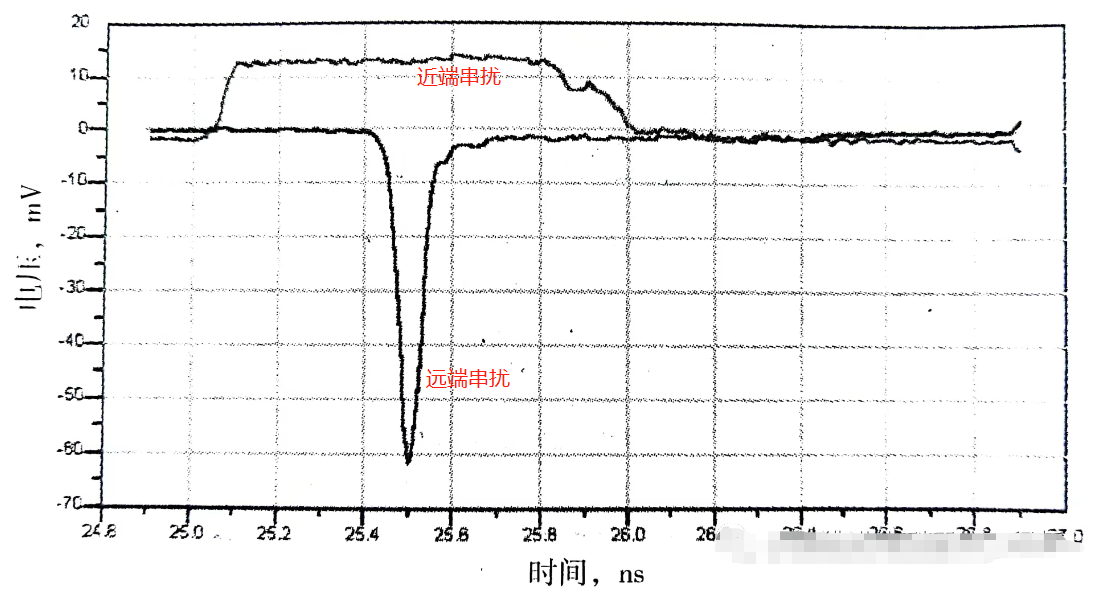

不考虑反射等影响,仅仅只是看串扰的波形。

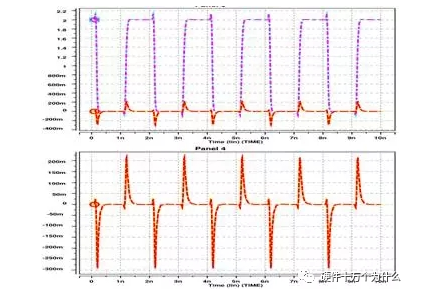

近端噪声波形:快速上升到固定值,并且保持一定时间,然后再下降。保持时间等于动态线和静态线耦合长度带来的时延的两倍。如果传输线的端接发生变化,近端噪声值也会发生变化。

远端噪声波形:它在信号传输一段时间之后才会观察到。它持续的时间很短,看起来是一个脉冲。脉冲宽度大约等于信号上升时间。

通过增大动态线和静态线之间的距离,可以减小近端噪声和远端噪声。另外减小耦合长度、使信号上升时间变缓慢,也可以降低远端噪声。

4描述串扰的两种方法

方法一:将动态线和静态线看做一对差分线。用奇模阻抗、偶模阻抗、奇模时延、偶模时延,这四组参数来描述传输线的耦合和串扰。

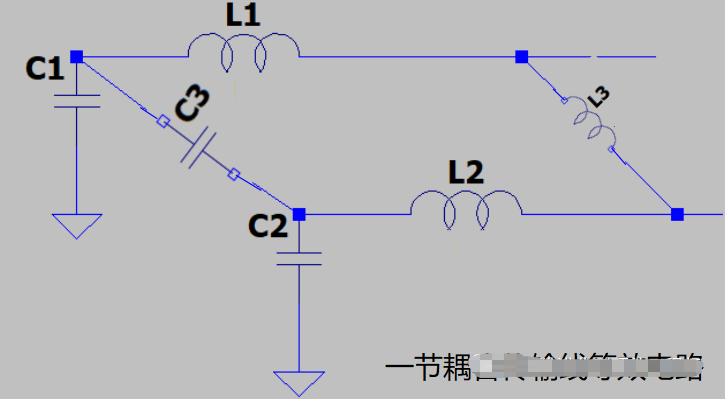

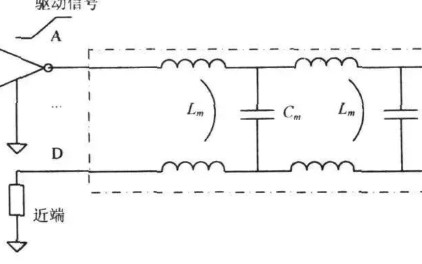

方法二:用n节LC模型来描述传输线的耦合和串扰。下图是其中一节的LC模型。用n节组合起来得到整个动态线和静态线的模型。LC模型的节数越多,近似程度越高。

针对每一节LC模型,单条传输线用单位长度电容CL(C1、C2)和单位长度回路电感Li(L1、L2)描述。两条线之间的耦合用单位长度互容Cm(C3)和单位长度互感Lm(L3)描述。

当有两条以上的传输线时,每条传输线之间都有寄生参数存在,此模型需要扩展,会变得更复杂。

5传输线之间寄生电容

5.1

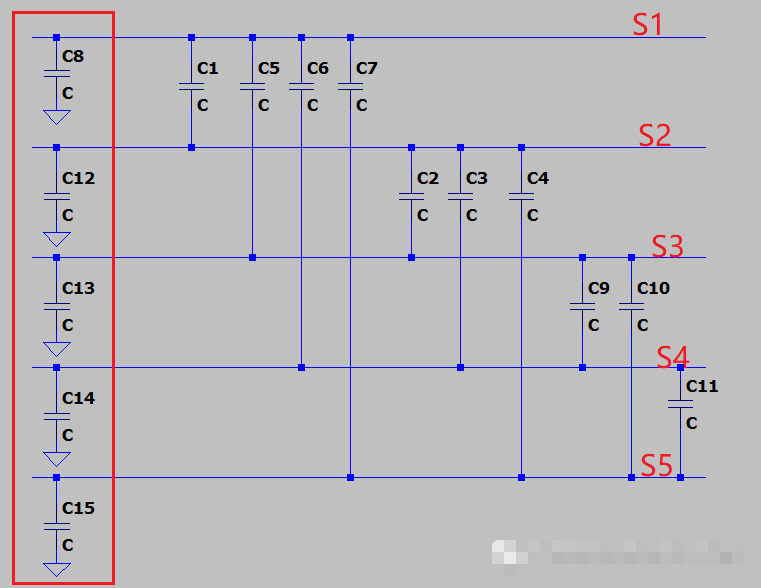

下图是以多条传输线为例,分析5条传输线(S1~S5)之间的寄生电容值。因为对于高速信号的dV/dt,寄生电容大小决定了导线之间的容性耦合电流大小(噪声电流)。

在本例中,5条线都是50Ω微带线,每条传输线宽度W是5mil,传输线和传输线之间的距离也是5mil,即两传输线中心之间的距离是2W。这些信号的返回路径都是GND。

当出现多于两条传输线的情况时,每条传输线之间都有寄生电容存在,只不过大小不同。红色方框中的电容表示每条传输线和参考平面之间的寄生电容。其他电容是各个传输线之间的寄生电容。例如C1是S1和S2之间的寄生电容,C4是S2和S5之间的寄生电容。

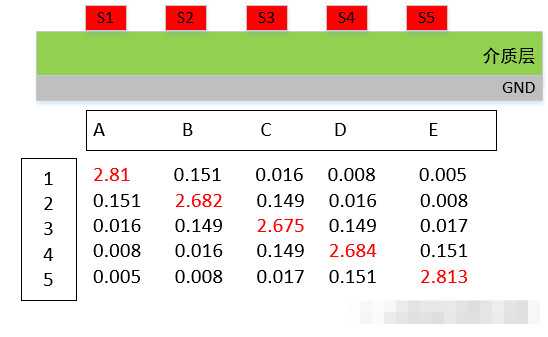

下图信号线下方的数字表示每条传输线和参考平面之间的单位长度寄生电容、以及传输线和传输线之间的单位长度寄生电容,单位是pF/in。例如A1=2.81pF/in,是S1和参考平面之间的单位长度寄生电容。B1=0.151pF/in,是S1和S2之间的单位长度寄生电容。C1=0.016pF/in,是S1和S3之间的单位长度寄生电容,依次类推。

通过以上的数据可以看到,①传输线和参考平面之间的耦合度要比传输线和传输线之间的耦合度更紧密。②相邻传输线之间的耦合度比相隔传输线之间的耦合度要紧密。例如S1和S2之间耦合电容接近是S1和S3之间耦合电容的10倍。这也是为什么高速信号PCB设计时,要求传输线和传输线之间至少保持3W间距的原因。

5.2

需要注意的是,对一条传输线而言,它和参考平面之间的寄生电容会受到它和相邻传输线距离的影响。例如当拉进S1和S2的距离时,S1对参考平面的寄生电容会减小一些,因为有一部分本来进入参考平面的电力线将分流到S2上去。

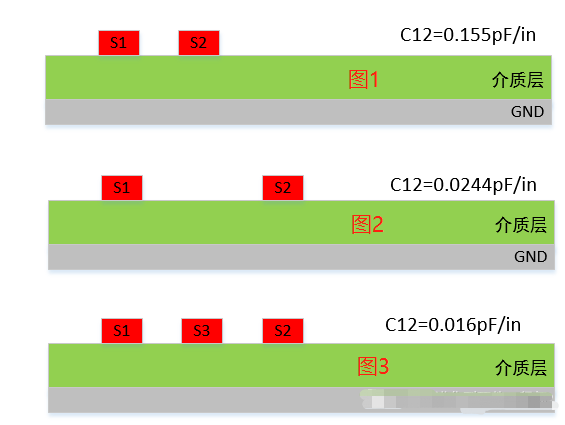

另一方面在两条传输线之间插入第三条传输线,第三条传输线将分担一些电力线,降低之前两条传输线之间的耦合度。这也是我们在做PCB设计时,用GND线隔离敏感信号的原因。如下图是2条传输线S1和S2,它们线宽是5mil。图1线间距是5mil(边到边)。图2线间距是15mil(边到边)。图3是增加一条传输线S3,各线之间间距是5mil(边到边)。C12是S1和S2之间的单位长度寄生电容值。可以看到拉大S1和S1的距离会明显降低寄生电容,插入一条新的传输线(通常是GND),寄生电容会进一步降低。

-

耦合

+关注

关注

13文章

582浏览量

100867 -

信号完整性

+关注

关注

68文章

1406浏览量

95460 -

寄生电容

+关注

关注

1文章

292浏览量

19228 -

传输线

+关注

关注

0文章

376浏览量

24029 -

串扰

+关注

关注

4文章

189浏览量

26943

发布评论请先 登录

相关推荐

常见信号完整性的问题之PCB设计串扰的原因与Altium Designer中的串扰消除威廉希尔官方网站

信号完整性之串扰(一)

信号完整性之串扰(一)

评论