【CMOS逻辑IC基础知识】—解密组合逻辑背后的强大用途!(上)

在前面的芝识课堂中,我们跟大家简单介绍了逻辑IC的基本知识和分类,并且特别提到CMOS逻辑IC因为成本、系统复杂度和功耗的平衡性很好,因此得到了最广泛应用,同时也和大家一起详细了解了CMOS逻辑IC的基本操作。逻辑IC作为一种对一个或多个数字输入信号执行基本逻辑运算以产生数字输出信号的半导体器件,其应用也是非常丰富的,今天就来和芝子一起了解一下吧。

首先我们要明确的是CMOS逻辑IC大致包括两种逻辑,即组合逻辑和时序逻辑。其中组合逻辑是输出仅为当前输入的纯函数逻辑电路类型,主要包括反相器、缓冲器、双向总线缓冲器、施密特触发器装置、解码器、多路复用器、interwetten与威廉的赔率体系 多路复用器/多路分解器、模拟开关等;时序逻辑是一种其输出取决于先前输入值的顺序,并由当前输入(如控制信号触发器、锁存器、计数器、移位寄存器等)控制的逻辑电路类型。组合逻辑电路与时序逻辑电路的区别体现在输入输出关系、有无存储(记忆)单元、结构特点上。

首先我们以几个简单的电路部分为例,来介绍组合逻辑电路的基本情况。

1 反相器

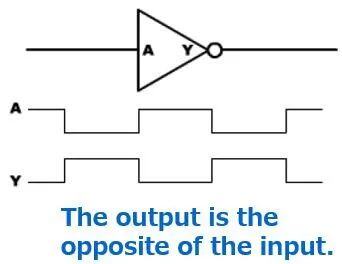

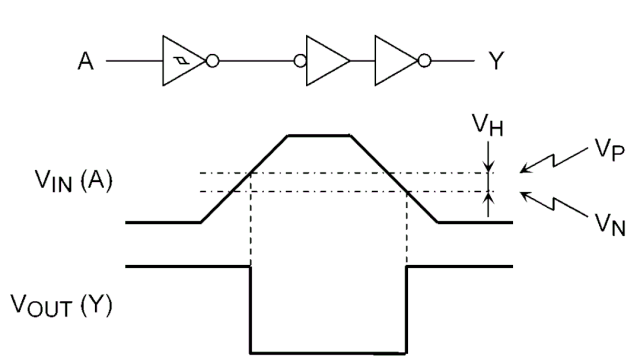

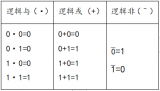

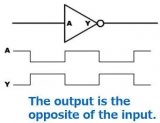

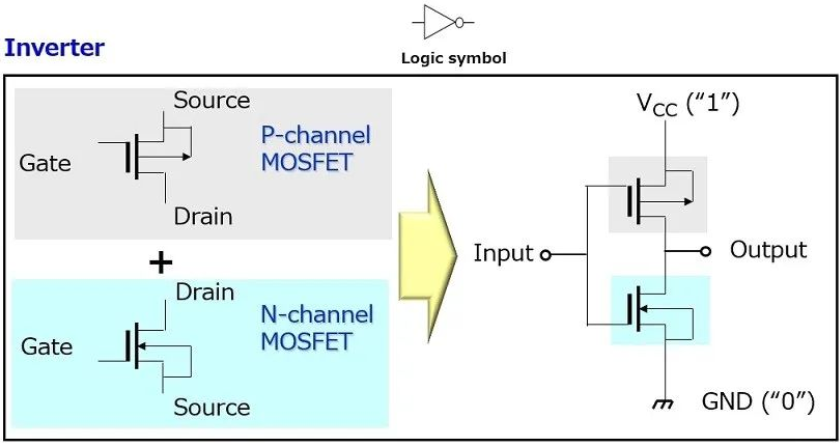

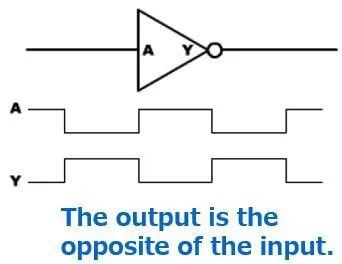

组合逻辑应用中比较常见的是反相器(以74VHC04为例),是一种输出(Y)与输入(A)相反的逻辑门,如图1所示。

图1 逆变器的操作

2 缓冲器

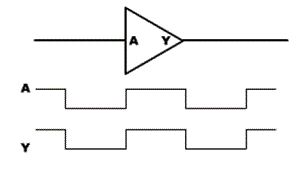

缓冲器(例如74VHC244),缓冲器增加驱动能力以增加可连接的信号线的数量,并执行波形整形。缓冲区不执行逻辑操作,示意图如图2。

图2 缓冲器的操作

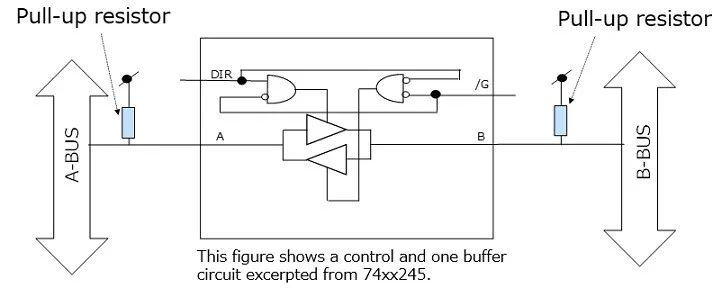

3 双向总线缓冲器(收发器)

双向总线缓冲器(收发器),比如74VHC245。双向总线缓冲器(收发器)是一种其I/O引脚可配置为输入和输出以接收和发送数据的逻辑电路。由于收发器允许通过控制信号(DIR)更改信号方向,所以它沿着总线传输,双向传输数据。图3显示了收发器的应用示例。双向使用总线信号时,将总线输入和总线输出都通过上拉电阻连接到VCC或GND,以防止在控制信号(DIR)切换信号时输入信号变为开路(未定义)。切换信号时请注意不要将输出与总线输出短路。

图3 双向总线缓冲器的应用示例

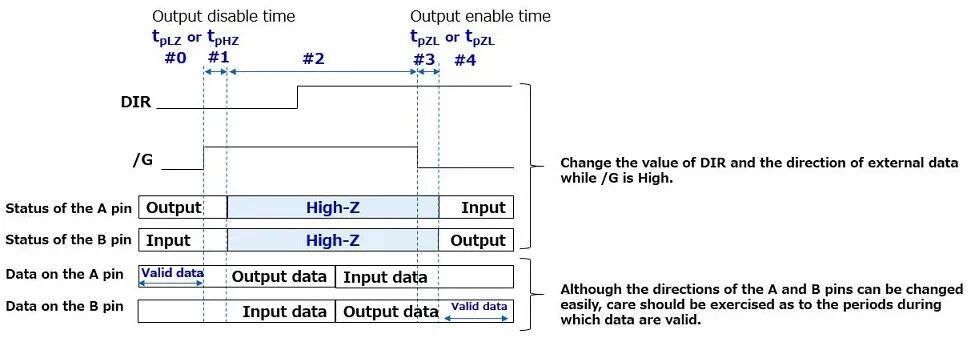

我们来看一下图3这个系统的逻辑情况,通过在/G为高电平时更改DIR的值,可以轻松更改A和B引脚的方向。/G为高电平时,更改DIR的值和外部数据的方向。在周期#0,数据从B传输到A。在周期#1,A引脚处于高Z状态。因此,输出数据无效。在周期#2,更改DIR的值和外部数据的方向。在周期#3,启用A和B引脚。然后,输出数据在周期#4开始时保持稳定。在周期#4,数据从A传输到B。详细输入和输出逻辑关系如图4所示。

图4 双向总线缓冲器的逻辑示意

4 施密特触发器

我们再看一个特别的示例,施密特触发装置(以VHC14为例)。施密特触发装置在两个输入阈值电压之间有一个磁滞带。图5显示了具有输入阈值滞后的施密特反相器的输入和输出波形。对于具有磁滞的IC,正向阈值电压(VP)不同于负向阈值电压(VN)。对于缓慢上升或下降的输入,输入阈值滞后(VH)有助于稳定输出。即使存在输入噪声或电源或噪声引起的接地反弹的情况下,IC也不会产生错误输出,除非噪声或反弹超过磁滞宽度。

图5 施密特反相器的输入和输出波形

5 解码器

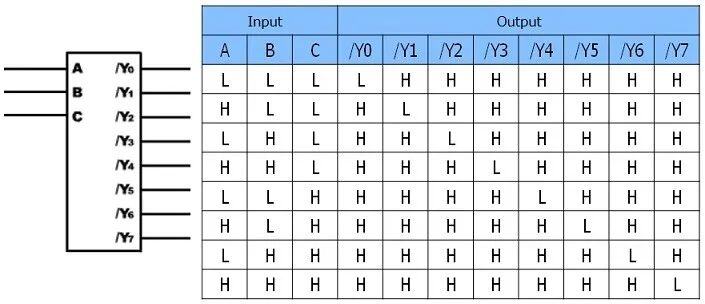

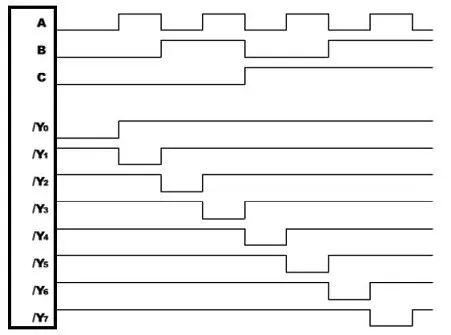

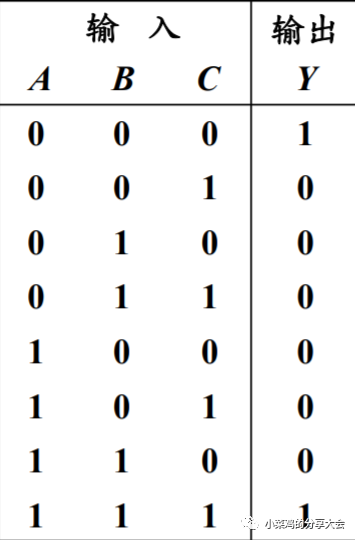

解码器也是一种典型的组合逻辑电路,我们以VHC138为例进行逻辑解读。解码器将N个编码输入的二进制信息转换为最多2N个独特输出。它通常用于增加端口数量和生成芯片选择信号。图6显示了3对8解码器(即具有三个输入和八个输出的解码器)的逻辑符号、真值表和时序图。

图6 3对8解码器的逻辑符号和真值表以及时序图

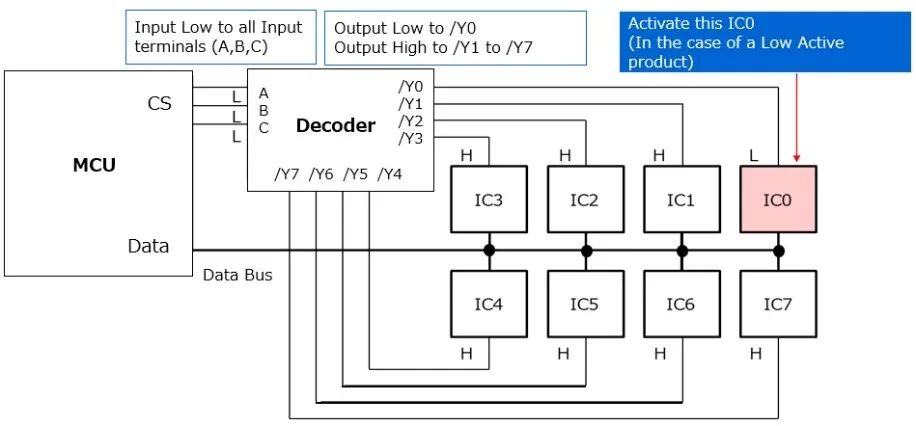

图7则显示如何使用3对8解码器从三个输入(A、B和C)生成八个芯片选择信号。当A、B和C都为低电平时,只有/Y0输出提供逻辑低电平,所以选择IC0。图7表明,通过三个输入的组合,可以从最多八个芯片中选择任意芯片。

图7 3至8解码器的时序图

今天的芝识课堂,我们带大家了解了几种典型电路单元的对应逻辑关系,在下面的芝识课堂中,我们将继续跟大家分享CMOS逻辑IC的基础知识,敬请期待。

审核编辑:汤梓红

-

半导体

+关注

关注

334文章

27305浏览量

218201 -

反相器

+关注

关注

6文章

311浏览量

43296 -

组合逻辑

+关注

关注

0文章

47浏览量

10038 -

逻辑IC

+关注

关注

0文章

22浏览量

6426

发布评论请先 登录

相关推荐

【雨的FPGA笔记】基础知识-------逻辑电路(2)

常见的组合逻辑电路分析

逻辑电路的基础知识

CMOS逻辑IC基础知识:系统认识CMOS逻辑IC

在Artix 7 FPGA上使用Vivado的组合逻辑与顺序逻辑

CMOS逻辑IC基础知识:解密组合逻辑背后的强大用途(上)

CMOS逻辑IC基础知识:解密组合逻辑背后的强大用途(上)

评论