现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

这里有一个前提,即假定设计师已经根据设计的大概规模和信号要求确定了目标器件范围和型号。对以下每一步都应在考虑单极信号前优先考虑差分对信号。

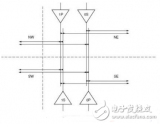

最先指配那些只能在特定引脚上工作的特殊信号,正常情况下是指串行I/O信号和全局时钟信号。其次指配大型和/或高速信号总线,特别是那些要跨越多个库或区域的信号。如果总线需要局部时钟,那么就要考虑具有更多局部时钟引脚的库或区域,并先指配局部时钟。

如果针对FPGA器件采用了多种I/O标准,那么设计师还必须先考虑将I/O信号映射到库/区。这一步需要慎重考虑,因为许多I/O标准和参考电压是不兼容的。一些I/O标准要求在特殊引脚上输入参考电压,使得这些引脚不可再用于一般用途。将高速输出和双向信号分开指配在一定程度上可避免同时开关输出噪声(SSO)问题。

第三,采用第二步中相同的基本规则指配速度较慢和约束较少的总线,但不用太多考虑SSO等问题。第四,最后完成个别信号的指配。如果只剩下少量引脚,或在第一次反复时用完了所有的引脚,可以考虑选用具有更多I/O数量的下一种器件,因为根据市场情况肯定还会临时增加某些功能,而且没有哪个设计师愿意在设计的最后阶段再做一遍指配过程吧。

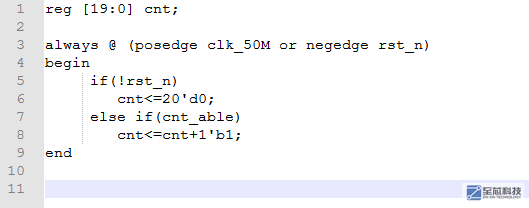

在以上每一步中,要建立含有正确信号分配和I/O标准的约束文件,以及含有I/O设计部分的HDL文件。然后再开始布局和布线,因为按从最多约束信号到最少约束信号的顺序可以更好地发现错误

审核编辑:汤梓红

-

FPGA

+关注

关注

1628文章

21708浏览量

602690 -

信号

+关注

关注

11文章

2786浏览量

76703 -

HDL

+关注

关注

8文章

327浏览量

47365 -

总线

+关注

关注

10文章

2875浏览量

88027 -

引脚

+关注

关注

16文章

1190浏览量

50365

原文标题:简谈FPGA引脚信号分配的几个原则

文章出处:【微信号:Hack电子,微信公众号:Hack电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

简谈FPGA的上电复位

FPGA管教分配需要考虑因素

浅谈如何克服FPGA I/O引脚分配挑战

图文解析如何分配FPGA管脚

勇敢的芯伴你玩转Altera FPGA连载49:PWM蜂鸣器驱动之引脚分配

FPGA引脚信号如何分配?FPGA引脚分配的几个基本原则

FPGA和USB3.0通信-FX3硬件设计简谈

简谈FPGA引脚信号分配的几个原则

简谈FPGA引脚信号分配的几个原则

评论