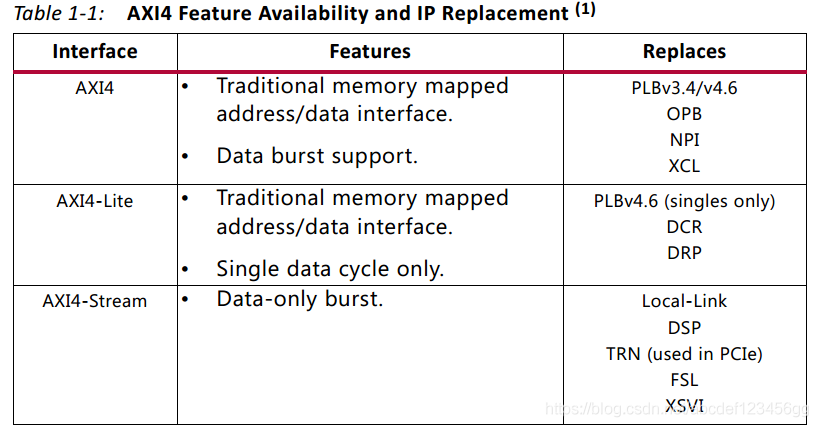

之前文章为大家介绍了AXI的协议与架构,本篇我们接着往下讲AXI的读写传输

内容概括

这次为大家讲述的内容包括:

AXI读写传输

0****1

读写传输

3.1

握手过程

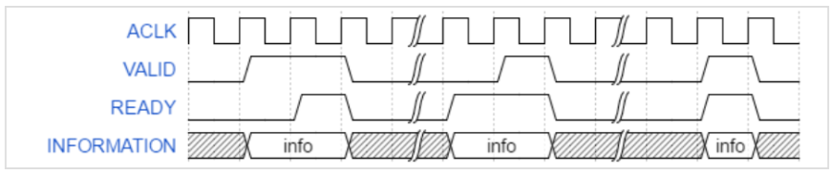

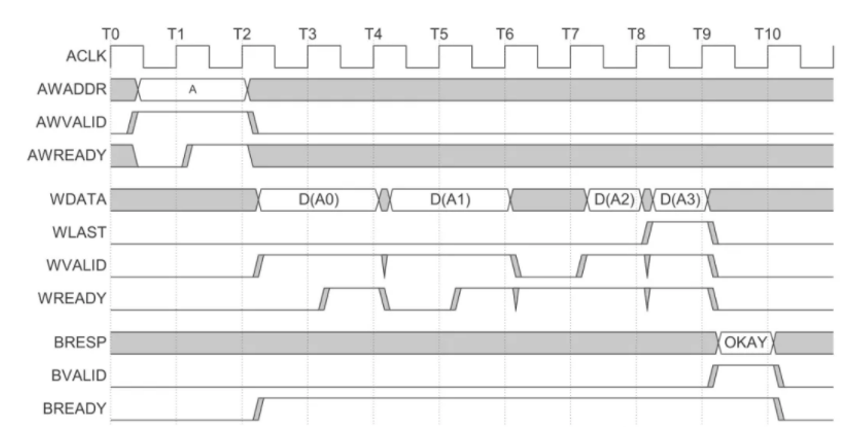

5个传输通道均使用VALID/READY信号对传输过程的地址、数据、控制信号进行握手。使用双向握手机制,传输仅仅发生在 VALID 、 READY 同时有效的时候 。

- VALID信号表示地址/数据/应答信号总线上的信号是有效的,由传输发起方控制

- READY信号表示传输接收方已经准备好接收,由传输接收方控制。

VALID和READY的先后关系具有三种情况:

- ALID先有效,等待READY有效后完成传输(VALID一旦有效后在传输完成前不可取消)。

- READY先有效,等待VALID有效后完成传输(READY可以在VALID有效前撤销)。

- VALID和READY同时有效,立刻完成传输。

此外,需要注意的是允许READY信号等待VALID信号再有效,即即使从机准备好,也可以不提供READY信号,等到主机发送VALID信号再提供READY信号。对应的VALID信号不允许等待READY信号,即不允许VALID等待READY信号拉高后再拉高,否则容易产生死锁现象。

3.2

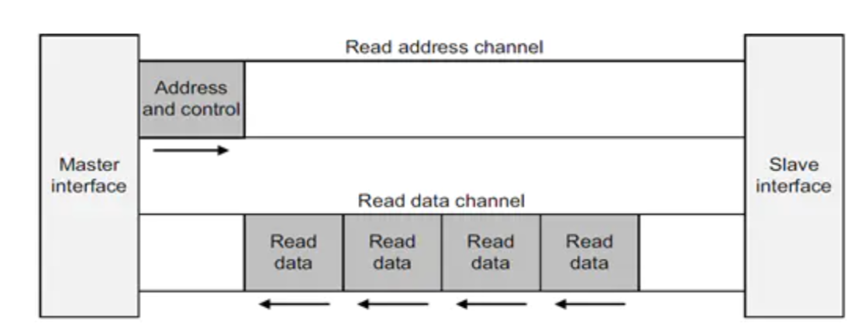

读操作顺序

读操作顺序:

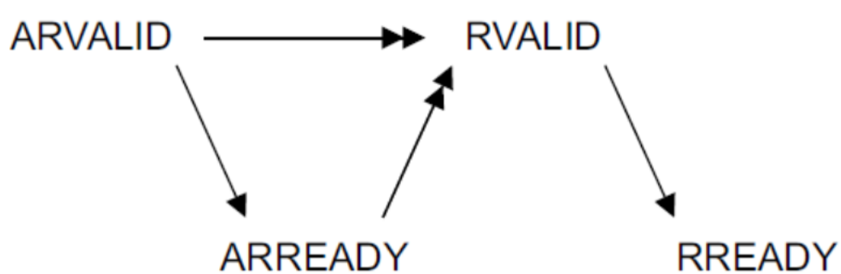

上图为读操作的依赖关系,ARREADY可以等待ARVALID信号,RVALID必须等待ARVALID和ARREADY同时有效后(一次地址传输发生)才能能有效。

写操作顺序:

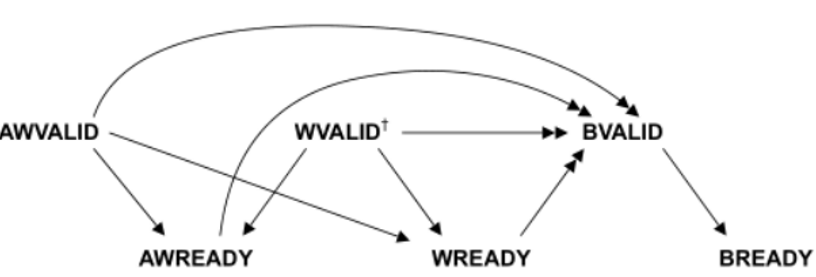

AXI3中写操作中唯一的强依赖关系是写响应通道BVALID,仅当WVALID和WREADY信号同时有效(数据传输完成)且WLAST信号有效(突发传输的最后一个数据传输完成)后才会被置位;

3.3

突发式读写

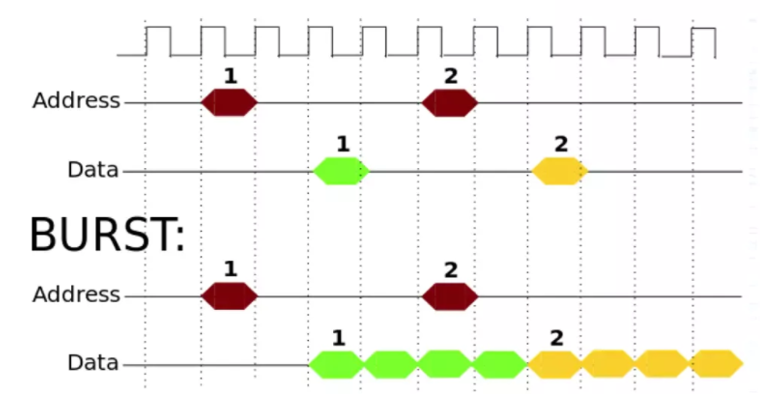

按照传统的RAM的读写方式,给定一个Address,只能读取或者写入一个Data,但是在Burst模式下,给定一个Address,可以连续写入或者读取多组数据。当地址出现在地址总线后,传输的数据将出现在读数据通道上。设备保持 VALID 为低直到读数据有效。为了表明一次突发式读写的完成,设备用 RLAST 信号来表示最后一个被传输的数据。

突发式读写时序图:

这一过程的开始时,主机发送地址和控制信息到写地址通道中,然后主机发送每一个写数据到写数据通道中。当主机发送最后一个数据时, WLAST 信号就变为高。当设备接收完所有数据之后他将一个写响应发送回主机来表明写事务完成。

a. 突发长度(AxLEN)

突发长度为每次突发传输的传输次数 ,范围限制116(AXI4增量模1256)且不能跨越4kb的地址空间,每次突发传输不允许提前终止(可以通过关闭所有数据字段的方式使一段传输数据无效,但传输行为必须完成)。每次传输的突发长度为AxLEN[3:0] + 1(AXI增量模式AxLEN[7:0] + 1.

- ARLEN[7:0]:读地址通道的突发长度接口

- AWLEN[7:0]:写地址通道的突发长度接口

对于回卷模式突发传输,突发长度仅能是2,4,8或16。

b.突发尺寸(AxSIZE)

突发尺寸为每次传输的byte数量,与突发传输的地址预测相关性很强。每次的突发尺寸不能超过数据通道的宽度;若突发尺寸小于数据通道宽度,需要指定哪些位数是有效的。突发尺寸为2^AxSIZE[2:0]^。

- ARSIZE[2:0]:读地址通道突发尺寸

- AWSIZE[2:0]:写地址通道突发尺寸

c.突发类型(AxBURST)

AXI支持三种突发类型:

- FIXED (AxBURST[1:0]=0b00):固定突发模式,每次突发传输的地址相同

- INCR (AxBURST[1:0]=0b01):增量突发模式,突发传输地址递增,递增量与突发尺寸相关

- WRAP (AxBURST[1:0]=0b10):回卷突发模式,突发传输地址可溢出性递增,突发长度仅支持2,4,8,16。地址空间被划分为长度[突发尺寸*突发长度]的块,传输地址不会超出起始地址所在的块,一旦递增超出,则回到该块的起始地址

本文借鉴自:

http://xilinx.eetrend.com/blog/2020/100052459.html

-

协议

+关注

关注

2文章

602浏览量

39215 -

传输

+关注

关注

0文章

153浏览量

27456 -

AXI

+关注

关注

1文章

127浏览量

16625

发布评论请先 登录

相关推荐

使用SpinalHDL实现一个支持AXI协议的互联架构

AMBA AXI协议指南

学习架构-AMBA AXI简介

AMBA 3.0 AXI总线接口协议的研究与应用

深入 AXI4总线 (四):RAM 读取实战

深入剖析AXI的协议与架构(下)

深入剖析AXI的协议与架构(下)

评论