一、AMBA概述

AMBA (Advanced Microcontroller Bus Architecture) 高级微处理器总线架构定义了高性能嵌入式微控制器的通信标准,可以将RISC处理器(精简指令集处理器)集成在其他IP芯核和外设中,它是有效连接IP核的“数字胶”,并且是ARM复用策略的重要组件;它不是芯片与外设之间的接口,而是ARM内核与芯片上其他元件进行通信的接口。比如Xilinx公司的Zynq芯片,就是ARM与FPGA之间的连接通路 .主要包括:

AHB (Advanced High-performance Bus) 高级高性能总线

ASB (Advanced System Bus) 高级系统总线----用的很少

APB (Advanced Peripheral Bus) 高级外围总线

AXI (Advanced eXtensible Interface) 高级可拓展接口

这些内容加起来就定义出一套为了高性能SoC而设计的片上通信的标准;

AHB主要是针对高效率、高频宽及快速系统模块所设计的总线,它可以连接如微处理器、芯片上或芯片外的内存模块和DMA等高效率模块;

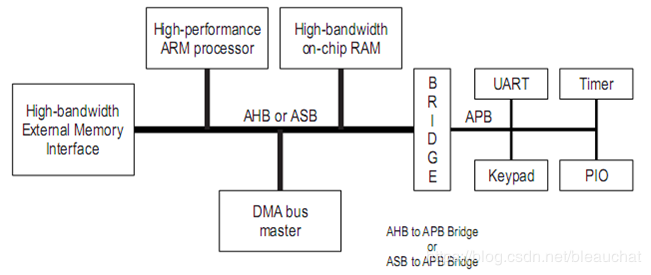

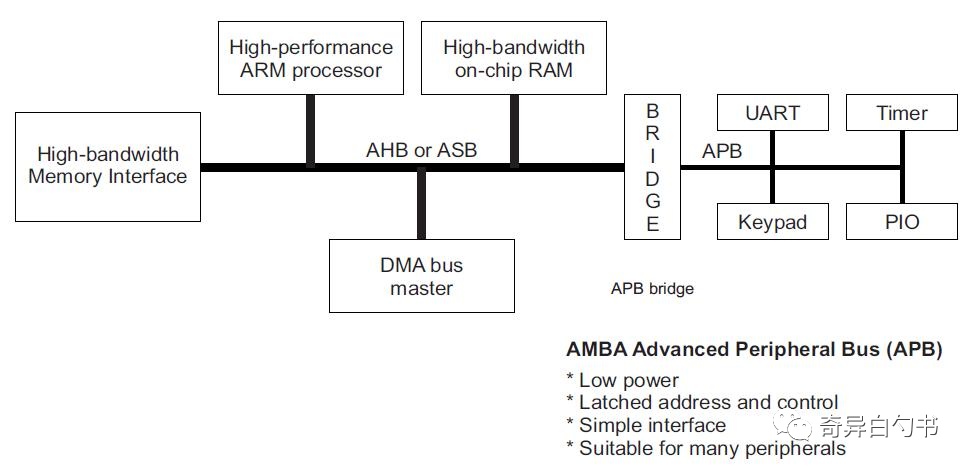

APB主要用在低速且低功率的外围,可针对外围设备作功率消耗及复杂接口的最佳化;APB在AHB和低带宽的外围设备之间提供了通信的桥梁,所以APB是AHB或ASB的二级拓展总线 ;

AXI:高速度、高带宽,管道化互联,单向通道,只需要首地址,读写并行,支持乱序,支持非对齐操作,有效支持初始延迟较高的外设,连线非常多;

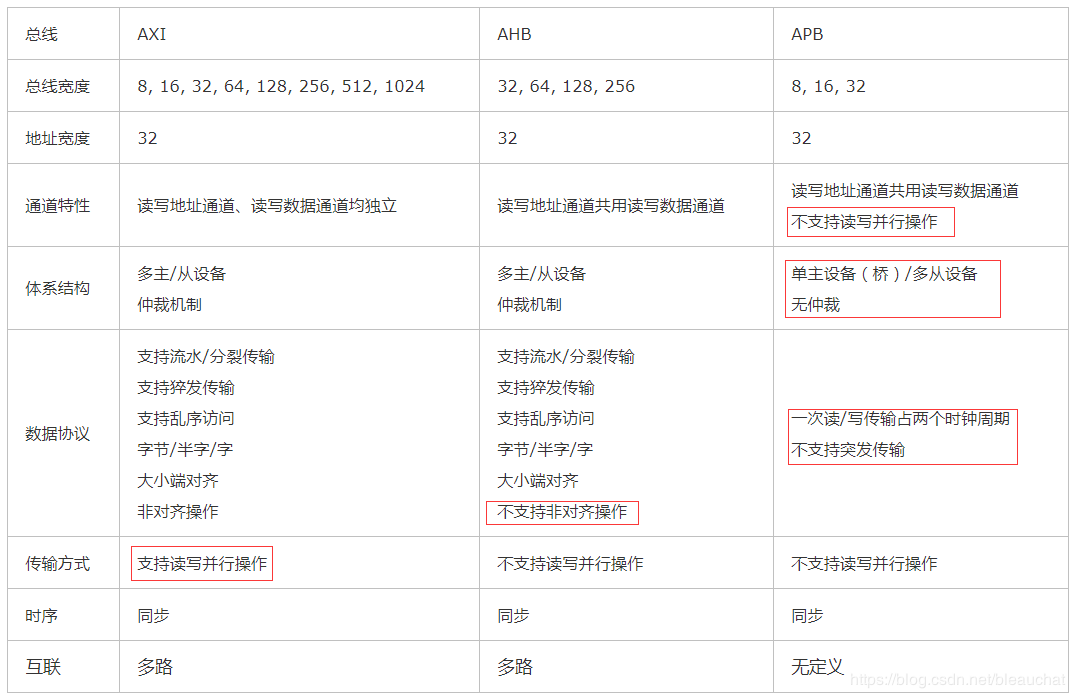

几种AMBA总线的性能对比分析:

AHB与AXI、APB的区别与联系

AHB是先进的高性能总线,AXI是先进的可扩展接口,APB是高级外围总线;

AHB和APB都是单通道总线,不支持读写并行;而AXI是多通道总线,总共分为五个通道,能够实现读写并行;

AHB和AXI都是多主/从设备,且通过仲裁机制实现总线控制权的分配;而APB是单主设备多从设备,其主设备就是APB桥,不具有仲裁机制;

在数据操作方面,AHB和AXI支持突发传输,APB不支持;此外,AXI支持数据的非对齐操作,AHB不支持;

二、AHB总线

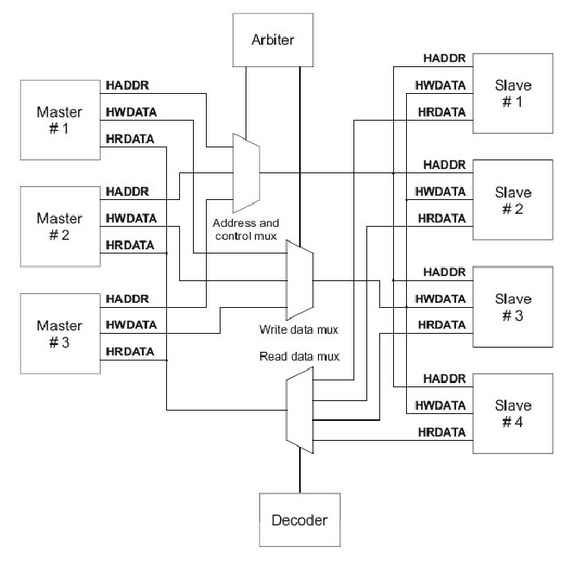

AHB总线强大之处在于它可以将微控制器(CPU)、高带宽的片上RAM、高带宽的外部存储器接口、DMA总线控制器,以及各种AHB接口的控制器等连接起来构成一个独立的完整SOC系统,还可以通过AHB-APB桥来连接APB总线系统。主要包括以下四个部分:

Master AHB主控制器:主控制器可以通过地址和控制信息,可以进行初始化,读,写操作,同一时间只有1个Master会被激活;

Slave AHB从设备:从设备通常是指在其地址空间内,响应主控制器发出的读写控制操作的被动设备,并对Master返回成功、失败或者等待等状态,完成数据的传输控制;

Arbiter AHB仲裁器:仲裁器根据用户的配置,确保在总线上同一时间只有一个主控制器拥有总线控制权限,从而保证总线上一次只有1个Master在工作;AHB总线只能存在一个仲裁器;

Decoder AHB译码器:负责对地址进行解码,并提供片选信号到各Slave;AHB总线只能有一个译码器;

每个AHB都需要1个仲裁器和1个中央解码器,且有且仅有一个!

*AHB基本信号 *

HADDR:32位系统地址总线;

HTRANS:M指示传输状态,NONSEQ、SEQ、IDLE、BUSY;

HWRITE:传输方向1-写,0-读;

HSIZE:传输单位;

HBURST:传输的burst类型;

HWDATA:写数据总线,从M写到S;

HREADY:S应答M是否读写操作传输完成,1-传输完成,0-需延长传输周期。需要注意的是HREADY作为总线上的信号,它是M和S的输入;同时每个S需要输出自HREADY。所以对于S会有两个HREADY信号,一个来自总线的输入,一个自己给到多路器的输出;

HRESP:S应答当前传输状态,OKAY、ERROR、RETRY、SPLIT;

HRDATA:读数据总线,从S读到M;

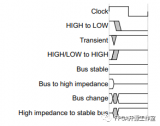

*AHB基本传输 *

两个阶段

地址周期(AP),只有一个cycle

数据周期(DP),由HREADY信号决定需要几个cycle

流水线传送

先是地址周期,然后是数据周期

AHB突发传输与AXI突发传输的特点

AHB协议需要一次突发传输的所有地址,地址与数据锁定对应关系,后一次突发传输必须在前次传输完成才能进行;

AXI只需要一次突发的首地址,可以连续发送多个突发传输首地址而无需等待前次突发传输完成,并且多个数据可以交错传递,此特征大大提高了总线的利用率;

AHB总线与AXI总线均适用于高性能、高带宽的SoC系统,但AXI具有更好的灵活性,而且能够读写通道并行发送,互不影响;更重要的是,AXI总线支持乱序传输,能够有效地利用总线的带宽,平衡内部系统。因此SoC系统中,均以AXI总线为主总线,通过桥连接AHB总线与APB总线,这样能够增加SoC系统的灵活性,更加合理地把不同特征IP分配到总线上;

三、APB总线

APB是一种优化的,低功耗的,精简接口总线,可以威廉希尔官方网站 多种不同慢速外设;主要应用在低带宽的外设上,如UART、 I2C,它的架构不像AHB总线是多主设备的架构,APB总线的唯一主设备是APB桥(与AXI或APB相连),因此不需要仲裁一些Request/grant信号。

APB总线协议包含一个APB桥,它用来将AHB,ASB总线上的控制信号转化为APB从设备控制器上可用信号。APB总线上所有的外设都是从设备,这些从设备有以下特点:

a 接收有效的地址和控制访问

b 当APB上的外设处于非活动状态时,可以将这些外设处于0功耗状态

c 译码器可以通过选通信号,提供输出时序(非锁定接口)

d 访问时可执行数据写入

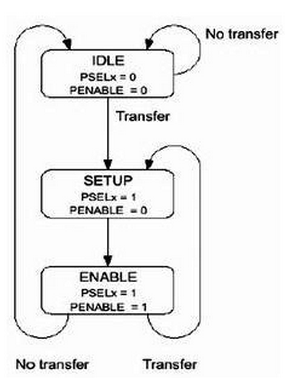

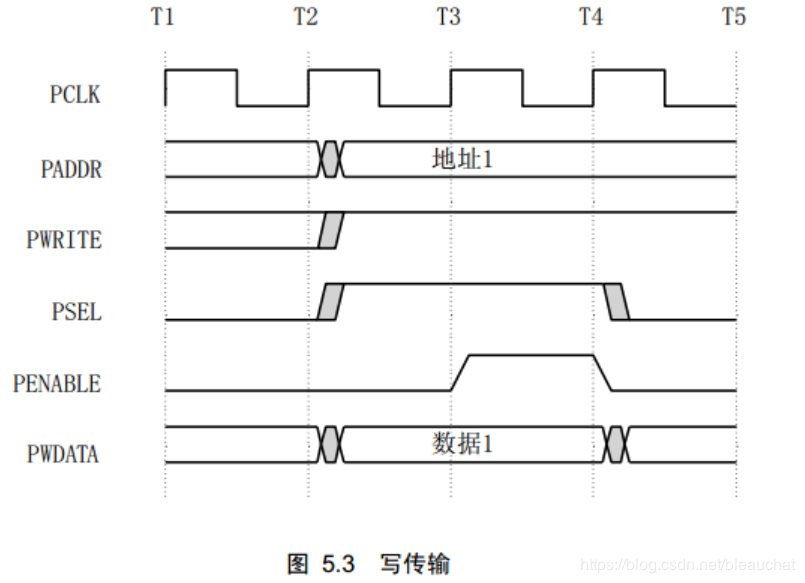

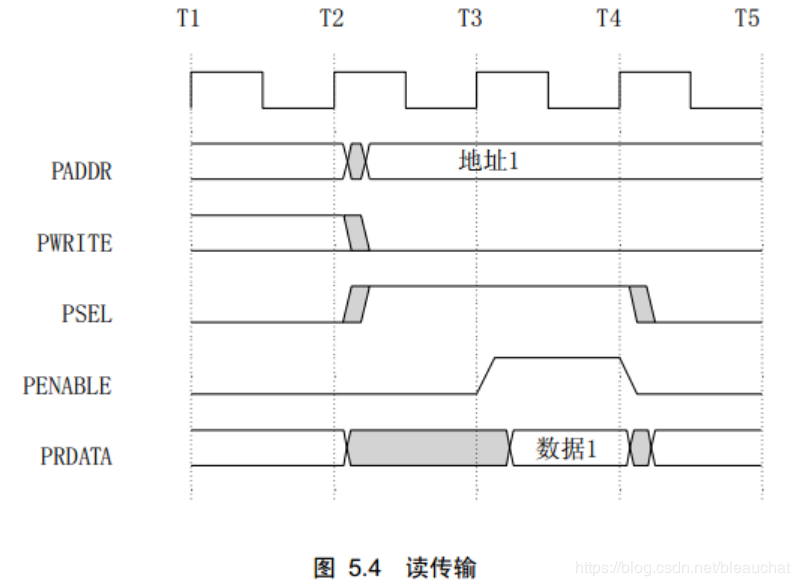

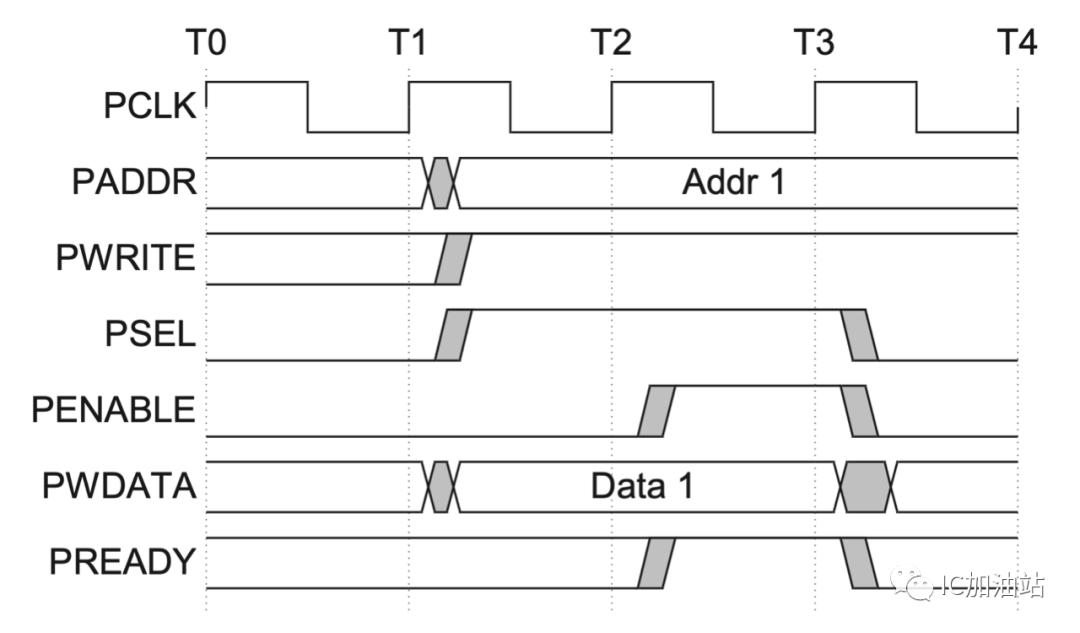

APB的协议也十分简单,甚至不是流水的操作,固定两个时钟周期完成一次读或写的操作。其特性包括:两个时钟周期传输,无需等待周期和回应信号,控制逻辑简单,只有四个控制信号。APB上的传输可用如图所示的状态图来说明:

1、系统初始化为IDLE状态,此时没有传输操作,也没有选中任何从模块;

2、当有传输要进行时,PSELx=1,,PENABLE=0,系统进入SETUP状态,并只会在SETUP状态停留一个周期。当PCLK的下一个上升沿到来时,系统进入ENABLE状态;

3、系统进入ENABLE状态时,维持之前在SETUP状态的PADDR、PSEL、PWRITE不变,并将PENABLE置为1。传输也只会在ENABLE状态维持一个周期,在经过SETUP与ENABLE状态之后就已完成。之后如果没有传输要进行,就进入IDLE状态等待;如果有连续的传输,则进入SETUP状态;

- 写传输

- 读传输

四、ASB总线

ASB总线主要用于高性能系统模块。ASB是可用于AHB不需要的高性能特性的芯片设计上可选的系统总线。ASB也支持高性能处理器,片上内存,片外内存提供接口和慢速外设。高性能,数据传输,多总线主控制器,突发连续传输。ASB总线是位于APB总线架构之上的用于高性能的总线协议,它有如下特点:

a 突发连续传输

b 单管道数据传输

c 多总线主控制器

五、基于AMBA的片上系统

大多数挂在总线上的模块(包括处理器)只是单一属性的功能模块:主模块或者从模块。主模块是向从模块发出读写操作的模块,如CPU,DSP等;从模块是接受命令并做出反应的模块,如片上的RAM,AHB/APB 桥等。另外,还有一些模块同时具有两种属性,例如直接存储器存取(DMA)在被编程时是从模块,但在系统读传输数据时必须是主模块。

如果总线上存在多个主模块,就需要仲裁器来决定如何控制各种主模块对总线的访问。虽然仲裁规范是AMBA总线规范中的一部分,但具体使用的算法由RTL设计工程师决定,其中两个最常用的算法是固定优先级算法和循环制算法。AHB总线上最多可以有16个主模块和任意多个从模块,如果主模块数目大于16,则需再加一层结构(具体参阅ARM公司推出的Multi-layer AHB规范)。

APB 桥既是APB总线上唯一的主模块,也是AHB系统总线上的从模块。其主要功能是锁存来自AHB系统总线的地址、数据和控制信号,并提供二级译码以产生APB外围设备的选择信号,从而实现AHB协议到APB协议的转换。

-

处理器

+关注

关注

68文章

19265浏览量

229676 -

Xilinx

+关注

关注

71文章

2167浏览量

121321 -

总线

+关注

关注

10文章

2878浏览量

88056 -

AMBA

+关注

关注

0文章

68浏览量

14983 -

RISC

+关注

关注

6文章

462浏览量

83714

发布评论请先 登录

相关推荐

AMBA总线概述

ARM总线协议AMBA中AHB、APB的区别与联系

AMBA总线AHB、APB、AXI性能对比分析及AHB详解

基于AMBA总线介绍

深度解读AMBA、AHB、APB、AXI总线介绍及对比

浅述AMBA-APB总线

介绍AMBA2.0总线

数字IC验证:ARM总线协议AMBA中AHB、APB的简介、区别与联系

AHB、AXI、APB分类

STM32菜鸟学习手册——AMBA、APB、AHB简介

AMBA、AHB、APB、AXI总线介绍

AMBA、AHB、APB、AXI总线介绍

评论