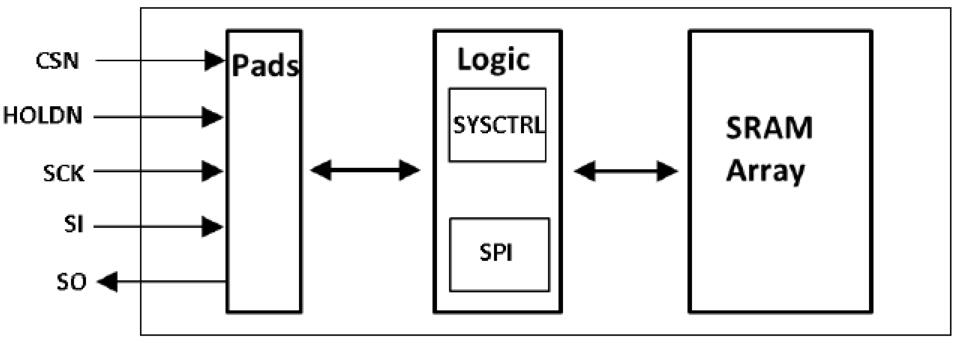

EMISerialSRAM是为串行接口的SRAM,外扩SRAM可以通过使用SPI的接口来将外部RAM添加到几乎所有应用中。串行访问的静态随机存取存储器采用先进的CMOS威廉希尔官方网站

进行设计和制造,以提供高速性能和低功耗。

SCLPSRAC1是一种串行静态随机存取存储器设备SRAM,存储器大小为512Kbit。位宽64Kx8位。采用先进的CMOS威廉希尔官方网站

,提供高速性能和低功耗。使用单一芯片选择(CSN)输入进行操作,并通过简单的串行SPl兼容接口进行访问。一条数据输入和数据输出线与一个时钟一起用于访问设备内的数据。包括一个HOLDN引脚,该引脚允许在不取消选择设备的情况下暂停与设备的通信。暂停时,除CSN引脚外的输入转换将被忽略。可在-40℃至+85℃(工业级)的温度范围内工作,并可采用节省空间的8引脚TSSOP封装。更多产品详情及样品测试联系英尚微电子。

功能框图

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CMOS

+关注

关注

58文章

5710浏览量

235428 -

存储器

+关注

关注

38文章

7484浏览量

163774 -

接口

+关注

关注

33文章

8580浏览量

151038 -

sram

+关注

关注

6文章

767浏览量

114677

发布评论请先 登录

相关推荐

国产MCU有推荐吗?最好是经过市场验证的!

本帖最后由 网卡朋友 于 2024-9-26 16:50 编辑

在电子产品开发中,微控制器(MCU)是实现各种功能的核心部件。随着国内电子威廉希尔官方网站

的快速发展,越来越多的国产MCU开始崭露头角,并在

发表于 09-26 16:38

SRAM1/2/3可以使用LPDMA通过LPTIM触发ADC4搬运数据到SRAM4吗?

SRAM1/2/3 ,将LPDMA 接收数据buff配置为SRAM4,但是现在在正常模式就没有数据,也没有中断产生,请问有大佬在正常模式用到SRAM1/2/3 使用LPDMA 通过LPTIM触发ADC4搬运数据到

发表于 09-20 15:17

spi_flash_read在512K以上无法进行4M闪存怎么解决?

我有一个 ESP12。

读取低于 512k 的闪光灯是成功的,但高于 512k 的闪光灯不能成功。

我确认闪光灯是 4M,带有 esp_tool

esptool.py v1.2-dev

连接

发表于 07-19 11:59

请问如何使用片外SRAM?

Hi , 在项目中,我们需要增加片外SRAM,型号是IS62WVS5128GALL 大小是512kb,请问你们是否支持此IC,能否提供驱动或者demo?

发表于 06-25 08:01

sram 512k实现softAP配网,wifi报错的原因?

采用的是安信可的模块,sram 512k

程序主要实现了softAP 配网,蓝牙gatt server和gatt client,及wifi tcp socket通信

一般运行12小时左右,就会持续

发表于 06-06 06:53

用MDK将UCOS+UCGUI下载到外部SRAM中调试慢怎么解决?

写数据。

@@触摸屏是使用STM32内部ADC采样触摸数据,同样使用了一个任务不停的对于UCGUI的GUI_TOUCH_Exec();)

外部SRAM:512K的IS61LV25616AL-10T

发表于 05-17 11:41

STM32H7使用DMA方式读取SD卡,DMA缓冲是否只能处于AXI SRAM?

除了512K的 AXI SRAM,还有没有其他的SRAM 区域能访问到? 因为我想这整个512K 的AXI SRAM 做其他用途,变量都定义

发表于 04-18 06:00

Microchip推出容量更大、速度更快的串行SRAM产品线

为满足客户对更大更快的SRAM的普遍需求,MicrochipTechnology(微芯科技公司)扩展了旗下串行SRAM产品线,容量最高可达4Mb,并将串行外设接口/

Microchip推出容量更大、速度更快的串行 SRAM产品线

Technology(微芯科技公司)扩展了旗下 串行 SRAM 产品线,容量最高可达4 Mb,并将串行外设接口/串行四通道输入/输出接口(SPI/SQI™)的速度提高到143 MHz

发表于 04-03 15:24

•1190次阅读

Microchip Technology扩展了旗下串行SRAM产品线,容量最高可达4Mb

为满足客户对更大更快的 SRAM 的普遍需求,Microchip Technology(微芯科技公司)扩展了旗下串行SRAM产品线,容量最高可达4 Mb,并将串行外设接口/

SRAM CLA和SRAM有什么区别

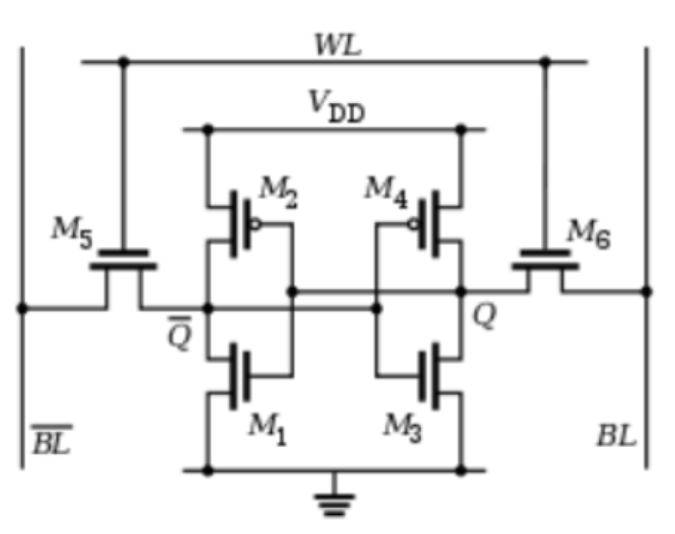

每个SRAM单元的核心由两个CMOS反相器构成,这两个反相器相互连接,每个反相器的输出电位被用作另一个反相器的输入。这种结构使得每个SRAM单元都可以保存一个二进制位(0或1),直到它被新的数据覆盖。

国产512kbit串行SRAM----SCLPSRAC1

国产512kbit串行SRAM----SCLPSRAC1

评论