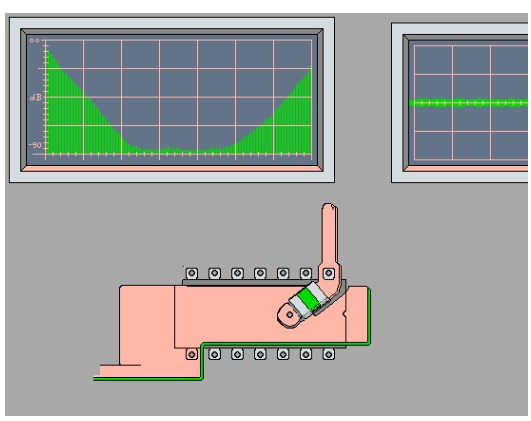

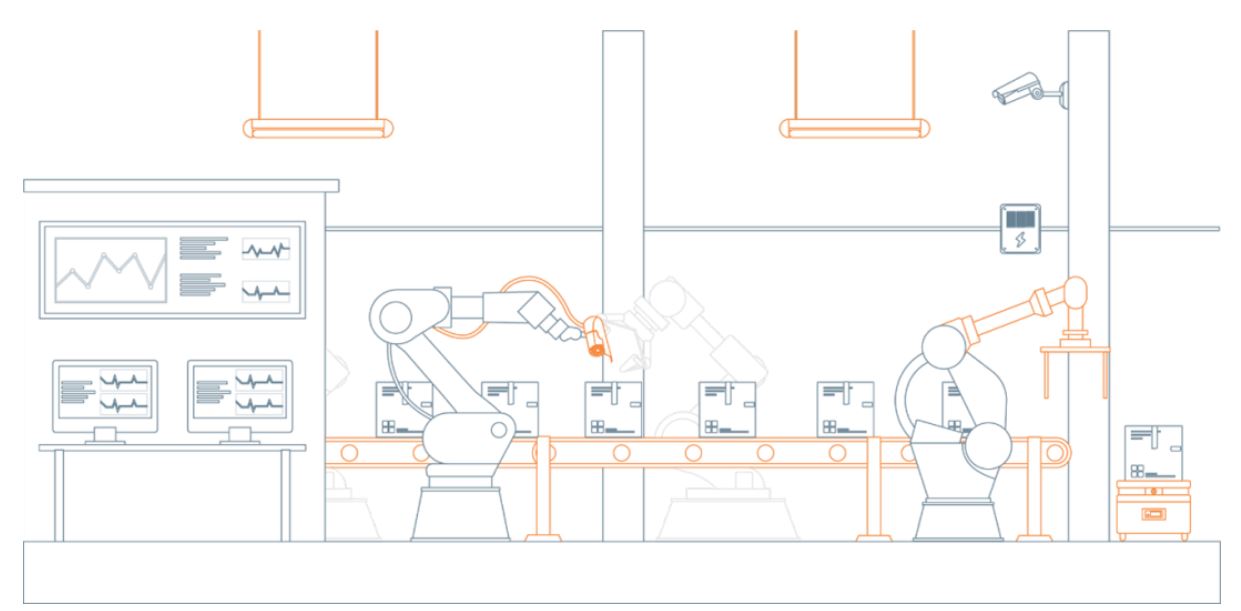

先看一个很形象的图,直观体会一下一个电容放置位置不同起到的作用有多大的差异。

这张动图其实传递了如下的信息:

1 在电源管脚上放置一个104(0.1μF)的电容能够有效抑制电源上的噪声,也就是能够对电源噪声去耦;

2 “ 电源 -- 去耦电容 -- 地 ”三点一线的距离越近,则去耦的效果越好;

3 相同材料的电容,即便电容容量减少为1/10,去耦的效果并不会有什么明显变化,我们对于高频去耦用同样封装的器件,容值为0.01μF、0.1μF、1μF效果相差不大;

4 同样容值,贴片(SMD)封装的电容比穿孔的电容效果更好,原因就是穿孔电容的管脚等效的电感要大很多,影响了去耦的效果;

5 电源平面和地平面的使用,一方面可以让三点一线的路径更短,而且两个平面相当于一个大电容,也起到了去耦的作用

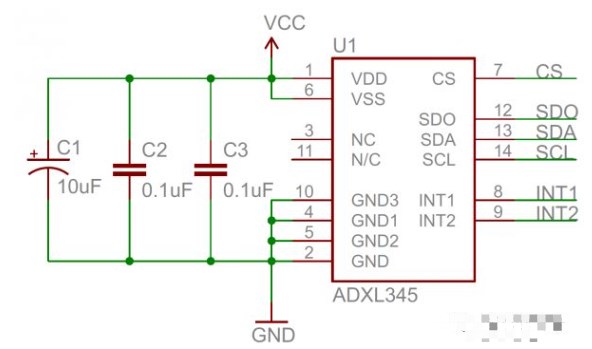

我们再来看一个实际的典型电路 - ADXL345是一颗加速度计传感器芯片,有两个分得比较开的电源管脚(Pin 1和Pin 6),在原理图中使用三个去耦电容来帮助降低传感器电压上的噪声 - 两个0.1μF的陶瓷电容和一个10μF的钽电解共同完成去耦功能。

再看一下最终的PCB板 - 这个板子密度不高,速度也不快,只需要2层板就可以了,没有专门的地平面,在无布线的区域采用了大面积铺地的方式来降低公共地(GND)的阻抗,三颗去耦电容的接地端直接用焊盘跟GND相连,跟电源管脚连接的另一端则尽可能接近电源管脚。

其实放置去耦电容的规则非常简单: 最小化电阻,最小化电感 。 这是通过将电容尽可能靠近电源引脚并使用尽可能短的走线实现所有连接来实现的。

理想情况下,如果采用4层以上的板子,有专门的地平面、电源平面,可以通过过孔(via)将器件上的地和电源连接到相应的地平面和电源平面。

简单总结一下使用去耦电容的要点:

除非特别说明,一般可为每个电源引脚提供0.1μF陶瓷电容,最好为0805或更小(我比较喜欢0603的,占空间小,性能还好),与10μF的钽电容或陶瓷电容并联;

如果只关心高频噪声,10μF的电容也可以省去,或者用较小的电容替换它;

将高频陶瓷电容尽可能靠近电源引脚放置,并使用短走线和过孔来最大限度地减少寄生电感和电阻。用于低频旁路的较大电容器的位置并不十分关键,但这些电容器也应该尽可能接近IC的电源引脚,容值与封装越大,去偶半径越大,可以对较大的区域的电源进行有效去偶,大封装和大容值的去偶电容可以同时管控多个电源引脚的去偶;

电源的去耦电容均匀分布在四周,靠近相应的电源管脚,容值小的电容最靠近管脚,容值大的距离相对较远

如果需要补偿电源的长期偏差,需要大量存储电荷,需要为每个IC增加一个更大的电容,例如47μF;

如果设计包含非常高的频率或特别敏感的电路,可以使用仿真工具分析旁路网络的AC响应(可能很难找到ESR和ESL的数据参数,特别是考虑到电容的ESR随频率变化也很大 - 尽可能做到最好),还要考虑到多电容并联以及计入电源平面、地平面等的综合效应。

对于电源和地平面的去耦是通过电源和地平面之间形成电容来对高频噪声进行去耦的。应尽可能减小电源和地平面之间的距离,对于高速电路,一般内层会有完整的电源及地平面,这时去耦电容及IC的电源、地引脚直接过孔via打到电源、地平面即可,不需用导线连接起来。

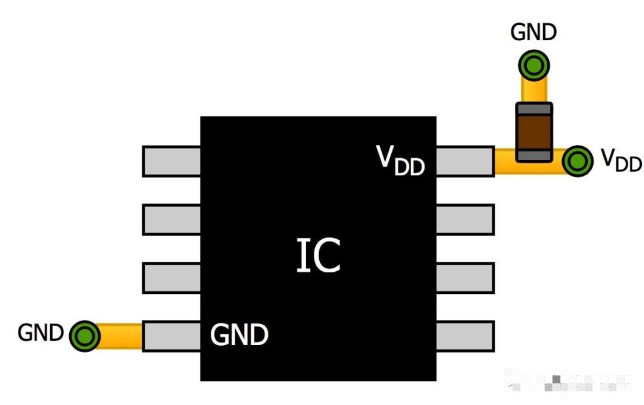

上图左侧,电源引脚和接地连接都比较短(直接通过过孔连接到内部地平面)是最有效的配置;上图右侧,PCB走线内的额外电感和电阻将造成去耦方案的有效性降低,且增加封闭环路可能造成干扰问题。

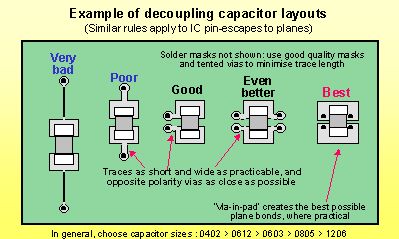

下面的图是去耦电容通过过孔与地进行连通的方法比较,从最左侧的效果最差依次编号,直到最右侧效果最佳,当然具体采用那种方式还要取决于其它一些因素,综合考虑后做一个折衷。

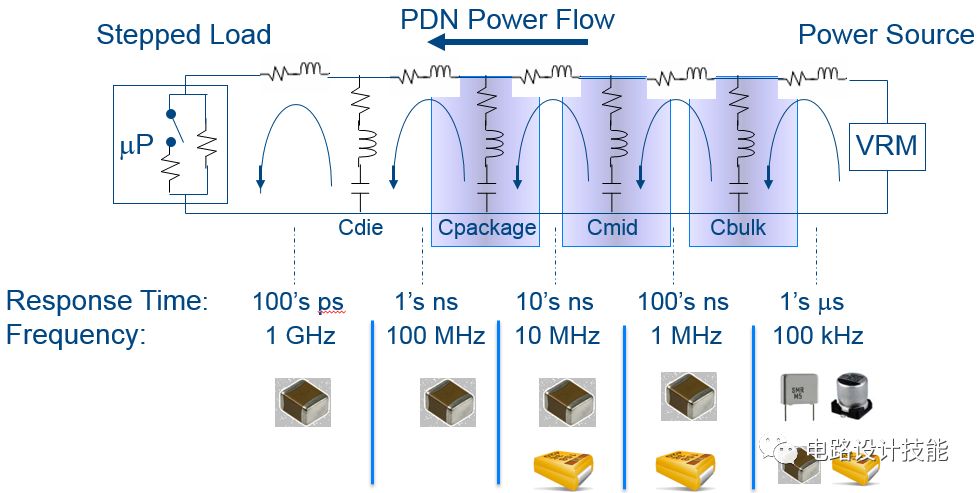

最后再回顾一下上一篇文章中我们的最后一个图,它是一个实际电子产品系统的供电分布网络(PDN - Power Distrubution Network)图,为了强调噪声的起源(最左侧),把电源模块(VRM)放到了最右侧。PCB上的走线、过孔、相关的器件引脚等都会产生寄生电阻、电感等,在图中以R+L的方式等效表达出来。

在这个图中可以看出针对IC器件内部(Die)、针对整个IC器件(Package)、针对某一个功能模块中的电路单元都有相应的去耦电容,最左侧(靠近内核)采用频率响应很高的小容值、小封装的陶瓷电容,到右侧则是低频率、容量比较大的电解电容。

-

传感器

+关注

关注

2551文章

51097浏览量

753527 -

PCB板

+关注

关注

27文章

1448浏览量

51645 -

SMD

+关注

关注

4文章

570浏览量

48452 -

去耦电容

+关注

关注

11文章

316浏览量

22335 -

电源噪声

+关注

关注

3文章

151浏览量

17480

发布评论请先 登录

相关推荐

哪位大哥可以帮忙讲一下LABview的系统构成

讲一下硬件系统中常用的滤波电路

讲一讲在FatFs文件系统下读取SD卡的该如何做

选定的电容该放在什么位置?

讲一下选定的电容该放在什么位置?

讲一下选定的电容该放在什么位置?

评论