12 容性终端负载对信号反射的影响

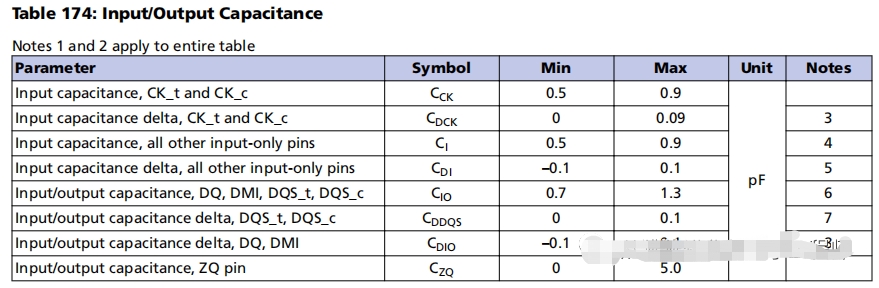

之前的文章讲述的都是阻性终端负载的反射。其实在负载(芯片管脚)上也有输入电容存在,通常都是几个pf。如下Table 174是某颗LPDDR4的各个输入ball的输入电容值。特别是当出现一个源端同时驱动多个负载时,负载端的输入电容并联总值会更大,例如SOC驱动多个DDR芯片。

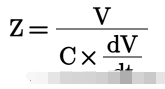

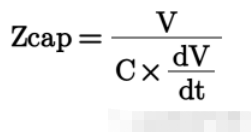

如下是电容的阻抗公式:

因为这些容性终端负载的存在,之前文章提到的反射系数计算公式中的阻抗就不是一个单纯的电阻了,而是一个复合的阻抗。其中容性终端负载会使反射系数中的瞬态阻抗随着时间而变化。当信号的上升时间小于电容的充电时间,可以分三个阶段来看电容阻抗的变化:

①在信号刚到达负载端时,电容两端的电压快速上升,此时阻抗很小。

②随着电容充电的进行,电容两端的充电电流慢慢减小,即dV/dt缓慢下降,电容阻抗开始变大。

③如果信号上升时间足够长,可以使电容充满电,此时电容相当于开路。

因此,随着容性终端负载的变化,反射系数也随着时间变化。在带容性负载的传输线末端看来,电压的变化就像是RC在充电。C是终端负载电容,R是传输线阻抗。

此处需要先理解RC电路的时间常数τ。它是指电容从0开始充电,充电到最大电压值的1/e时,所需要的时间。因为自然常数e=2.718,所以1/e≈0.37。因此

假如一条传输线的阻抗是50R,容性负载是2pf。由此传输线和容性负载带来的10~90%充电时间是:

2.2 x 50R x2pf=0.22ns。

如果源端输出信号的上升时间比0.22ns短,则在最终的信号上升时间波形上,传输线末端的容性负载占主导地位。如果源端输出信号的上升时间比0.22ns长,则在最终信号上升时间中源端输出信号的上升时间占据主导地位。其实当源端信号的上升时间和0.22ns相当时,由传输线和容性负载带来的10~90%充电时间已经对信号时序有影响了。例如一个信号源的上升时间是1ns,0.22ns的Z0-C延迟加在信号上,影响不明显。另一个信号源的上升时间是0.1ns,0.22ns的Z0-C延迟,对信号的影响就和明显了。

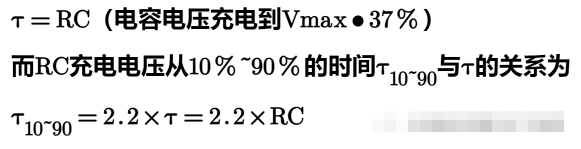

如下是在终端有一电容负载,电容取值分别是0pf~4pf时的仿真电路。

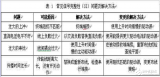

依据上述计算公式,得到不同负载电容值时,信号从10%上升到90%时的时间Tr如下表:

| 不同负载电容时,信号从10%上升到90%的时间Tr1 | |||

|

系数 |

C1(pf) | TL1(Ω) | Tr(ns) |

| 2.2 | 1 | 50.1 | 0.11022 |

| 2.2 | 2 | 50.1 | 0.22044 |

| 2.2 | 3 | 50.1 | 0.33066 |

| 2.2 | 4 | 50.1 | 0.44088 |

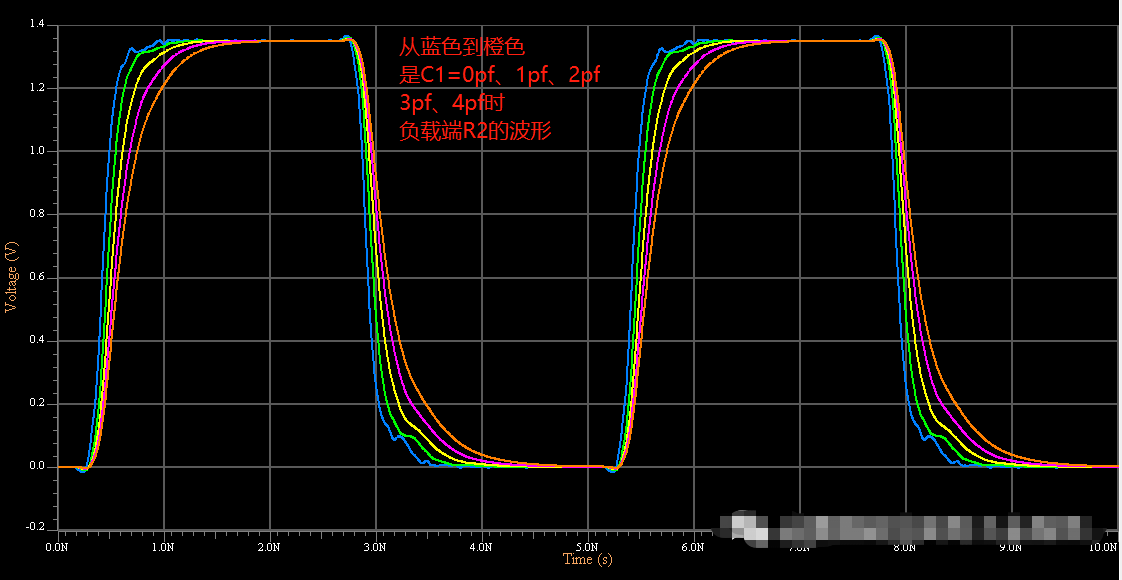

之前文章讲过本仿真电路的源端波形,从10%上升到90%的时间Tr2=0.195ns。因此从C1=2pf开始,在最终的信号波形上,容性负载就占据主导地位了。如下图仿真波形(黄色为C1=2pf,紫色为C1=3pf,橙色为C1=4pf时的波形),信号边沿变缓慢的趋势越来越明显。

另外,对于同样的容性终端负载,特性阻抗越小,时延累加越小。因为上述公式中C已经固定,能控制的就是R。因此在允许的范围内,可以使R的在50R偏下一点。

13 传输线上引入的容性因素对反射的影响

在源端和负载端之间的传输线上,有些因素也会带来寄生电容。例如传输线上的测试点(焊盘)、via等。这些寄生电容,在信号上升过程中,就像在信号路径和返回路径上并联了一个容抗Zcap。这个跨接在传输线上的并联阻抗会引起反射。

信号从源端出发,到达传输线中间的Zcap时,会有上升沿的延时,但是并没有波形的振荡(如上一节所述)。波形继续向前,到达负载终端时,发生反射。当此反射波形在返回源端的过程中,到达Zcap时,波形中的负电压部分会在Zcap处再次反射,这些反射回负载端的波形也是负电压,并且最终在负载端的波形上形成下冲。电容量越大,电容的阻抗Zcap越小,负反射电压越大,从而接收端的信号下冲越大。信号的上升时间越短,电容的阻抗Zcap越小,负反射电压越大,接收端的信号下冲也越大。

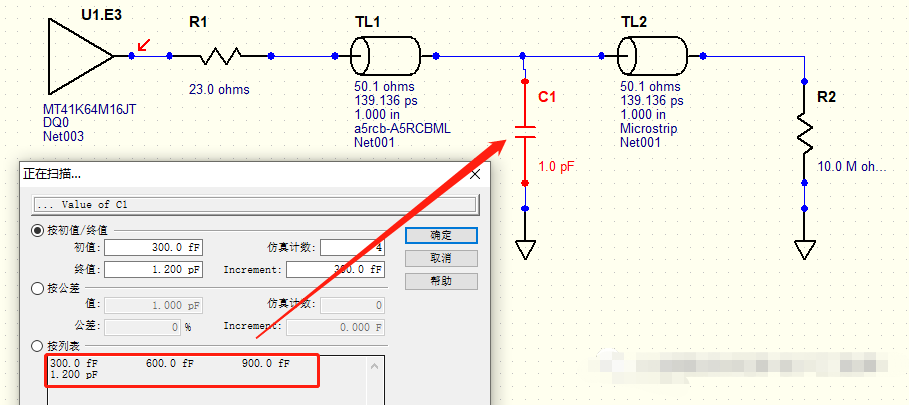

如下图是一个仿真电路,用C1来interwetten与威廉的赔率体系

传输线中途的寄生电容。C1的取值分别是0.3pf、0.6pf、0.9pf、1.2pf。之所以选择0.3pf,是因为通常PCB设计中,一个via的寄生电容大约就在这个数量级。

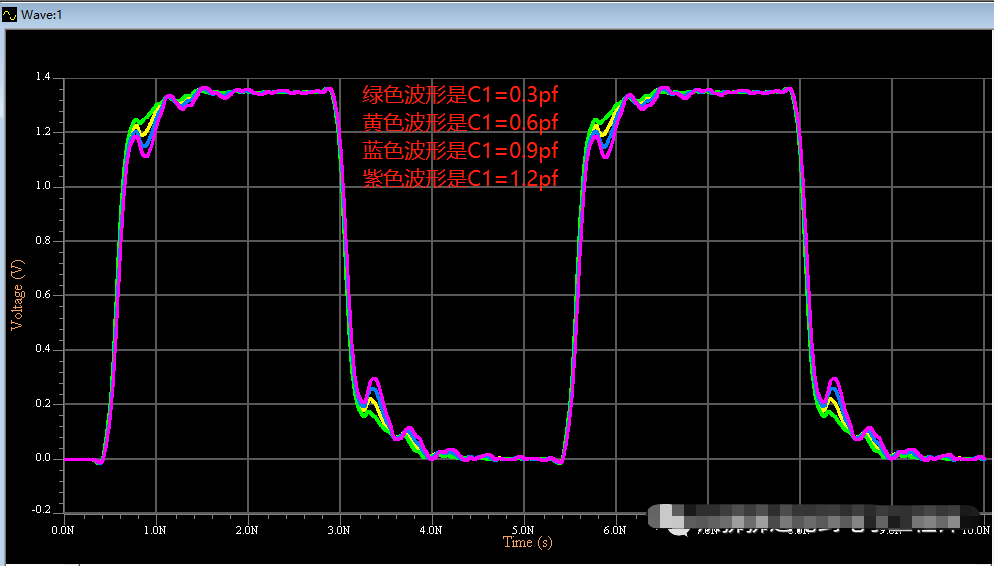

仿真结果如下:和上一节的仿真结果比较,可以看到终端电容负载只带来信号上升时间的延迟(变缓),并不会带来信号的失真(振荡)。而在传输线中途出现的寄生电容则会带来信号失真。

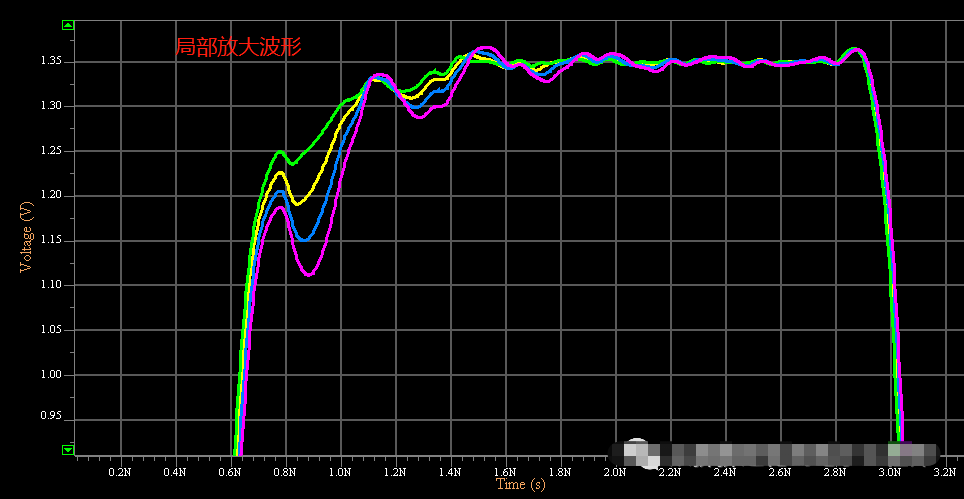

下图是将波形局部放大的结果。可以看到随着电容的增大,信号的下冲越明显。信号只有下冲失真。随着整体都有振荡,但是在上冲方面并没有多大的幅度振荡。这也是为什么很多芯片的应用手册中要求高速信号在进行PCB走线时,最多换一次走线层,这样顶多出现2个via。

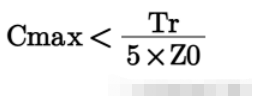

随着信号上升时间越来越快,传输线上可以接受的寄生电容越来越小。为了降低Zcap对信号反射的影响,希望Zcap大一些好,因为Zcap大一点,接收端的信号下冲就会小一些。但是如果Zcap太大了,又会减缓信号的上升时间。通常希望Zcap>5 x Z0.

电容阻抗的计算公式如下:

针对高速信号的上升沿波形,dV/dt就是V/Tr,因此

Tr是高速信号的上升时间(从V x10%上升到V x90%)。V是高速信号的高电平值。

Zcap的单位是欧姆。C的单位是nF,Tr的单位是ns。

因为希望Zcap>5 x Z0,所以

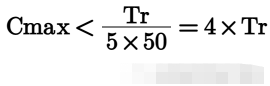

对于常见的50R阻抗控制传输线,

Cmax的单位是pf,Tr的单位是ns

例如针对Tr是1ns的信号,Zcap可以接受的最大电容是4pf。这个经验公式可以在接插件选型时用来做为衡量参数之一。

-

DDR

+关注

关注

11文章

712浏览量

65318 -

soc

+关注

关注

38文章

4163浏览量

218182 -

信号

+关注

关注

11文章

2790浏览量

76736 -

信号完整性

+关注

关注

68文章

1405浏览量

95459 -

反射

+关注

关注

0文章

67浏览量

15862

发布评论请先 登录

相关推荐

信号完整性(五):信号反射

信号完整性简介及protel信号完整性设计指南

信号完整性之反射(六)

信号完整性之反射(六)

评论