等离子体均匀性和等离子体位置的控制在未来更加重要。对于成熟的威廉希尔官方网站 节点,高的产量、低的成本是与现有生产系统竞争的关键因素。如果可以制造低成本的可靠的刻蚀系统,从长远来看,可以为客户节省大量费用,有可能促使IC制造商取代现有系统发展低成本的新系统。最关键的是成品率,正常运行时间应相同或高于现在的系统,而且产量更高,耗材更低,使生产商可以相信通过一年的系统更新,节省的运作成本可以还清设备成本。

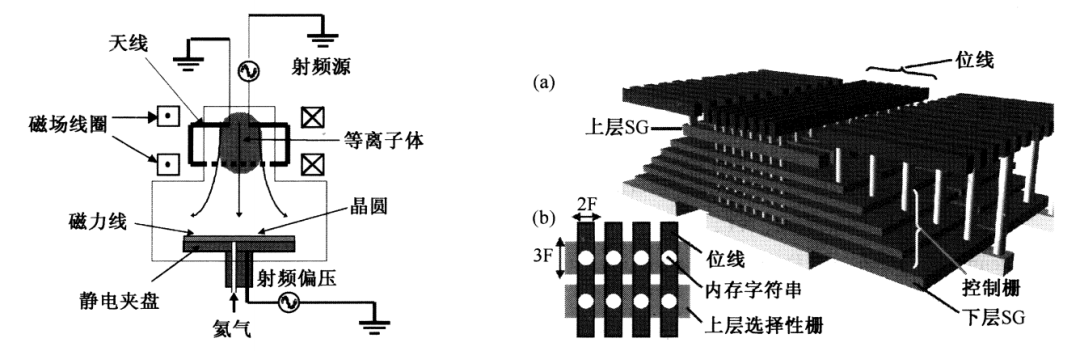

最近,新材料已被添加到IC芯片制造工艺中,如HKMG和ULK介质。这些新材料的刻蚀是刻蚀工艺面临的挑战之一。新器件结构,如三维FinFET器件、三维栅器件、垂直结构器件等也被应用于先进的IC芯片制造。对于三维FinFET器件,单晶硅刻蚀工艺变得越来越具有挑战性,特别是制作在体硅衬底上的FinFET。对于先进的埋字线DRAM,刻蚀工艺需要约1:1的单晶硅和氧化硅刻蚀选择性。进一步提高NAND快闪存储密度的方法之一是釆用3D堆叠结构(见下图)。下图显示了4层NAND快闪单元用于形成一个4位快闪存储器。实际应用中可能需要16位字符。存储器字符孔刻蚀工艺已经非常具有挑战性了,而且字线接触孔刻蚀不同深度将更加困难。如硅通孔(TSV)3D封装工艺也对刻蚀工艺提出了更多的挑战和机遇。不同于亚微米和纳米级图形刻蚀工艺,TSV的刻蚀工艺有较大的关键尺寸CD,从50um到5um,而且还需要高的刻蚀速率达到所需的产量。

本节内容回顾

1.IC芯片封装时,需要刻蚀的4种材料是单晶硅、多晶硅、电介质(二氧化硅与氮化硅)和金属(TiN、ALCu、Ti、W和WSi2)。

2.4种主要的刻蚀工艺是硅刻蚀、多晶硅刻蚀、电介质刻蚀和金属刻蚀。

3.湿法刻蚀利用化学溶液溶解需要刻蚀的材料。

4.干法刻蚀利用化学气体,经过物理刻蚀、化学刻蚀或两种刻蚀威廉希尔官方网站 的组合方式刻蚀掉衬底表面的材料。

5.湿法刻蚀具有高的选择性、高的刻蚀速率和低成本。受等向性刻蚀轮廓的限制,湿法刻蚀不能用于图形尺寸小于3am图形化刻蚀工艺。

6.湿法刻蚀普遍用于先进的半导体工艺中去除薄膜并监测电介质薄膜的质量。

7.等离子体刻蚀工艺中,刻蚀剂注入反应室并在等离子体中分解。自由基将扩散到界面层并被表面吸收。在等离子体轰击下,将和表面的原子或分子产生反应,产生的挥发性生成物从表面释放出来,扩散穿过边界层后,经由反应室对流作用被抽出。

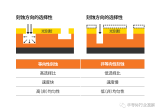

8.有两种非等向性刻蚀机制:损伤机制和阻绝机制。电介质刻蚀使用损伤机制,硅、多晶硅和金属刻蚀使用阻绝刻蚀机制。

9.电介质刻蚀使用氟元素化学品,经常使用CF4.CHF3和AlCF4是主要的刻蚀剂,而CHF’是聚合物,可以用于改善PR和硅的刻蚀选择性。Ar用于增强离子轰击。O2能增加刻蚀速率。而珏可以用于改善对PR和硅刻蚀选择性。

10.对于低左和ULK电介质刻蚀,CO可以改善刻蚀工艺的控制。

11.硅刻蚀使用HBr作为刻蚀剂,O2和氟用于侧壁刻蚀。

12.多晶硅可以利用Cl2或SF6刻蚀,被用于改善氧化物的选择性,而HBr有利于侧壁沉积。

13.金属刻蚀使用Cl2>BCl3和N2提高侧壁层的钝化作用。

14.铜金属化不需要金属刻蚀工艺,而是需要电介质槽形刻蚀。

15.ULK电介质刻蚀后的光刻胶去除威廉希尔官方网站 越来越复杂,一般使用硬遮蔽层TiN。

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50818浏览量

423713 -

等离子体

+关注

关注

0文章

122浏览量

14229 -

封装

+关注

关注

126文章

7905浏览量

142971 -

制造工艺

+关注

关注

2文章

179浏览量

19757 -

刻蚀

+关注

关注

2文章

186浏览量

13107

原文标题:半导体行业(一百七十)之刻蚀工艺(二十一)

文章出处:【微信号:FindRF,微信公众号:FindRF】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

半导体前端工艺之刻蚀工艺

芯片制造的刻蚀工艺科普

半导体刻蚀工艺简述

半导体刻蚀工艺简述

评论