静电放电(ESD)防护是电子系统设计者和制造商面临的主要挑战之一。 这些ESD事件可能在现场发生并导致系统故障,引起短时间系统中断(软故障),甚至引起系统芯片功能的物理损坏,从而导致硬故障。

当发生ESD事件时,外部的ESD保护器件应能保护整个系统。 这不仅包括系统芯片,还包括敏感无源组件。

典型ESD故障情况

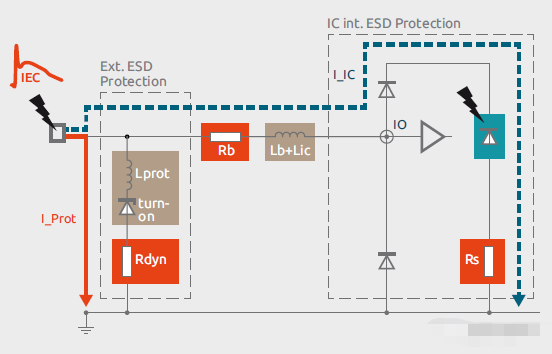

一个简化的系统等效电路示例如下,用于说明典型ESD故障情况。 电路由外部ESD保护器件、信号PCB铜线寄生器件、芯片内部I/O ESD保护和电源及地间ESD保护组成。 系统动态和准静态参数分别用棕色和橙色框标出。

列出两种不同的失效情况如下。

第一种,非常敏感的栅极氧化层。

描述了在ESD脉冲侵入的前几纳秒内,MOSFET晶体管的敏感栅极氧化层被过电压破坏的情况。 失效场景发生在非常敏感的栅极氧化层上。

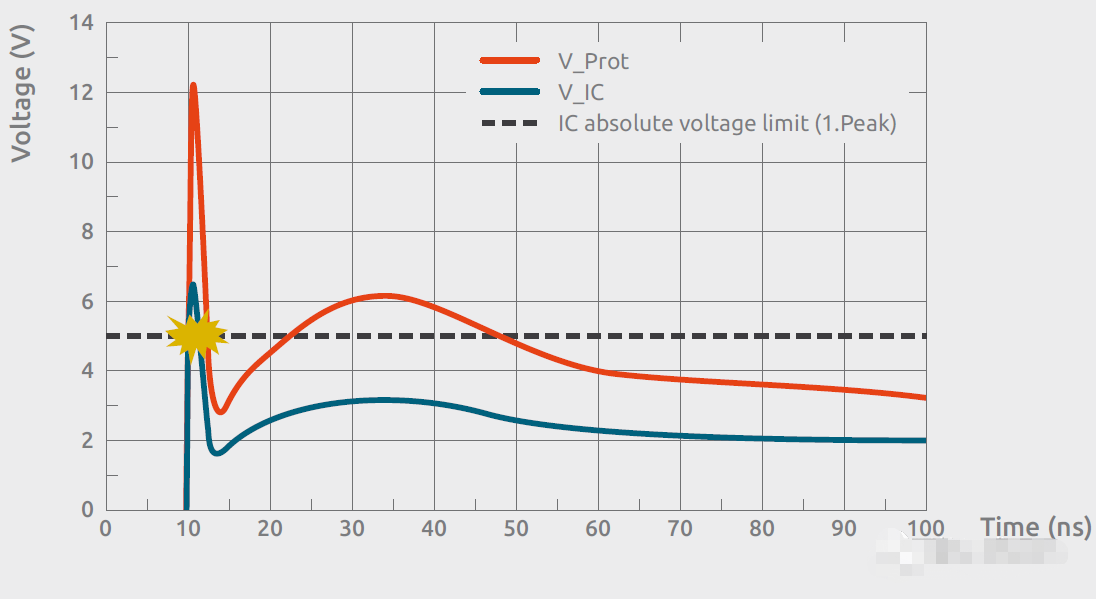

时域电压评估见下图:蓝色曲线显示了过电压发生在IC内部I/O引脚,红色曲线表示外部ESD保护器件的压降,虚线黑色定义IC绝对电压限值。

第二种,IC内部功耗。

系统会遭受由于流经IC内部ESD保护组件的大电流产生的高功耗而导致的热损坏。

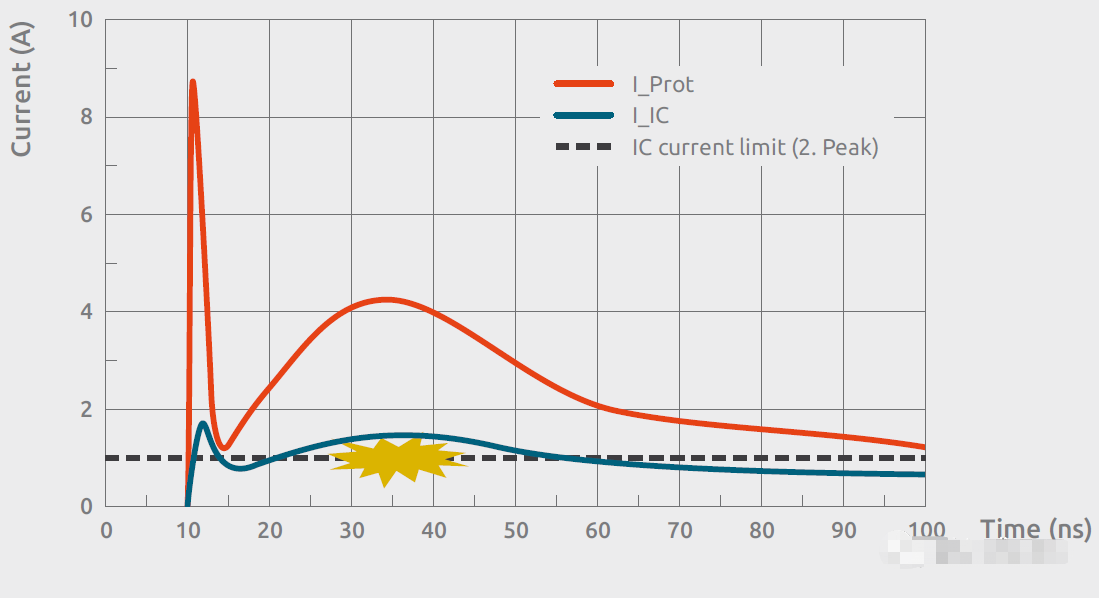

时域电流评估见下图:蓝色曲线为流过IC内部ESD保护器件的电流,红色曲线为流过外部ESD保护器件的电流,黑线虚线为稳态状态下IC电流限制值。

所以ESD保护器件应当非常快地导通,并且导通电阻(动态电阻)尽可能地低。 此外,其ESD保护器件寄生电感包括PCB铜线寄生电感应尽可能低。

系统高效ESD设计

系统高效ESD设计(SEED, system efficient ESD design)方法可用于支持工程师建模电子系统并仿真其ESD条件下的行为。 暂态系统分析可用于预测开发阶段系统级ESD健壮性,并有助于最小化开发周期及降低成本。

有两种方法建模系统中芯片模型。 一种是SPICE(Simulation program with integrated circuit emphasis)模型,是晶体管级别的电路描述,是描述物理元素的模型,它包含半导体器件内所有电路描述的详细信息。 另外一种是行为(behavior)模型,避免了复杂物理工艺的描述,不包含芯片设计厂家专有数据。 此外,还需要增加分立器件,及描述PCB铜轨迹线特征的传输线模型等。 其中TLP(transmission line pulse)模型即是其中一种行为模型。

TLP(传输线脉冲)测试

TLP是一种相对较新的测量威廉希尔官方网站 ,用于表征完整接口或ESD保护组件的特性。

TLP是50 Ω受控阻抗环境中的短时矩形脉冲,可提高测试准确度和测量再现性。 TLP能够表征具有短脉冲宽度和快上升时间的承压电应力设备的性能特性。 低占空比可防止发热。

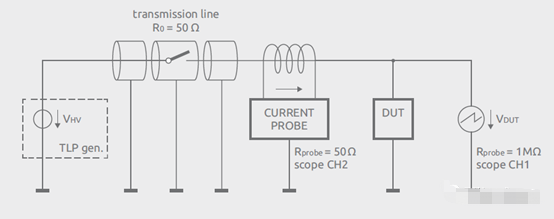

如下图显示的TLP测试环境所述:发生器以预先调节的电压为50 Ω传输线充电。 开关闭合,能量应用于被测器件(DUT)。 进入被测器件的电流通过电流探针进行测量,而被测器件上的电压则使用高速示波器进行监测。 脉冲长度、上升时间和下降时间可在发生器上更改。 施加标准脉冲的持续时间通常为100ns,上升时间和下降时间分别为10ns。 最小可设置转换时间为300ps。

TLP测试以预定义的步宽从低脉冲电压到更高电压逐步开始执行。 如下图中描绘的TLP测量电压和电流迹线所示,电压和电流采样以20 ns时间窗取平均值。 这段时间窗在100 ns测试脉冲内的70 ns到90 ns间,通过这种基于时间窗的方法可消除噪声的影响。 此外,时间窗的位置确保系统稳定,从而消除过冲等影响。 每个测量结果都成为TLP图上的一个点,显示TLP I-V特性,即构成TLP曲线。

TLP曲线ΔV/ΔI的陡峭度即是动态电阻R 戴恩 ,在选择ESD和浪涌保护器件时,这是一个重要的考虑参数。

TLP测试可对ESD保护器件及完整系统的接口引脚执行。 根据产生的TLP曲线,我们可以总结出哪个保护器件适合用来安全可靠地保护产品。

基本系统高效ESD设计

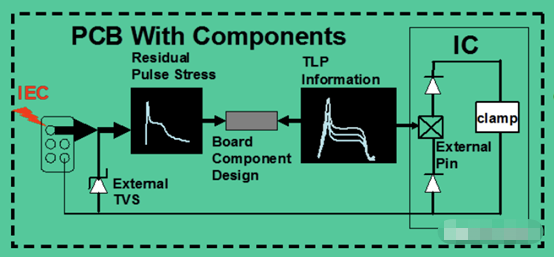

下图显示了基于TLP行为模型的基本系统高效ESD设计建模(仿真)。

扩展系统高效ESD设计

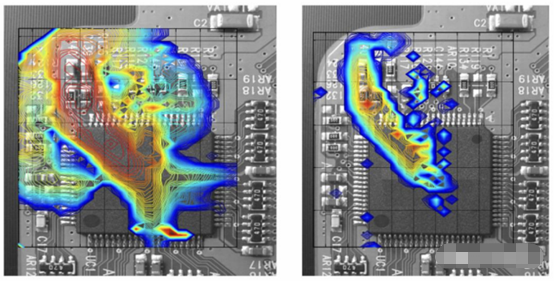

如果EM(Electro magnetic 电磁)扫描工具可以使用,则如下图所示EMC设计方法扩展系统高效ESD设计。 其可以覆盖由于低注入电流及电磁辐射等其它电磁问题造成的软故障。

系统级与元件级ESD脉冲

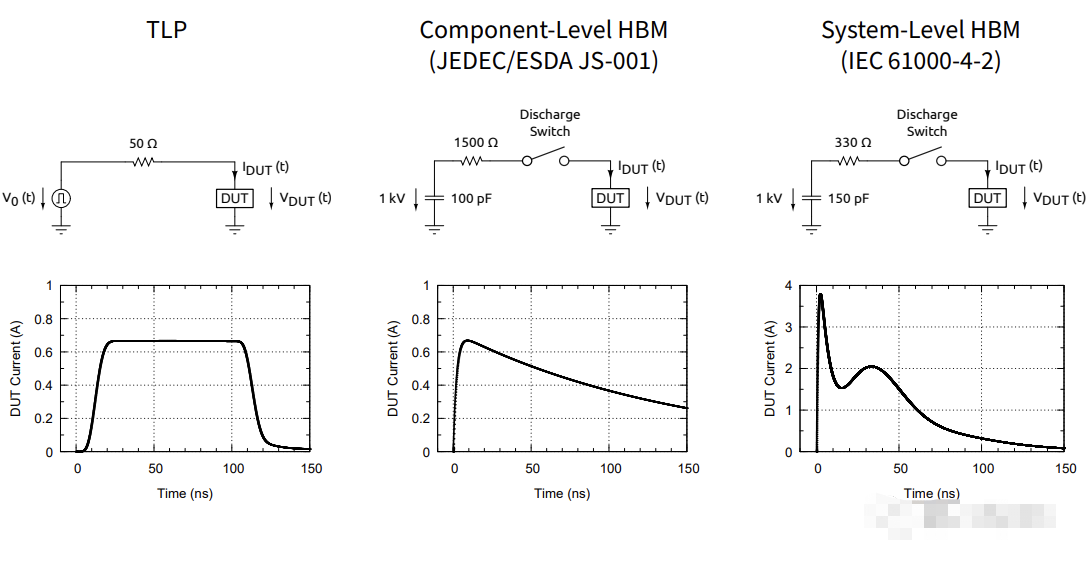

TLP(传输线脉冲),

器件级别人体放电模型component-level HBM (JEDEC/ESDA JS-001),

系统级别人体放电模型system-level HBM (IEC 61000-4-2),

电流脉冲波形图示如下。

图中显示三种脉冲有着完全不同脉冲源阻抗,但是其电流脉冲(波形)有着相似的上升时间和持续时间。 所以TLP传输线脉冲行为模型很有用,因为它具有类似于系统级别人体放电模型IEC 61000-4-2 ESD冲击的特征。 所以TLP不止用于表征器件完整接口特性,也用于表征ESD保护组件的特性。

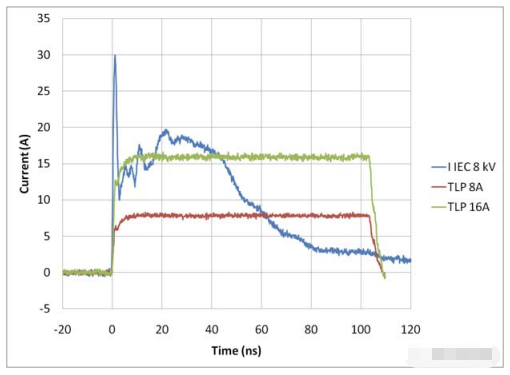

下图把IEC 61000-4-2 8KV电流波形与TLP 8A及16A电流波形放在同一坐标图中,则凸显了TLP的上升时间及持续时间与系统级别人体放电模型的相似性。 实际上对应于芯片内部或外部ESD保护器件的作用时间及耗散能量。

因此,甚至有人在工程估算中将TLP电流与IEC ESD相关联:

2kV IEC 冲击 = 4A TLP。

4kV IEC 冲击 = 8A TLP。

6kV IEC 冲击 = 12A TLP。

8kV IEC 冲击 = 16A TLP。

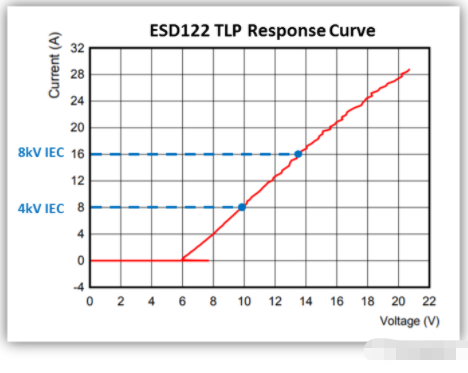

有了这些信息,可以从下图器件ESD122 TLP响应曲线推断,在8kV IEC 61000-4-2 ESD冲击期间,器件ESD122将具有约13.5V的钳位电压。 换句话说,当8kV IEC冲击发生时,您可以预期后续电路暴露在13.5V下约100ns。

ESD工程估算设计举例

下面例子摘抄于TI网站威廉希尔官方网站 博文。

需求:

选择一个合适的ESD二极管来保护在19V传输线脉冲(TLP)下失效的USB2.0系统。

选择过程:

USB 2.0差分信号的电压范围约为0至3.6V,因此您要确保器件的VRWM大于等于3.6V。

USB 2.0带宽最高可达480Mbps,因此您需要选择具有适当电容的器件来保持信号完整性。

您需要满足IEC 61000-4-2 4级法规,因此ESD二极管必须额定至少支持8kV接触放电和15kV气隙放电。

16A TLP的ESD二极管的钳位电压必须小于19V,因为系统将在19V时失效。

解决方案:

器件TPD1E04U04是一个很好的解决方案,因为它满足如下所有这些要求。

这是一个单向ESD二极管,其VRWM为3.6V。

它具有0.5pF的低电容。

它支持IEC 61000-4-2额定值16KV接触和16kV气隙放电。

在16A TLP脉冲下,钳位电压为9V。

尽管在许多器件规格书中没能找到TLP失效电压,但这个例子基本上给出了一些ESD防护器件选择原理,特别是假设器件厂家给出这一数值情况下。 或是采用绝对最大电压限制值作为设计输入,尽管这样会过设计。

许多器件仅包含器件级别HBM和CDM模型标准ESD额定电压值,但这些数值仅仅能够工程估算TLP失效电流,不能完全描述器件内部ESD防护特性。

总结

简单介绍系统高效ESD设计。

-

ESD

+关注

关注

49文章

2031浏览量

172990 -

pcb

+关注

关注

4319文章

23099浏览量

397856 -

MOSFET

+关注

关注

147文章

7164浏览量

213278 -

保护器件

+关注

关注

1文章

308浏览量

13400 -

静电放电

+关注

关注

3文章

287浏览量

44656

发布评论请先 登录

相关推荐

采用有源RFID的仓库管理系统设计方案

USB 2.0高速端口的ESD保护设计方案

SERDES在数字系统中高效时钟设计方案

静电放电(ESD)最佳设计方案资料下载

系统高效ESD设计方案

系统高效ESD设计方案

评论