在本博文中,我想说一下PRU-ICSS的另一个应用,即帮助把您选择的数字位置编码器主接口集成入Sitara处理器内。

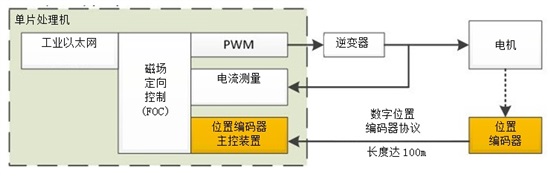

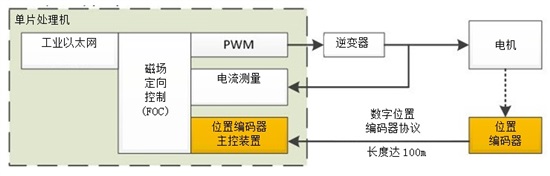

首先,让我们来看下包含位置编码器的系统层面方块图——见图1。诸如伺服驱动器等应用通常都配有集成了数字位置反馈编码器的电机。位置编码作为传感器,能够精准测量电机轴的角度(以度为单位)或线性轴(以微米为单位)的距离。

在该等系统中,位置编码器负责读取电机轴的角度,并通过数字位置编码器协议将信息提供给位置编码器主控装置。应用处理器的磁场定向控制(FOC)算法负责对角度进行进一步处理,包括电机相电流测量,以计算脉冲宽度调制(PWM)外设的新值。

图1:带位置编码器主接口的集成伺服驱动器

位置编码器和位置编码器主控装置之间的距离可长达100m。数字位置编码器协议在基于RS-485的接口上运行,创建起稳健的通信通道。

跟工业以太网一样,不同的编码器供应商也开发了许多位置编码器协议标准,供您传输位置数据用。单芯片驱动器开发人员的挑战就在于根据编码器和电机供应商选择和集成正确的数字编码器协议标准。三个最常用的位置编码器协议标准为EnDat 2.2, BiSS C和高性能接口数字舵机链接(HIPERFACE)DSL。

让我们来看下这三个位置编码器协议标准的历史和特点。

EnDat 2.2:EnDat接口是由德国公司Heindenhain开发出的产品,EnDat的最初版本使用的是interwetten与威廉的赔率体系 接口信号。随着EnDat 2.2的推出,编码器接口变为数字双向接口,适用于增量型和绝对型编码器,使用RS-485差分信号传输标准。EnDAT使用两种差分信号传输位置数据:时钟(单向)和数据(双向)。在EnDat主控设备和编码器装置间建立通信需要六根线,包括编码器供电线。

HIPERFACE DSL:另一家德国公司西克开发出了HIPERFACE DSL,其使用RS-485差分信号传输标准。其运行频率固定为9.375MHz并支持长达100m的电缆。HIPERFACE DSL的优势在于其能够实现HIPERFACE DSL主控制装置和HIPERFACE DSL编码器装置间双向通信的双线接口。这两条线还负责为编码器供电;因此,主控制装置接口和编码器装置之间只需要两条线,能够显著减少布线成本。

BiSS C:iC-Haus于2002年开发出了开放式双向BiSS接口。BiSS接口兼容单向同步串行接口(SSI),其RS-485接口最大可支持10MHz。BiSS C标准既支持BiSS主控制装置和编码器装置之间的点对点配置,也支持多个传感器和执行器总线连接至一台BiSS主控制装置。接口包括BiSS主控制装置到编码器装置的共享时钟和控制数据(MA+/MA-)信号以及编码器装置到主控制装置的共享传感器数据和控制数据(SL+/SL–)信号。BiSS主控制装置和编码器装置之间总共有六根线,包括编码器供电线。

每个数字位置编码器协议标准传统上要求在现场可编程门阵列(FPGA)、可编程逻辑装置(PLD)或专用集成电路(ASIC)方面的具体硬件实现。然而,在通过PRU-ICSS外设将位置编码器主控制装置协议集成入Sitara处理器应用时无需外部装置组件。AM437x处理器有两个PRU-ICSS外设。您可以一个用于数据编码器主控制装置协议,如EnDAT 2.2、HIPERFACE DSL和BiSS C,另一个运行工业以太网协议。

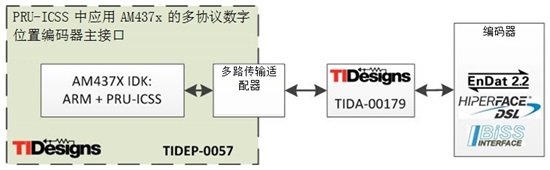

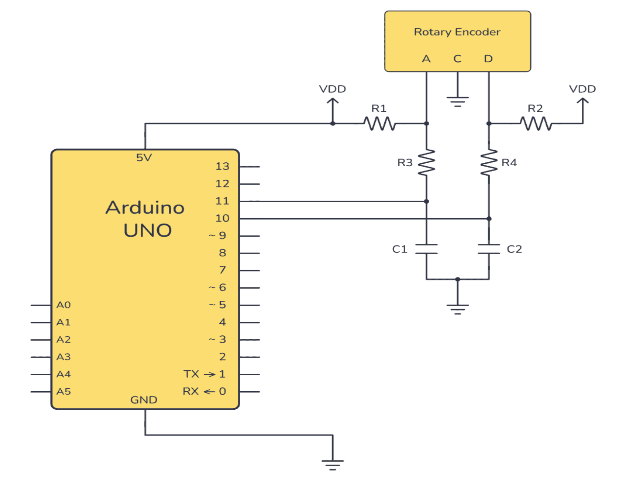

多协议位置编码器主接口已发布,见PRU-ICSS中应用AM437x的多协议数字位置编码器主接口参考设计(TIDEP0057),其中,配备PRU-ICSS外设的ARM负责检测所连接的位置编码器类型。参见图2。

图2:带PRU-ICSS的多协议位置编码器主接口

第二个参考设计,用于工业通信和电机控制的单芯片驱动器(TIDEP0025),集成单芯片驱动器的系统方法,如图1所示。在本参考设计中,位置编码器主接口使用EnDat 2.2,一个运行在AM437x的PRU-ICSS上,用于与位置编码器通信,而另一个PRU-ICSS用于EtherCAT从通信支持。

PRU-ICSS作为极其灵活的外设,可以集成之前在外部ASIC和FPGA中提供的复杂功能。正如本博文中提到的,Sitara处理器系列的PRU-ICSS集成了很多位置编码器协议用的位置编码器主接口,因此,能够免除该等外部组件。将配备PRU-ICSS的位置编码器主接口集成入Sitara处理器时可以节约开发板空间、组件成本并建立高性能吞吐量系统。

审核编辑:郭婷

-

传感器

+关注

关注

2550文章

51046浏览量

753142 -

编码器

+关注

关注

45文章

3639浏览量

134441 -

电机

+关注

关注

142文章

9003浏览量

145355

发布评论请先 登录

相关推荐

AM1810 Sitara ARM 微处理器

EnDat 2.2 位置编码器接口的参考设计

一个到电机位置编码器的EMC兼容接口设计

电磁兼容(EMC)标准的电机位置编码器接口讲解

符合EMC标准绝对位置编码器的通用数字接口

基于HEIDENHAIN EnDat 2.2标准针对位置或旋转编码器

数字位置编码器集成到 Sitara 处理器内部方法

绝对位置编码器的通用数字接口参考设计

如何将位置编码器主协议集成入Sitara处理器应用

如何将位置编码器主协议集成入Sitara处理器应用

评论