将多个芯片或小芯片集成到一个封装中的公司将需要解决结构和其他机械工程问题,但设计工具、新材料和互连威廉希尔官方网站 方面的差距以及专业知识的缺乏使得这些问题难以解决。

在半导体的大部分历史中,代工厂之外的人很少担心结构性问题。硅基板可以轻松支撑沉积在顶部或蚀刻掉的任何薄膜。但随着 SoC 被分解成更小的芯片,并且随着硬化的 IP 块以小芯片的形式组合在一起,不同的用例增加了可能影响可靠性的意想不到的压力。其中原因:

出于成本和尺寸原因,有机中介层被引入——它们可以定制为任何尺寸——但它们比硅中介层灵活得多,如果处理或包装不当,这会增加翘曲的可能性。

芯片或小芯片越来越多地堆叠在一起,这增加了机械应力。这些应力通常会因热量而加剧,这会导致小芯片、互连以及各种类型的填充和键合材料之间的热失配。虽然其中一些可以预先考虑,但它也可能因用例而有很大差异。

在先进的节点,衬底变薄以缩短信号必须传输的距离并降低电阻和电容。与此同时,在这些基板上钻了数以千计的孔,用于硅通孔和背面功率传输,这可能会导致在制造过程中无法检测到的微裂纹。由于这些设备以其他方式受到压力,裂纹会扩散。

MIT Technology Review Insights 刚刚发布了一份受 Synopsys 委托的报告,该报告对十多个行业的 302 名高管进行了调查。调查发现,38% 的人至少意识到并探索多芯片芯片设计,以此来产生足够的马力来满足未来的计算需求。报告还指出了一些需要解决的挑战。

“当你必须在芯片之间进行连接时,你就是在处理物理问题,”AMD 公司研究员 Gerry Talbot 在报告中说。“组件的物理尺寸、互连、层转换、封装的尺寸——所有这些都会限制你扩展小芯片之间接口的带宽。”

对于大多数其他公司而言,情况要严重得多。AMD 使用内部开发的小芯片。但是对于来自多个代工厂和供应商的小芯片,更多的交互是可能的。“你如何分解你的架构,并通过热、压力、可靠性一直进行这种假设架构分析?今天没有人提供。“这仍然是一项非常手动的工作。架构师需要决定,‘我的处理器在哪里,我的加速器在哪里,我的内存在哪里?我怎么上车?一旦你这样做并分解了你的芯片,就可以对芯片之间的热、可靠性、时序、功率等进行分析。但第一阶段仍然是手动的。”

有机中介层增加了另一个挑战。“翘曲是我们主要关注的问题之一,”日月光集团高级副总裁 Ingu Yin Chang 说。“当我们组装多个芯片时——有时在单个有机基板上组装 7 到 12 个芯片——这是我们今天面临的主要机械挑战之一。这跨越了我们通常在汇编世界中不看的非常大的格式,但现在我们必须看它。这可能是 150 x 150 的基板,这对我们来说是一个更大的挑战。”

即使在组装和包装过程中有效解决了翘曲问题,设备(或其某些部分)在现场大量使用下仍可能会翘曲。对于异构设计尤其如此,其中使用不同的材料或工艺开发小芯片,并且逻辑集中在封装的一个或多个区域中。随着这些区域的膨胀和收缩,或者封装的各个部分比其他部分升温更多,不同组件与基板或中介层之间的互连和键合上的应力会增加。

Ansys 产品营销总监 Marc Swinnen 表示:“通过这些颠簸的电流会产生一定的阻力。”“但是,如果这些连接中的一个发生故障,连接桥很窄,那么你就会通过那个小桥施加大量的能量。它变热,导致它融化。我们已经看到来自客户的interwetten与威廉的赔率体系 ,如果它熔化,其他凸点会获得更多电流,并且那些会熔化,因此您会发生级联热故障。你无法预测哪个碰撞或有多少碰撞会失败,所以你必须考虑,'如果两个或三个碰撞失败,它们将以什么模式造成最大的损害?你需要有足够的备用传导资源来为所有这些凸点输送能量,这就是你的热分析和电流分析。”

这些问题在混合键合中变得更加明显。“颠簸就像大型减震器,”proteanTecs 业务发展高级总监 Nir Sever 说。“微凸起就像小型减震器。但是混合债券没有任何减震器。没有多余的材料可以弥补这一点。即使您认为已经对所有这些问题进行了测试并且芯片已部署并正在运行数据,问题还是会出现。它正在加热、冷却并开始变形,即使是在零时间未检测到的最轻微的缺陷最终也可能导致单条线发生故障并产生错误。这是静默数据损坏的原因之一。最重要的是,该领域可能会出现其他问题,例如退化和加速老化。因此,在芯片的整个生命周期中持续对其进行监控至关重要。”

与其他方法相比,小芯片需要更多的连接。“在封装中,我们习惯于处理几千个信号连接,比电源和接地连接要多得多,因此可能只有不到 50,000 个连接,”IC 封装和产品管理组总监 John Park 说。Cadence 的跨平台解决方案。“但现在有了小芯片,你可能会面临 100,000 多个连接,这意味着需要一个自动路由器来处理这种容量。”

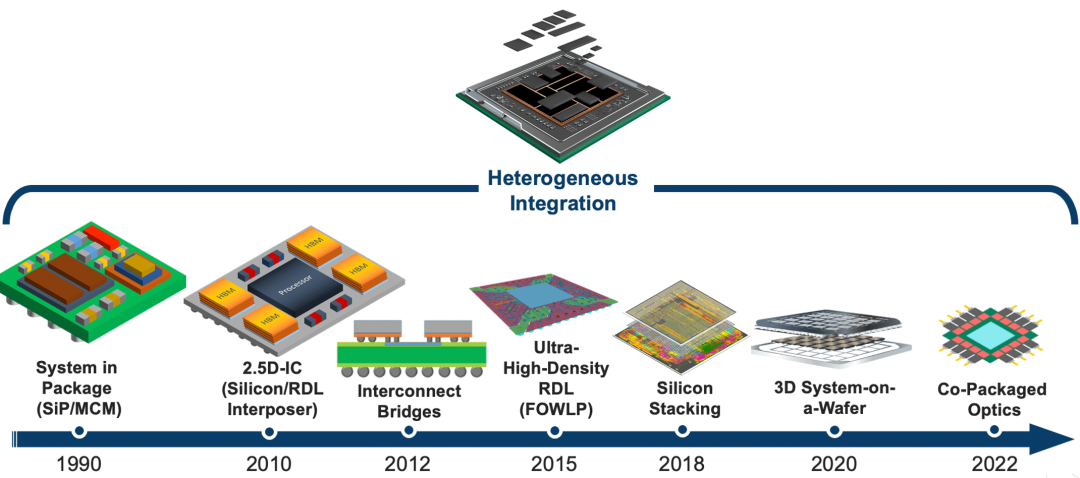

随时间变化的异构集成选项

不同的热膨胀系数增加了另一个潜在的机械应力来源,如果小芯片尺寸不同,尤其是当它们垂直堆叠时,这个问题会变得更糟。

Arm 硅运营工程研究员兼高级总监哈维尔·德拉克鲁兹 (Javier DeLaCruz) 表示:“如果您键合尺寸不同且经过预先测试的裸片,则需要用某些东西填充因裸片尺寸不匹配而造成的空间。”“但几乎所有你要添加进去的东西都会有很差的导热性。所以你会在这些区域有更大的热梯度,任何时候你有一个热梯度,你就会有额外的压力。如果导体金属发生变化,那么电迁移就会发挥作用。填充材料是新元素。传统上,我们总是不得不担心硅和带有中介层的封装基板之间的不匹配。但是在 3D 中,你需要担心引入填充材料时的硅对硅应力,所有这些都需要在设计过程的早期就加以考虑。或者,当关键组件达到特定温度时需要降低性能,以免设备烧毁。

“这取决于所涉及的功率大小以及热量的处理方式,”Amkor 高级工程师 Nathan Whitchurch 说。“如果您没有散热器,并且将所有热量向下推到电路板上,那很重要。如果您通过散热器或某些冷板设计将所有热量从顶部排出,那么您基本上没有改变热路径中的任何组件,无论您使用的是 2.5D 还是 40 层或 2 -层基板。

小芯片与软IP

当今半导体中使用的大多数 IP 都是软 IP。它通常是进程独立的,或者至少是进程弹性的。将该 IP 强化为小芯片会改变这种关系。

“强化 IP 需要经验并且可能是一个挑战,”Arm 的 DeLaCruz 说。“处理硅还需要一整套其他能力——当它集成到系统中时,产量、存储、材料处理、产量问题的所有权。如果没有很好地计划,这些都可能是乱七八糟的东西。”

所有这些元素都会影响所选封装的类型,以及何时需要在从设计到制造的流程中做出选择。

“我们必须更早地参与设计阶段。过去,您几乎完成了布局,然后问:“我们如何处理包装?” ASE 的 Chang 说。“现在的设计更加全面,因为机械应力需要与设计的其余部分同时考虑。所以现在你不仅要设计你的晶体管或核心 IP,而且你必须看看你将在小芯片布局方面拥有什么样的平面图。”

实际上,过去被描述为“左移”的东西正在变成一堆并发流程,每一步所需的数据都需要更加全面。

Siemens Digital Industries Software 威廉希尔官方网站 解决方案销售高级总监 Michael Munsey 表示:“IP 公司将不得不发展,因为他们需要提供更高水平的分析和信息来推动前进。”“如果你是一家规模较小的 IP 公司,正在做 USB 或 PCI 等零件,那将进入更大的领域。但你会看到 IP 公司推出小芯片,而这些公司确实需要不仅可以输入电气分析,还可以输入机械分析的信息,以产生集成流程。”

计算密度也只会增加,将所有这些不同的计算元素放入一个包中会使散热变得更加困难。反过来,这可能会在异构设备的其他地方引起机械应力,但并不总是在人们预期的地方发生。

“如果你有 AI 加速器,并且它的封装功率为 1 千瓦,那么系统中会产生大量热量,系统预热会产生大量机械应力,你必须考虑到这一点,”负责人 Andy Heinig 说。Fraunhofer IIS 自适应系统工程部高效电子部门的负责人。“我们需要更多的标准。也许我们还需要机械接口标准来实现小芯片生态系统。我们肯定看到了一些差距。但首先我们需要展示原型,将来自不同合作伙伴的小芯片汇集在一起,这样我们才能看到缺少的东西。chiplet 生态系统与我们在 Intel 和 AMD 方面看到的完全不同,他们在内部完成所有工作并控制一切。如果我们真的想建立一个开放的生态系统,热和机械并不完全独立。“压力会产生热量,”西门子 EDA 的 Calibre nmDRC 产品管理总监 John Ferguson 说。” 因此,应用的堆叠越多,静止温度越高。同样,当材料被加热时它们会膨胀。给定由几种不同材料组成的系统,每种材料具有不同的热系数,暴露于周期性加热和冷却最终会导致可靠性问题,例如 EMIR 影响。”

考虑到所有这些因素也会增加设计成本,这可能会限制公司处理多芯片集成的方式。

“如果我们从多个地方获得多个管芯,那么如果这些东西已经构建,您首先要看的是它们的引脚间距,”Cadence 的 Park 说。“例如,在基于 UCIe 的 die-to-die 小芯片中,有一个标准封装的选项,类似于具有 125 或 130 微米引脚间距的倒装芯片,而不是内插器上的东西间距可降至 35 微米。如果引脚间距降至 40 或 50 微米,我必须使用硅中介层或某种互连桥来做到这一点,这会增加成本。这就是为什么有些人可能会选择标准封装版本的原因,因为如果你将所有东西都放在 125 微米的倒装芯片间距上,你可以在传统的层压封装上做到这一点,这比使用硅中介层或嵌入式桥的成本要低得多。”

如果设备过早失效,成本可能会显着增加。“如果你是一家组装来自多个供应商的小芯片的公司,并且你已经完成了互连,你仍然必须集成并负责该系统的测试,”proteanTecs 的 Sever 说。“例如,如果您有四个合作伙伴,您将从他们每个人那里获得单独的测试程序,并使用他们自己的测试方法。作为 chiplet 集成商,您负责测试最终产品,当出现问题时,您需要知道原因。当单片芯片出现故障时,这是您自己的芯片,您拥有调试所需的必要信息。但是,如果您有四家不同的供应商,您怎么知道哪一家负责呢?检测到错误的芯片不一定是问题的根本原因。

定制

定制在压力方面增加了另一层复杂性。虽然从理论上讲,定制设计可以提供最大的能效和性能,但它也以独特的方式将许多部件组合在一起。在各种会议上已经讨论了第一个商业小芯片是否将是子系统而不是具有非常特定功能的单个芯片。

“与其他人做同样事情的标准接口不会使您的产品与众不同,”Synopsys IP 产品线高级组总监 Michael Posner 说。“如果你想挤出更多的性能,或者降低你的功耗,或者在界面上脱颖而出,这就是我们定制 IP 的原因。但是有了这些封装威廉希尔官方网站 ,要做到这一点变得越来越难。UCIe 被定义为标准或基于有机中介层或硅桥。因此,您必须立即牺牲凹凸坡度。即使使用标准的 UCIe 定义的 100nm 凸点间距,这还没有经过汽车级测试,但有机物上的 130nm 是汽车级的。所以你有一个标准和威廉希尔官方网站 之间不匹配的过渡区域。然后你有机械问题,那里还没有足够的数据来真正进行大量模拟——甚至那些都是基于一些理论的。我们需要更多的数据。”

与所有新方法一样,许多想法正在浮出水面。哪些坚持还有待观察。

“展望未来,热分析信息可以作为元数据存储在芯片本身上,然后传递到机械/热分析工具中以进行该级别的分析,”西门子的 Munsey 说。“当您进行电气/机械/系统级分析时,您将收集大量真正有用的数据,这些数据可以反馈到流程中。因此,我们听到了关于左移和试图左移的事情,这些事情实际上是从机械信息开始的,目的是在流程的早期和下一代产品中推动决策制定。”

这适用于小芯片以及非小芯片设计。Ferguson 说:“想想今天传统布局布线中的功率是如何优化的。”“对于每个区块,都有特定级别的预期功率要求。这有助于推动布局以满足芯片级的整体功率利用限制。3D-IC 环境中的小芯片也需要做同样的事情。这意味着对最小封装中的每个小芯片执行电热机械分析,以捕获给定热机械窗口内电气行为的公差,以及如何存储和传输此类信息的相应标准。从那里开始,随着每个小芯片被放入更大的 3D-IC 封装中,需要进行后续的热机械分析,以确定配置是否满足组件中每个小芯片放置的最低规格。当然,鉴于当前最先进的解决方案对热机械模拟的性能和容量要求,自动化仍将是一个挑战。”

结论

还不完全清楚小芯片将如何推出,或者它们将如何打包。但是在高级封装中有一个明确的异构集成方向,并且至少已经确定了很多问题,即使目前还没有解决方案。

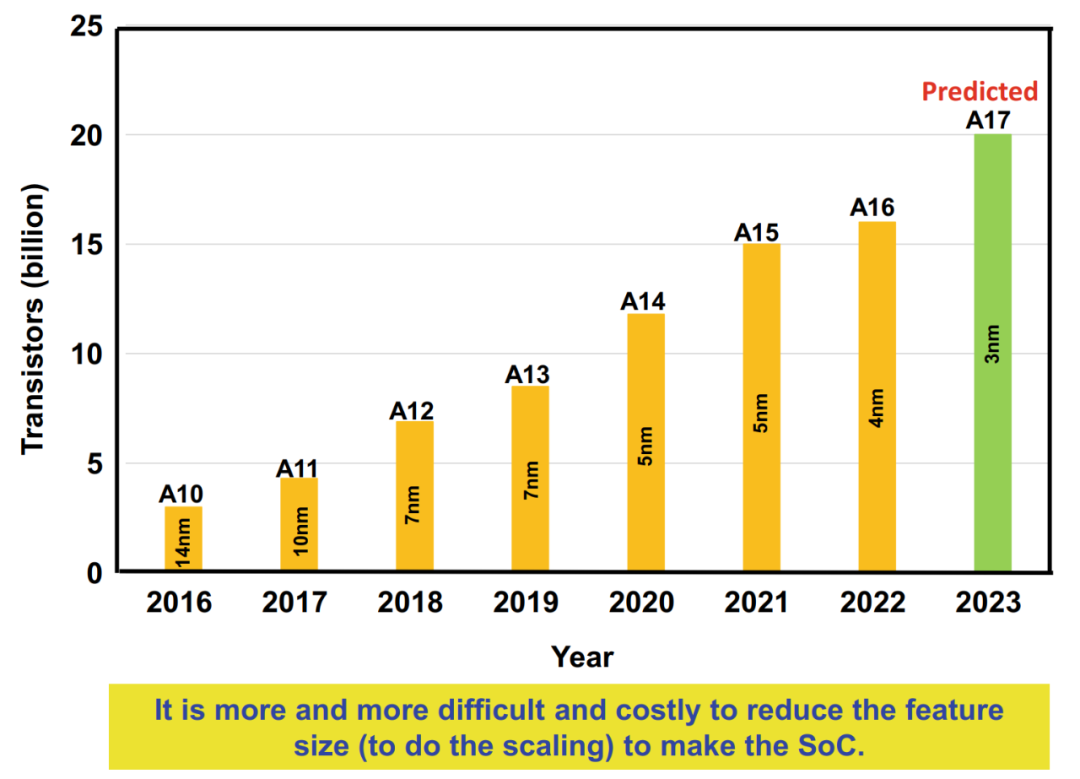

“超越摩尔定律是推动电子威廉希尔官方网站 发展的唯一途径。可能会有 2nm 或 1nm 设计,但由于成本原因,这些威廉希尔官方网站 节点的设计数量将非常有限,”Fraunhofer 的 Heinig 说。“但现在没有人想成为第一个使用来自不同供应商的小芯片构建系统的人。他们不想花费数百万美元来承担风险,了解整个供应链,了解什么是必要的,并开发第一个原型来向大家展示它是如何工作的,以及可能的障碍点是什么。他们宁愿成为第二。”

审核编辑 :李倩

-

芯片

+关注

关注

455文章

50732浏览量

423266 -

封装

+关注

关注

126文章

7881浏览量

142902 -

异构

+关注

关注

0文章

40浏览量

13105

原文标题:异构集成仍面临这一挑战!

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

7纳米工艺面临的各种挑战与解决方案

人工智能应用中的异构集成威廉希尔官方网站

【一文看懂】什么是异构计算?

异构集成封装类型详解

【⌈嵌入式机电一体化系统设计与实现⌋阅读体验】+磁力输送机系统设计的创新与挑战

三星芯片复兴之路:半导体业务飙升与HBM挑战并存

Wolfspeed德国建厂计划推迟,欧盟半导体产业面临挑战

全光网应用面临的挑战

日月光应邀出席SEMICON China异构集成(先进封装)国际会议

Cadence与Intel代工厂合作通过EMIB封装威廉希尔官方网站 实现异构集成

一文解析异构集成威廉希尔官方网站 中的封装天线

O-RAN威廉希尔官方网站 面临的的挑战

华芯邦科技开创异构集成新纪元,Chiplet异构集成威廉希尔官方网站 衍生HIM异构集成模块赋能孔科微电子新赛道

硅面临的挑战 硅以外的半导体材料选择

半大马士革集成中引入空气间隙结构面临的挑战

异构集成仍面临这一挑战!

异构集成仍面临这一挑战!

评论