SPI(串行外设接口)总线是 设计师有很多原因。SPI总线可以在高电平下运行 速度,短时传输数据速度高达 60 Mbps 距离,例如板上的芯片之间的距离。巴士是 概念简单,由一个时钟、两条数据线组成, 和芯片选择信号。由于数据在一个阶段呈现 的时钟和在相反的相位上回读,有一个 延迟和速度不匹配的余地很大。 最后,总线由单向线路组成, 简化微处理器中的实现,消除 控制流问题和与隔离 光耦合器或数字隔离器,因为隔离器是 固有的单向设备。

在工业应用中,如热能或压力 监控系统,与ADC中的通信 传感器前端不需要高采样率,并且, 因此,SPI时钟速率很高。即使是孤立的设计也很简单 在各种隔离威廉希尔官方网站 中实施,但是 需求会随着时间的推移而变化。久负盛名的 SPI 接口 已被长线应用推向极限 运行、高数据速率和隔离要求。在 本文,我们将介绍SPI总线,其约束条件以及 如何在孤立的系统中处理它们。

突破隔离式 SPI 极限的应用 性能是高动态范围传感器接口。自 创建一个具有宽动态范围的系统,设计人员会 从信噪比(SNR)良好的ADC开始, 这通常与单词长度有关;16 位是 常见于转换器。但是更高的动态范围在哪里 必需的,可以采用其他威廉希尔官方网站 ,例如变量 获得输入放大和过采样。 过采样会牺牲带宽来抑制噪声。如果 采样频率加倍,通常噪声 性能提高了 3 dB。例如,75× 过采样率将改善噪声 性能和动态范围约为 18 dB。A 75× 信号过采样意味着ADC在 900 kSPS 将提供 18 dB 更好的动态范围,大约 带宽为 6 kHz。带宽和动态范围可以 当然需要权衡,但最终,将 ADC 作为 越快越好,好处越大。这意味着 SPI 总线将不得不跟上这种雪崩式的数据。让我们 使用用于 高采样速率应用,例如ADI AD7985脉冲星ADC,其运行速率可达2.5 MSPS,并了解如何 通过 SPI 总线与其通信会影响 信号链。

模数转换器接口

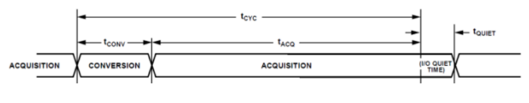

典型的模数转换器处理两个数据 基本操作如图 1 所示。首先,ADC具有一个 转换周期 (t卷积) 通过其内部的位置 创建表示电压的数字字的过程 在其输入。其次,ADC传输采集的数据 在 采集时间(tACQ).ADC 通常具有 最短循环时间(t中青) 才能启动另一个 转换,大约是 t 的总和卷积和 tACQ但可以是 当ADC具有特殊的传输模式时,时间较短,允许 收购和转让重叠。为简单起见,以下内容 讨论将基于顺序转换和 收购。

图1.简单的ADC传输序列。

转换时间和最小循环时间相同 无论数据如何传输。但收购 时间取决于数据接口的属性,在大多数情况下 SPI总线的操作案例。如果采集时间是 由于SPI上的时钟速率而延长,采样速率 ADC可能会受到严重限制。

SPI 时钟速率限制

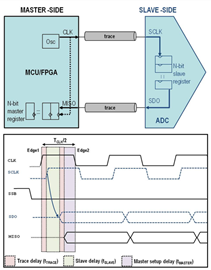

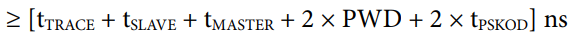

微处理器/FPGA (MCU) 和 ADC如图2所示。SPI 总线由 一对移位寄存器之间的连接,一个在 主MCU和从属ADC中的一个。单片机提供 同步传输的时钟。时钟的一个边缘 将数据移出移位寄存器和互补 边缘时钟已呈现到另一个中的数据 环形拓扑中每个移位寄存器的结束。在 ADC,可能不需要从MCU转移数据 到ADC,因此该通道已被消除 简单以及从属选择。ADC 填充其 在转换工作阶段内部移位寄存器,然后在采集期间移出寄存器 阶段。

图2.ADC SPI通信模块/时序图

在SPI事务中,时钟信号由 主站通过一些接线延迟传输到从站,其中 它触发从站在某些内部数据后移出其数据 延迟。数据信号再次传回主站 通过接线延迟,它必须到达主站 时钟互补边缘的时间。大师 通常有一些额外的设置时间要求 这一行。此时序如图 2 所示,它显示了 这些延迟确定了一半 主时钟周期。在非隔离系统中,这些时间是 通常非常短,在大多数情况下<10 nS,并允许SPI 时钟以超过 50 MHz 的速度运行。

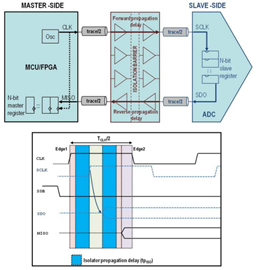

如果将隔离栅添加到SPI数据路径,如图所示 在图 3 中,它添加了类似于跟踪延迟的项。然而 根据用于隔离的威廉希尔官方网站 ,信号 传播延迟(prop延迟,TP.ISO) 通过隔离 可以超过 100 nS。图 3 还显示了如何 一组延迟时间延长了数据所需的时间 交易并显着增加半期 SPI 时钟。隔离延迟主导所有其他时间 系统中的延迟和最大时钟频率可以 降至几兆赫。

图3.隔离式ADC SPI通信模块/时序图。

时钟周期的主要约束是 要求数据及时存在于主服务器上 下一个时钟边沿。在非隔离系统中,这并不算什么 约束,它实际上增加了数据的健壮性 通过允许慷慨的时序裕量进行转移。然而 一旦数据路径的传播延迟开始 主导半期,严重退化最大值 巴士的速度。

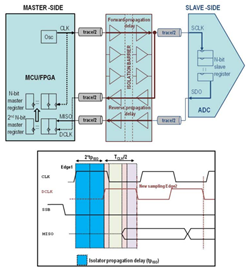

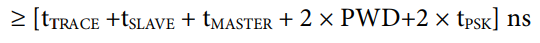

幸运的是,有一种方法可以绕过此限制。如果数据 从奴隶返回有一个独立的时钟 与之同步,可以有一个单独的接收移位寄存器 在MCU中设置以接受基于独立数据的数据 时钟。在这种情况下,SPI 总线的吞吐量不再 受隔离栅传播延迟的限制,但 通过隔离器的吞吐量。

独立时钟DCLK可通过以下方式轻松创建: 向隔离器添加匹配的高速数据通道 并沿匹配的 SPI 时钟发送隔离 SPI 时钟的副本 包含来自ADC的数据的数据路径,如图4所示。 此方法确实需要额外的硬件 隔离屏障;一个额外的隔离通道和一个 MCU中的独立时钟移位寄存器。单片机 从辅助接收寄存器读取数据,而不是 标准 SPI 寄存器。

图4.创建独立数据时钟的隔离系统。

为了说明如何植入这种数据传输方法 在不同的威廉希尔官方网站 中,以下三个例子是 定量检查最大速度,以及 定性功耗和所需电路板 空间。我们将看到,在标准隔离SPI中,它 是限制速度的往返传播延迟,以及 在延迟时钟方案中,它是时序偏差和 设置限值的隔离器失真。

光耦合器实现

在典型的工业应用中,单通道数字 光耦合器常用于高速隔离 巴士。需要四个光耦合器来隔离一个标准 4线SPI总线。时序参数在 估计常用工业中的最大SPI时钟速度 CMOS光耦合器有:

最大数据速率为 12.5 Mbps 或最小 脉冲宽度为 80 ns。

最大传播延迟(吨.ISO) 的 40 ns。

最大脉冲宽度失真 (PWD) 为 8 ns。

最大器件间传播延迟偏斜 (吨PSK) 的 20 ns。此参数很重要,因为 多个光耦合器用于创建 隔离式SPI总线。

为了估计SPI吞吐量,我们假设一些典型的 图 3 中不同组件的延迟。每条迹线 假设延迟为 0.25 ns,相当于总迹线 延迟 (t跟踪) 的 1 ns。类似地,从机延迟(t奴隶) 和 主设置延迟 (t主人) 假定为 3 ns 和 2 ns 分别。

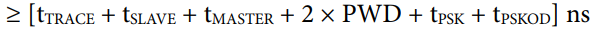

因此,从我们对隔离式SPI时钟速率的讨论来看,在 图3所示,对于使用上述光耦合器隔离的SPI总线, SPI 时钟周期的一半将是

或 86 ns—导致 SPI 时钟速率为 5.75 MHz 或 速度较慢,并明确表示 2 × TP.ISO大大 减慢 SPI 总线速度。

现在,考虑在反向添加一个额外的隔离器 将隔离时钟信号路由回主站的方向 并实现延迟时钟,如图4所示。这 允许我们生成与返回的时钟信号同步的时钟信号 来自从属站的数据。往返传播延迟 [2 ×吨.ISO]的隔离器不再限制时钟速率。跟 系统中剩余的延迟,可以隔离SPI的一半 时钟周期≥ [t跟踪+ 吨奴隶+ 吨主人] ns或6 ns, 支持最大 80 MHz 的 SPI 时钟速率? 不幸的是,答案并不那么简单。

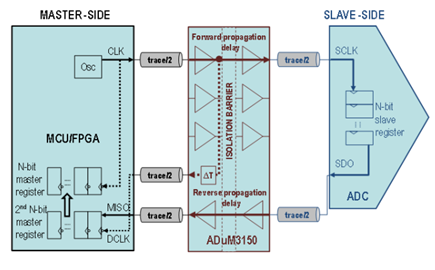

正向和反向通道中的不对称性必须仍然 计算最小SPI时钟时考虑的因素 周期如图 5 所示,为 t扭曲.传播延迟 器件之间的偏斜和脉冲宽度失真限制了 新的SPI半时钟周期至

或 62 ns。这导致实际最大时钟速率为8 MHz。但是,由于其最小脉冲宽度限制为80 ns,该光耦合器只能支持6.25 MHz的最大SPI时钟。上面的例子表明,即使光耦合器不受其最小脉冲宽度的限制,tSKEW也会将最大SPI时钟速率从可能的80 MHz(完美延迟匹配)限制在实际应用中达到6.25 MHz。

图5.实用的 DCLK 时序图。

可以使用速度更快的光耦合器,最小值更短 脉冲宽度有帮助?超高速光耦合器,具有 20 ns的最小脉冲宽度可以允许我们运行 以前的接口速率较高。但即使是这些设备 遭受较大的偏斜和失真参数。用 tPSK16 ns,PWD为2 ns,最小SPI时钟的一半 周期≥ 42 ns,从而产生最大时钟 速率为 11.75 兆赫。在上述两种情况下,时间 光耦合器的特性进一步降低 时间,从而在 延迟时钟和从数据。添加时序裕量 这些变化导致需要进一步减少 SPI 时钟速率。

使用额外的快速光耦合器进行SPI隔离, 除了非常昂贵,还需要很多板 因为这些器件通常是 SO8 中的单通道 需要软件包和 5 个通道。的功率预算 隔离接口的电流可达 20 mA 每个通道。

数字隔离器实现

在过去十年中,新一代数字隔离器 已可用。这些器件具有更高的集成度, 更高的速度、更低的传播延迟、低偏斜和更少的失真。考虑一个四通道数字隔离器—— 3 个正向通道和 1 个反向通道允许紧凑 隔离4线SPI总线。类似于光耦合器 示例,我们从以下时序参数中获取 数据表;最小脉冲宽度为 11.1 ns (90 Mbps), 最大传播延迟(tpISO) 的 32 ns,最大脉冲宽度 失真 (PWD) 为 2 ns,最大传播延迟偏斜 零件之间(tPSK) 的 10 ns。但是,与单通道不同 光耦合器,在四通道数字隔离器中,通道间 一对相反方向之间的匹配 渠道也需要考虑。在上面的部分中,这 参数 (tPSKOD) 为 5 ns。

使用与图3相同的典型延迟,即半时钟 使用数字隔离器的隔离式SPI总线的周期 应该是

或 70 ns,最大时钟为 7 MHz。就像 光耦合器案例中,我们看到SPI速率很高 受隔离器传播延迟的限制。但 数字隔离器内置标准CMOS威廉希尔官方网站 ,具有 在整个产品生命周期内具有非常稳定的时序特性。 这使我们能够在不留下太多时间的情况下设置 SPI 时钟速率 时序特性变化的余量。

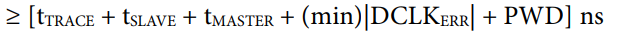

如果使用额外的隔离器通道来实现延迟 如图 4 所示的时钟,至少额外高 需要使用速度通道。再次实现 SPI 吞吐量 取决于 时钟和数据通道。鉴于所有 通道类似,新的SPI半时钟周期应该是

或 25 ns,最大时钟速率为 20 MHz。

在许多应用中,MCU仅从 ADC,不会移入任何东西。在这种3线SPI总线中, 具有2个反向通道的单个四通道数字隔离器 用于实现SPI总线和延迟时钟。在 这些情况,还有一个额外的好处。半SPI时钟 期间将是

或 20 ns,从而获得更快的最大时钟速率 25兆赫。

尽管数字隔离器的速度和偏斜 明显优于光耦合器,时序偏差 通道之间的失真仍然限制了最大值 可能的SPI时钟速率。用于延迟时钟的额外隔离器 仍然消耗大约 20% 到 25% 的功率。因此,使用 现有的隔离器将消耗更多的电源和电路板空间 同时仍然达不到最大可能的好处 方案。

优化数字隔离器延迟时钟 实现

ADI公司开发了一种数字隔离器,该隔离器经过优化,适用于 在延迟时钟中提供尽可能高的性能 方案。ADuM3150(图6)是SPI隔离器的一部分™系列高速数字隔离器旨在优化 SPI总线的隔离。ADuM3150产生延迟 时钟,DCLK,无需使用额外的隔离器通道。 DCLK 通过延迟标准 SPI 时钟产生 等于往返传播延迟的量 [2 × tpISO]通过隔离器。图 6 显示了内部 ADuM3150的框图延迟单元小心 在生产时进行修剪以匹配往返道具延迟 通过零件,从而最大限度地减少时序失配 在延迟时钟和返回从站数据之间。延迟 不匹配不仅大大减少,而且非常 在广泛的工作条件下定义良好,并且 DCLK 在数据表中保证犯 错参数。

图6.ADuM3150 SPI隔离器延迟时钟实现

DCLKERR 是延迟时钟与从站数据不同步程度的量度,因此 DCLKERR 的符号指示延迟时钟是领先还是滞后于从站数据。由于延迟时钟用于将从属数据采样到主站,因此它不应引导数据。DCLK 滞后数据是可以接受的,只要它不会完全错过数据采样位。ADuM3150数据手册对DCLKERR的规格为–3 ns至8 ns,PWD的规格为3 ns。考虑到最大超前DCLKERR和PWD,SPI时钟速率为

或 12 ns,最大时钟速率为 40 MHz。 ADuM3150, 最大数据速率为40 MHz,能够与此相匹配 高SPI时钟速率,无需任何尺寸、成本和功耗 与使用额外隔离器通道相关的处罚。

| 时钟延迟 机制 | 主要斜坡 贡献 | MAX SPI 速度 (兆赫) | 备注/评论 |

| 单通道 Opto1 tp.ISO= 40 纳秒 |

PWD = 8 ns tPSK= 20 ns |

6.25 |

• 电路板面积 大 • 高功率 • 定时特性随生命周期 变化 • 成本高 |

| 单通道 Opto2 tp.ISO= 20 纳秒 |

PWD = 2 ns tPSK= 16 ns |

11.75 |

• 电路板面积 大 • 高功率 • 高速光电器件非常昂贵 • 定时特性随生命周期 变化 • 成本非常高 |

| 数字隔离器 卫生纸.ISO= 32 ns |

PWD = 2 ns tPSK= 10 纳秒 t普斯科德= 5 ns |

25 |

• 4 线 SPI 外壳 中的中等到高电路板面积 • 高功率 • 成本适中 |

|

集成延迟 数字隔离器: ADuM3150 卫生纸.ISO= 14 ns |

PWD = 3 ns DCLK犯 错= 3 纳秒 |

40 |

• 不增加电路板面积 • 最低功耗 • 由于调整延迟 ,最小倾斜 • 特征良好的DCLKERR • 成本最低 |

结论

为了使过采样成为增加的有用工具 动态范围在传感器应用中,必须有很高 与目标频率相比,采样频率的倍增器足以提供显著的噪声 减少。此处介绍的延迟时钟方案 提供了提高隔离吞吐量的途径 SPI接口,提高采样率。此方法将 在可用范围内提升最大SPI时钟速率 隔离威廉希尔官方网站 。数字隔离威廉希尔官方网站 与旧式光耦合器相比具有显著优势 由于严格控制通道之间的偏斜和 信号链中的其他失真。ADI公司已经采取了这个 威廉希尔官方网站 进一步优化SPI专用隔离器, ADuM3150,提供低偏斜集成延迟时钟 功能无开销和功耗 较旧的威廉希尔官方网站 和方法。这将启用示例 与快速 ADC 配合使用时,速率高达 1 MSPS,通过 允许通过隔离的高达 40 MHz 的数据传输 SPI 端口。ADuM3150是SPI专用系列产品的一部分 数字隔离器,可提高与高 通道数 ADuM3151/ADuM3152/ADuM3153 作为ADuM3154的附加功能,支持 多个隔离的从站。

审核编辑:郭婷

-

接口

+关注

关注

33文章

8582浏览量

151072 -

adc

+关注

关注

98文章

6497浏览量

544524 -

SPI

+关注

关注

17文章

1706浏览量

91539

发布评论请先 登录

相关推荐

MEMS传感器的静止带宽测试

高带宽和快速故障响应电流传感器IC ACS709

简析电量隔离传感器的检测系统

日置推出新的高精度电流和高带宽传感器

高带宽传感器的SPI隔离

用于高带宽传感器的隔离SPI

用于高带宽传感器的隔离SPI

评论