前言

InFO(Integrated-FanOut-Wafer-Level-Package)能够提供多芯片垂直堆叠封装的能力,它通过RDL层,将芯片的IO连接扇出扩展到Die的投影面积之外,增加了bump的放置灵活性和IO数量。与CoWoS-S相比,既减少了硅制造成本,又通过异构集成获得了性能的提升,以及更小的体积。

在InFO封装设计中,其主要的难点在RDL自动化布线的实现,如何做到高效、DRC-clean以及高质量(电气、可靠性)实现?

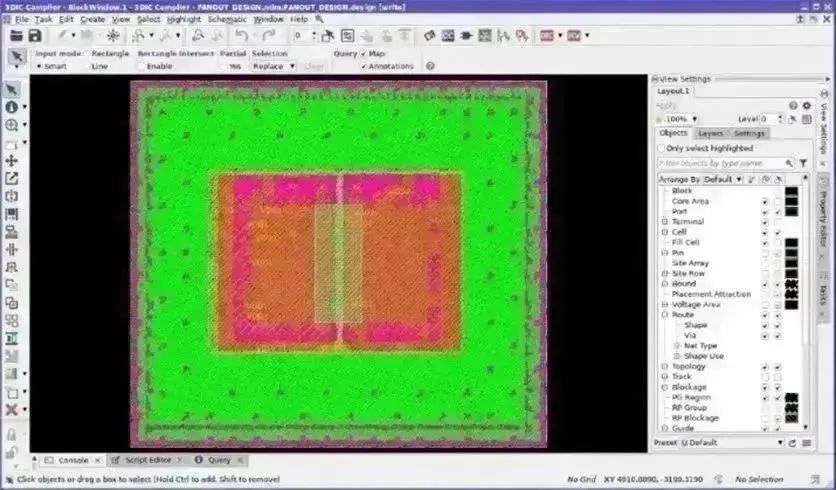

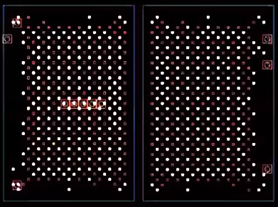

图 1

InFO_3D封装

芯和半导体的3DICCompiler(以下简称“3DICC”)设计平台,全面支持2.5D/3D chiplets集成设计和仿真。

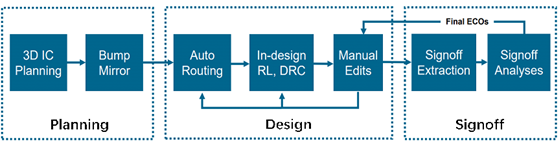

本文介绍如何基于3DICC设计平台实现Fanout集成方式的布局布线,整个流程包含芯片创建、顶层创建、FanOut substrate创建和实现,以及系统规则检查和dummy填充、degassing hole添加,如下:

图2

FanOut设计流程

案例介绍

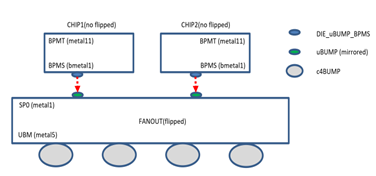

图 3

FanOut示例

1. 创建芯片模型,读入设计数据

首先,我们需要为每个芯片创建一个基本模型。为die定义floorplan的boundary,然后读入CSV文件,建立front-side的microbump pattern,这些microbump将与fanout substrate连接。

如下图:

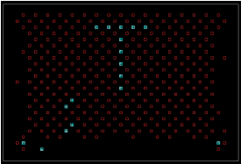

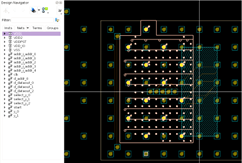

图4

(a)Die1 bump arrary (b) die2 bump array

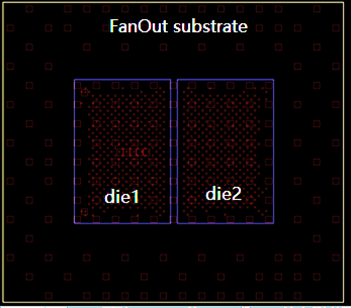

2. 创建FanOut substrate

读入C4 bump的CSV文件,建立仅包含boundary信息的substrate floorplan。

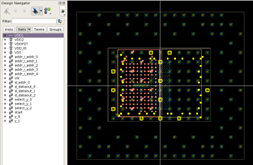

图5

(a)FanOut substrate boundary

(b) FanOut substrate的C4 bump阵列

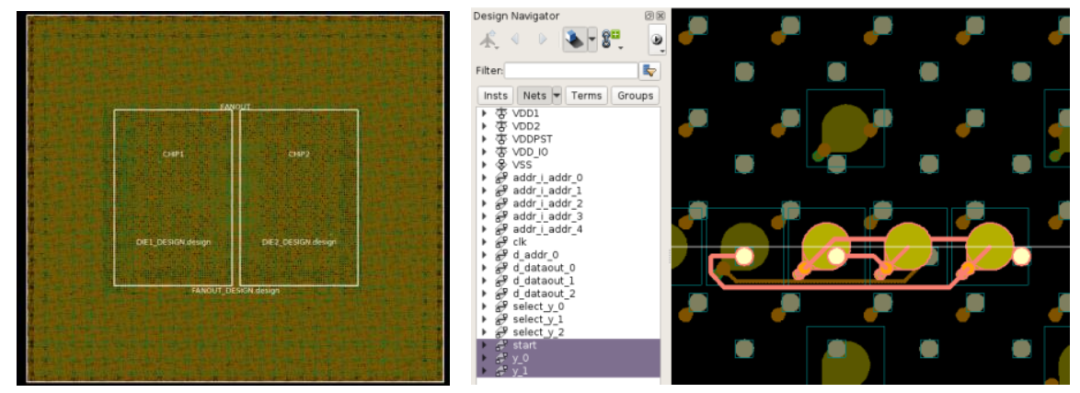

3.创建系统顶层

1)读入两个top die和substrate的NDM库,进行布局放置。

图6

FanOut设计顶层创建

2)Microbump镜像创建。通过3DICC的bump mirroring功能,将top die的microbump阵列镜像到substrate上,自动创建对接的microbump阵列。

图7

top dies的bump镜像实现

3)基于顶层netlist和镜像后的bump阵列,自动追溯芯片间和芯片与封装基板间的互连关系,创建substrate的netlist和所有互连通道和映射关系,完成top level系统建立。

图8

系统互连的自动创建

4.Fanout substrate自动布线

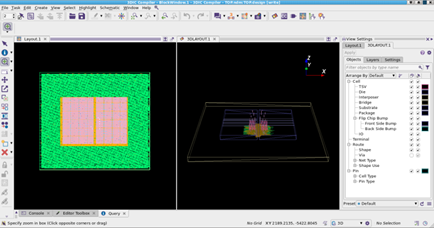

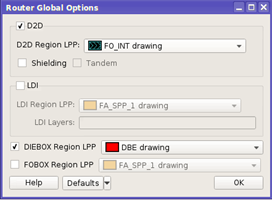

RDL substrate的自动布线将通过3DICC的add-on Custom Compiler进行。在进行布线之前,定义可调用的PDK库,其中包含定制的各种特殊图形PCell,如椭圆形、长方形等。点击OK后,系统将把这个库添加进入lib.defs文件中。另外,在版图编辑器中选择Packaging > Router Global Options,在Router Global Options中设定如下,完成自动布线器的全局规则设定。

图9

PDK库和自动布线全局规则设定

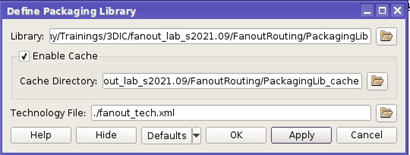

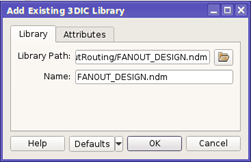

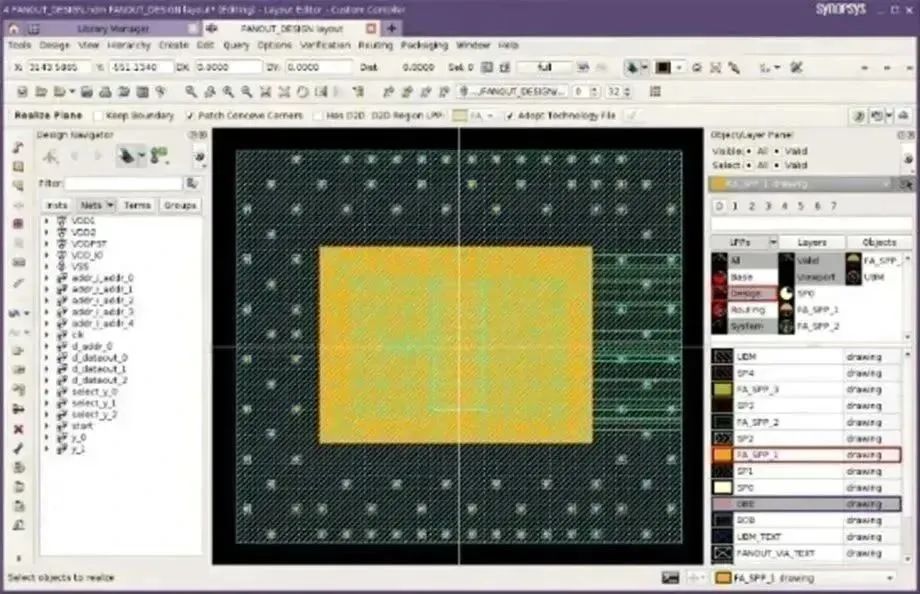

1)打开3DICC设计库,导入顶层设计版图。

图10

顶层设计版图

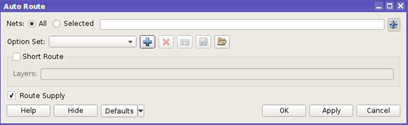

2)多层任意角度自动布线。

在Hierarchy工具栏设定stop level(可见的level深度)为1,使得布线器可以看到层次化设计中的pins和blockages。在Packaging > Auto Route中设定如下:

图11

布线设定

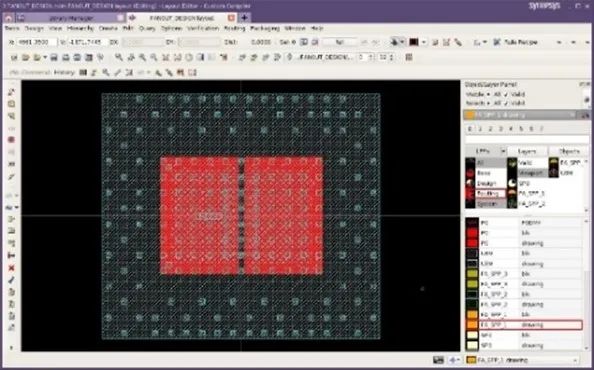

完成布线后,回到top view的结果如下:

图12

多层自动布线

3)PG平面创建。

设定用于PG平面创建的nets和布线层,如下:

| Nets | PG Plane layers |

| VDD1, VDD2, VDDPST | FA_SPP_1 |

| VDD_IO | FA_SPP_3 |

| VSS | FA_SPP_2 |

为VDD1创建PG平面边界。在Object/Layer Panel选择FA_SPP_1 drawing LPP。选择Packaging > Create Plane Boundary,在Create Plane Boundary工具栏,键入VDD1到Nets栏,在版图上用FA_SPP_1层画一个矩形区域,将VDD1 bumps/pins覆盖住。

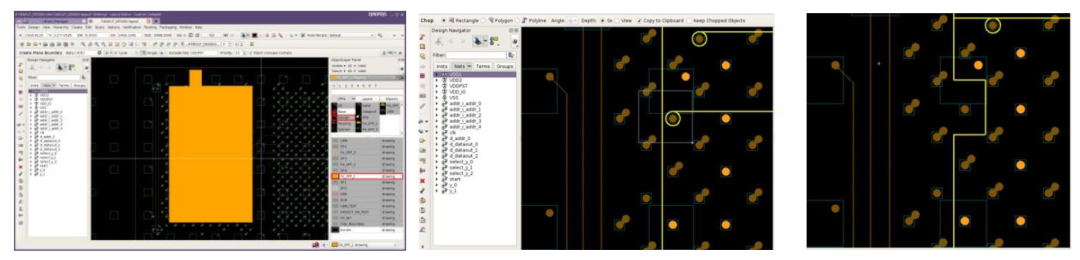

图13

VDD1平面边界创建

新创建的平面边界将目标网络和目标LPP信息存储为属性,这些属性将被布线器使用。接下来,重复以上步骤,为所有PG网络创建平面边界。

4)调整PG平面边界

检查各个PG平面边界中是否有将其他电源域的pin或者net包覆进来,如有,则进行平面调整,避免引起短路或开路。如下图中,可以看到VDDPST(黄色亮点)的bump也被VDD1平面边界覆盖。由于VDD1、VDD2、VDDPST共享同一层FA_SPP_1,为了确保不造成任何开路或短路,必需对平面边界进行调整。

图14

初版PG平面边界

在Object/Layer Panel选择FA_SPP_1 drawing LPP,关闭除FA_SPP_1 和border drawing之外的所有可视层。在Design Navigator选择VDD1.该net被highlight出来。选择Packaging > Create Plane Boundary。其中仍然被包覆的其他bump(黄色高亮的VDDPST)可以通过继续切割进行处理。

图15

VDD1 PG平面边界调整

继续进行VDD2和VDDPST的平面边界调整。结果如下:

图16

VDD2和VDDPST PG平面边界调整

接下来,在Object/Layer Panel中使所有LPP层可视可选,Edit > Select > By LPP中选择border drawing。到Packaging > Realize Plane。执行结果如下:

图17

PG平面边界调整结果

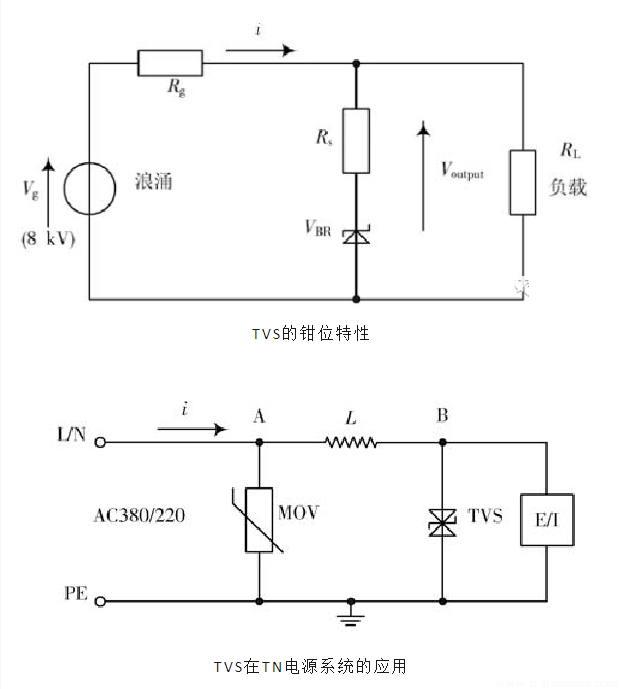

5.布线结果检查,dummy fill,de-gassing hole添加

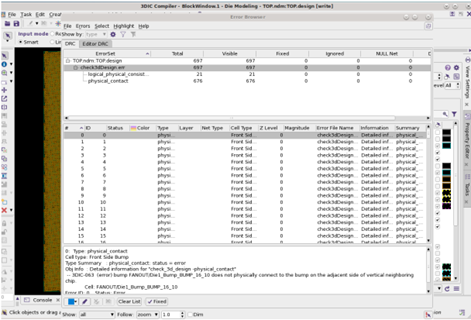

布线完成后,进行top-level的3D rule检查和基于ICV的DRC、LVS、dummy fill和degassing hole创建等。

ICV的检查结果可以在错误窗口进行查看,分为几种类型:物理连接,匹配类型,逻辑物理一致性,bump cluster,芯片布局摆放,物理设计规则等。

图18

ICV检查结果

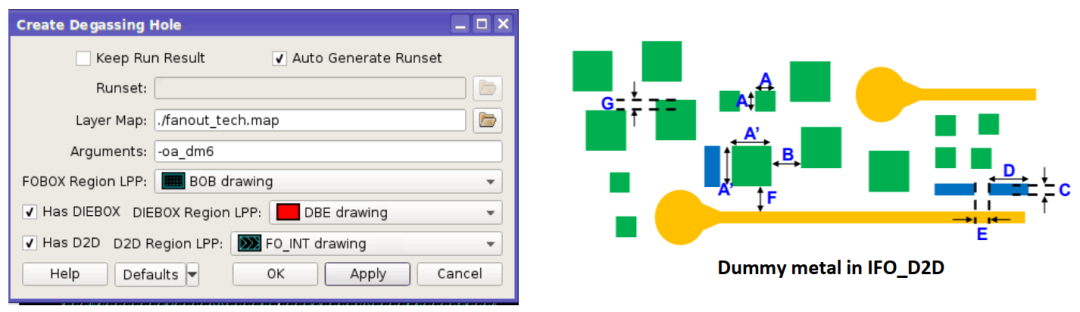

打开Packaging > Create DeGassing Hole,选择如下:

图19

de-gassing hole and dummy fill

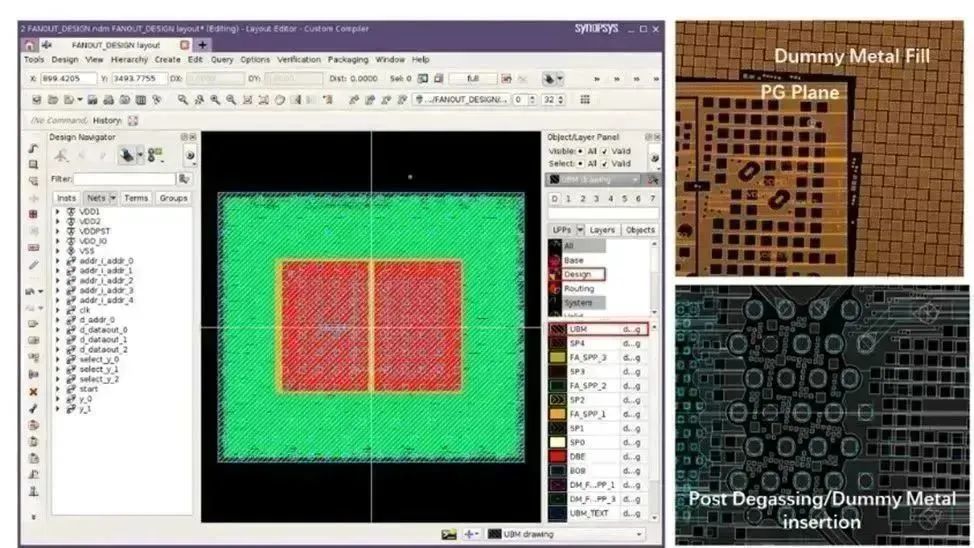

生成设计的GDS,运行ICV来生成de-gassing holes和dummy fills,将de-gassing holes导入到当前设计中,代替PG平面。当操作结束以后,degassing holes被创建完成,版图展示如下:

图20

post de-gassing hole and dummy layout

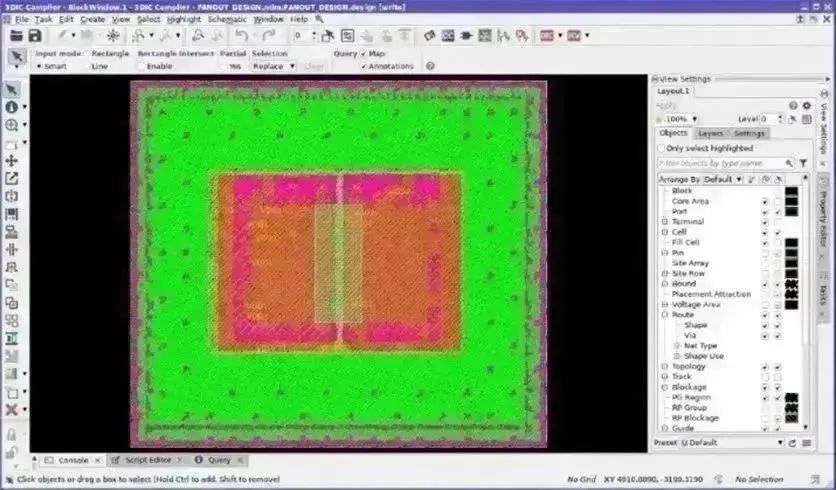

6.同步顶层设计

使用Custom Compiler完成InFO布线和编辑后,在3DICC中直接打开编辑过的设计,Tools > Digital Implementation > 3DIC Compiler,完成设计的同步更新。

图21

最终版图结果

总结

3DIC Compiler可以帮助设计者实现InFO封装物理设计和分析,能够达到高度自动化(可以将数周的实现时间压缩到几小时),具有可定制substrate、高容量、高性能等特点。并且和芯片设计数据在统一平台上完全同步,实现芯片-封装协同设计。

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50731浏览量

423195 -

封装

+关注

关注

126文章

7881浏览量

142901 -

布线

+关注

关注

9文章

771浏览量

84322 -

info

+关注

关注

0文章

11浏览量

10175 -

芯和半导体

+关注

关注

0文章

103浏览量

31416

原文标题:【应用案例】如何基于3DICC实现InFO布局布线设计

文章出处:【微信号:Xpeedic,微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Vivado之实现布局布线流程介绍

求助,关于模拟电路的PCB布线及布局问题求解

谷歌Tensor G5芯片转投台积电3nm与InFO封装

高速ADC PCB布局布线技巧分享

FPGA布局布线的可行性 FPGA布局布线失败怎么办

如何基于3DICC实现InFO布局布线设计

如何基于3DICC实现InFO布局布线设计

评论