当一个SoC芯片项目将要切入到FPGA原型验证阶段时,FPGA原型验证团队如何评估是否可以进入原型验证阶段进行新一个阶段的验证工作呢?

1. SoC代码是否成熟?

我们当然希望在项目中尽快准备好基于FPGA原型验证的代码,以便最大限度地为软件团队和RTL验证人员带来更客观的收益。然而,假如过早地开始FPGA原型验证工作,由于RTL代码在Simulation阶段验证不成熟或不充分,那么将会浪费大量的时间(因为FPGA原型验证过程中debug的难度数倍与Simulation)而只发现简单的RTL的bug,如果使用Simulation仿真,其实容易发现这些简单bug,这样原型验证的时间、技能和设备都没有得到有效利用。

所有SoC芯片项目组将在项目的各个阶段制定一份SoC验证设计。该计划的目标始终是100%验证SoC并自我确认已实现。一般包含Simulation验证计划,FPGA原型验证计划,Emulation验证计划等。一些验证团队采用高效且通用的Simulation验证方法,如UVM,主要用于System Verilog中编写的复杂测试环境,此验证计划记录了验证工程师对于相关功能测试点进行的验证,以及每个测试的当前设计状态,相关的工程师会采用收集覆盖率的方法保证基本的bug在Simulation阶段都已经验证完备了。此时整个RTL的成熟度可以认为是90%了,剩下的10%要通过FPGA原型验证或者Emulation才能保证验证完备。此时,恭喜你,可以进行ASIC代码到FPGA代码的移植工作了!

2. SoC的功能有多少可以通过FPGA原型验证平台来验证?

在早期规划阶段,我们需要确认进行FPGA原型验证的范围。当然,通常而言,团队决策者是贪心的,一般都想将整个SoC的功能都进行验证,所以有团队甚至一上来就规划几十片FPGA甚至上百片FPGA原型验证的计划,其实都不算很合理。我们需要从SoC的架构以及能实现FPGA原型验证的规模通篇考虑,因为成功搭建几十上百片FPGA的原型验证系统实属不易。

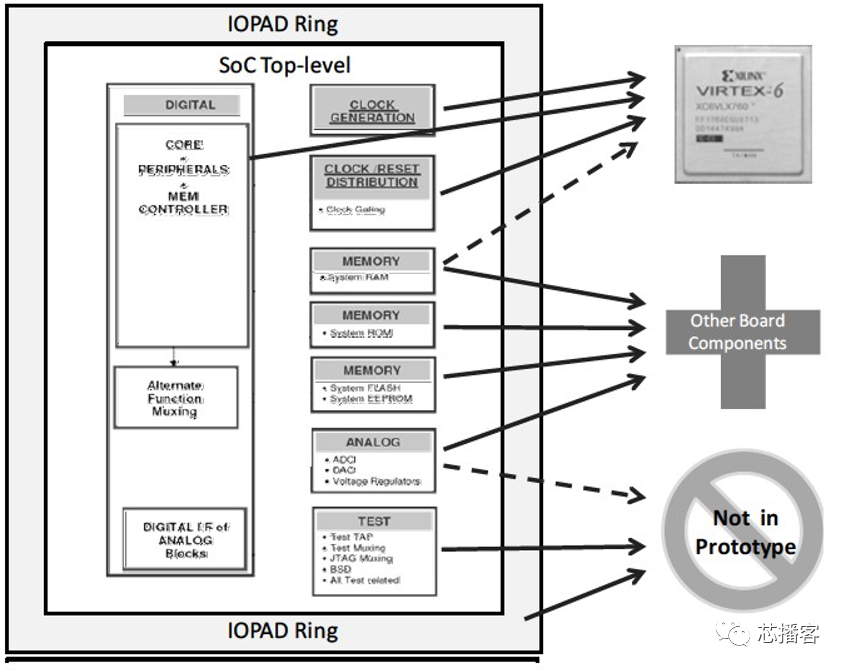

在考虑分多片FPGA原型验证系统之前,我们需要权衡哪些一定功能点相关设计一定要放在FPGA原型验证系统中,哪些功能点可以放在其他片外或者Emulation阶段去保证,也就是在项目中通常所说的“阉割”版本的FPGA原型验证系统,不管是规模还是功能,都建议从小到大,由简到难的顺序去做相关的移植工作,当然这样的版本不宜太多。简单来讲:哪些可以进入FPGA原型验证来做,哪些不能进入FPGA原型验证来做。

对于给定的平台,较小的设计通常以更快的时钟速率运行,并且比较大的设计花费更少的时间来处理。因此,我们应该谨慎地将更多的SoC设计纳入到原型中。我们可以通过哪些方式减少原型的规模,而不会过度降低其有用性或准确性?

为了减小设计尺寸并缓解容量限制,可以考虑以下选项:

永久性逻辑移除:当SoC设计中的块具有可添加到FPGA平台的硬件等效物(物理SoC、评估平台等)时,它是从将映射到FPGA的逻辑中移除的好候选。除了节省空间外,这些块可以以比FPGA平台中可达到的速度更快的速度运行。此类块的典型示例是第三方IP,例如处理器或专用控制器。

临时逻辑“阉割”:当逻辑量超过FPGA平台中的可行空间时,可以考虑临时移除一些块。当SoC的一部分可以被原型化时,这可以起作用。例如,如果一个SoC有多个可能的内存接口,但实际应用中只使用一个,那么一次一个地对它们进行原型化,而其他的则被移除,这将单独验证每一个。

整体功能缩放:当SoC中的块大小将超过整个FPGA平台中的可用可行空间时,可以考虑缩小它们。例如,SoC存储器块可按比例缩小以在任何给定时间运行代码的子集,或者可替代地,多通道设计的一个通道可能足以代表用于原型化通道驱动器软件的足够功能。

3. 评估配合FPGA完成相关功能的外接设备卡

虽然FPGA原型验证平台中,主要起作用的一定是这个系统中最主要的FPGA,但是,现代SoC中的功能非常丰富,单纯的FPGA资源一般不能完全满足SoC的验证需求,所以要考虑外接设备卡进行整系统的验证。

一般情况下,出于评估目的,SoC芯片的IP供应商通常提供在在FPGA上可实现的IP,以供客户进行FPGA原型验证。在其他情况下,项目组的FPGA原型团队可以设计或者构建功能上等同于未映射到FPGA的IP块的电路板,当然现今的FPGA原型验证供应商会提供各种类型的功能子卡。为了适应这些外部硬件选项,我们需要验证/执行以下操作:

a. 在RTL中提供与FPGA外部模块的连接。

b. 确保FPGA和外部硬件模块之间的IO的信号级别彼此兼容。

c. 确保外部硬件的信号完整性可被FPGA和硬件模块接受。典型的FPGA 的IO有许多选项,如信号电平、速度以及驱动强度。我们应该熟悉这些选项,以及如何在特定的原型环境中最佳地使用它们。

d. 提供所需的时钟,考虑时钟延迟,能够计算FPGA系统和外部硬件之间的互连定时。

e. 固定硬件的启动时间可能比FPGA系统启动时间短得多,因为FPGA需要在开始工作之前加载。早期启动可能导致硬件模块和FPGA系统之间的同步问题。

f. 外部硬件模块如何物理连接到FPGA系统,以及如何供电。必须注意布线和与FPGA系统的重复连接,以保护FPGA和硬件模块。当需要将原型运送到远程实验室或客户时,一个好的机械计划将使其更容易。

审核编辑:刘清

-

FPGA

+关注

关注

1628文章

21708浏览量

602688 -

asic

+关注

关注

34文章

1197浏览量

120390 -

soc

+关注

关注

38文章

4146浏览量

218057 -

RTL

+关注

关注

1文章

385浏览量

59746

原文标题:从SoC仿真验证到FPGA原型验证的时机

文章出处:【微信号:于博士Jacky,微信公众号:于博士Jacky】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SoC的功能有多少可以通过FPGA原型验证平台来验证?

SoC的功能有多少可以通过FPGA原型验证平台来验证?

评论