今天主要给大家简单介绍一下:PCB 上晶体振荡电路的设计。

在大部分电路中,设计晶体振荡电路是经常会遇到的。 网络上也有很多关于晶体振荡器设计的笔记,不过都是针对大规模生产,这种方法也需要投入大量的测试和不断地进行优化。

这篇文章更加适合小型的电路项目,可以帮助你设计晶体振荡器和选择合适的负载电容。

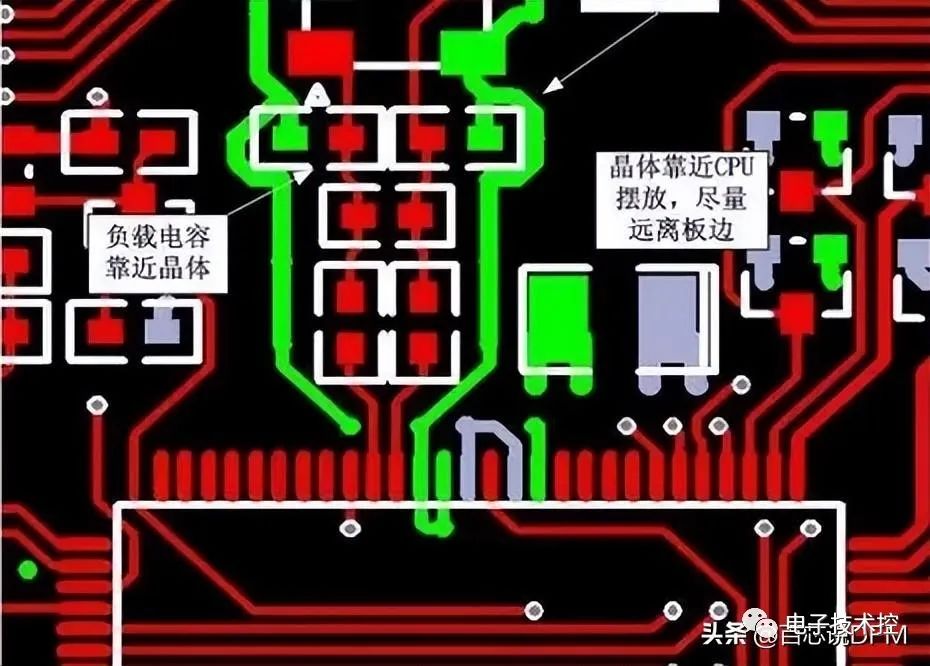

PCB 图

一、PCB上 晶体振荡电路设计步骤

这里主要有 4个简单的步骤:

1、选择晶体振荡器

选择晶体振荡器需要考虑到以下3 个因素:

可拉性与功耗

振荡器对频率变化的功耗启动时间与封装尺寸

上电后达到稳定振荡所需要的时间成本

1) 可拉性与功耗

一般来说,拉力低的晶体振荡器需要较大的负载。 每个振荡周期都必须要释放电容的能力,因此更大的负载电容意味着更高的功耗损耗。

很多微控制器的 datasheet 中都会有推荐负载电容的最大值,这样的话可以减低驱动电路中的功耗。

2) 振荡器对频率变化的功耗启动时间与封装尺寸

较小的晶体振荡器封装具有较大的 ESR ,较大的 ESR 会提供较大的临界增益(gm_crit),从而降低增益宽=裕度。

增益裕度降低意味着晶体需要更长的时间才能启动。

3) 上电后达到稳定振荡所需要的时间成本

其实很多时候性能和成本并不是强关联,如果在满足性能下,可以选择成本相对较低的晶体振荡器。

2、检查微控制器是否可以驱动晶体振荡器

通常来微控制器的 datasheet 中会提供一些关于怎么选择晶体振荡器。 这些参数与临界增益由关,临界增益是微控制器电路启动晶体振荡器所需的最小增益。

有的 datasheet 还会提供一组给定频率和负载电容的晶体振荡器允许的最大的 ESR。

如果微控制器数据表提供 振荡器跨导 (通常以uA/V为单位)或最大临界增益,那么我们需要计算晶体的临界增益并检查微控制器是否可以驱动它。

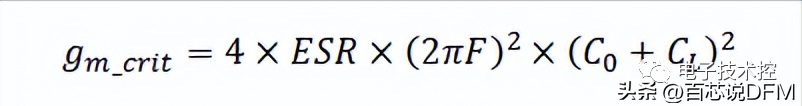

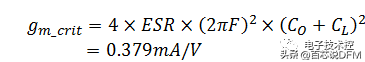

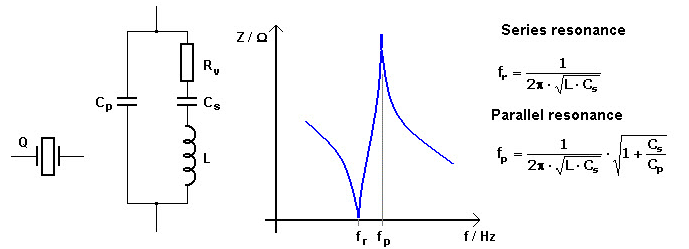

下面为临界增益计算公式:

临界增益公式

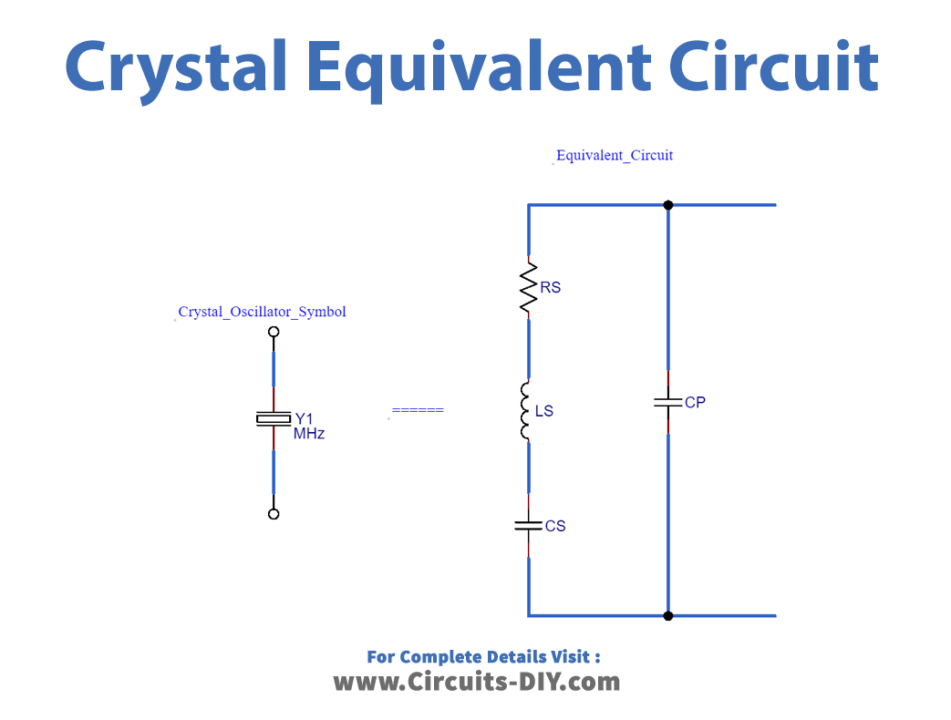

在这个公式中:

F 是晶体振荡器的标称频率

ESR 是晶体的等效串联电阻

CO 是晶振并联电容

CL 是晶体的标称负载电容

临界增益是晶体的一个属性,这些参数在晶体的数据手册中。

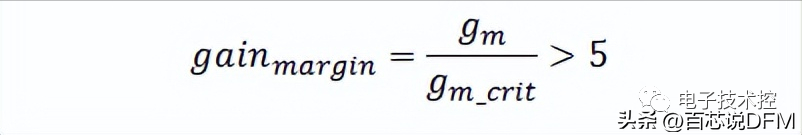

接下来计算增益裕度。 如果增益余量大于5,则振荡器将可靠启动。 更大的增益余量意味着更快的振荡器启动。

晶体振荡器的启动条件:增益余量大于5,如下公式所示:

晶体振荡器的启动条件

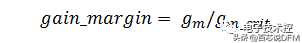

下面为增益裕度计算公式:

增益裕度

或者,一些微控制器数据表提供了最大临界增益gm_crit_max。 在这种情况下,gm_crit必须小于gm_crit_max。

如果微控制器不满足驱动晶振的要求,就需要重新选择晶体振荡器。

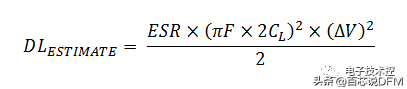

3、晶体振荡器的功耗

datasheet 中会指定了晶体的驱动电平 (DL),驱动电平基本上是晶振正常工作时的最大额定功率。

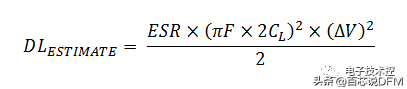

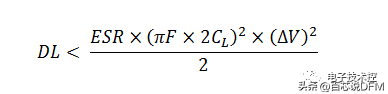

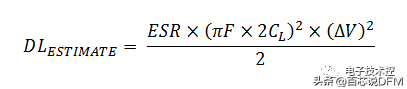

驱动电平的粗略估计可以用下面这个公式计算:

驱动电平驱动电平计算公式

在上面这个公式中:

△V 是 峰峰值振荡器电压 ——最坏的情况:△V=Vcc

如果估计值低于晶体振荡器的额定驱动电平,则直接进行下一步。

符合要求的驱动电平

如果估计值高于晶体振荡器的额定驱动电平,你可以改进估计值或者重新另外的晶体振荡器。

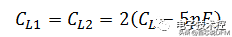

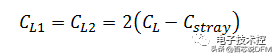

4、选择负载电容 CL1和 CL2

第一次设计晶体振荡电路的时候,先假设两个负责电容是并联的。 选择了CL1=CL2=0.5*CL,但经过验证过后,这是错误的。

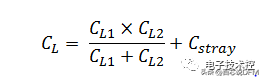

负载电容是晶体两端所需的电容,因此 CL1 和CL2 串联。 负载电容的计算公式如下所示:

负载电容的计算公式

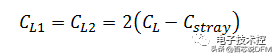

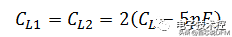

将负载电容的计算公式简化一下,简化后的公式如下所示:

简化后的负载电容计算公式

Cstray 是来自微控制器引脚和走线电容的杂散电容的累积,很多有经验的工程师建议,将这个值估计为 5pF 左右。

则公式为以下:

负载电容公式

一些微控制器数据手册提供了更准确数据一一例如,msp430f22x2系列指定了 1pF 的杂散电容,非常适合其低功耗模型。

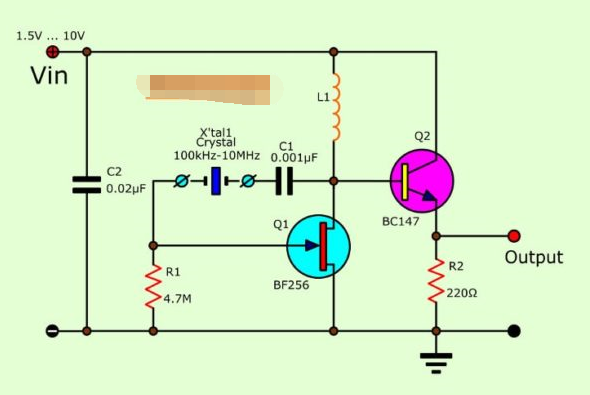

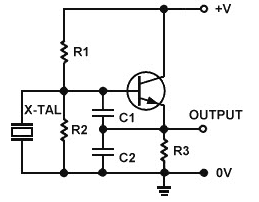

二、PCB 中晶体振荡电路设计

这里希望通过 PCB 布局来最小化振荡器和外部信号之间的耦合,因为高频耦合会激发晶体振荡器的高次谐波,晶振是干扰外部电路的噪声源。

具体有以下几点需要注意:

1、晶体振荡器靠近微控制器

短走线具有低互感和电容,长走线具有高互感和电容。 使晶体靠近微控制器可以缩短走线,从而减少耦合。 所以 走线的长度尽可能短,但不能与其他信号线交叉 。

2、振荡器电路与高频电路隔离开

路由非振荡器信号时, 高频电路要远离振荡器电路 。 也可以考虑使用带有通孔的铜迹线,围绕着振荡器电路,这将减少外部信号线和振荡器之间的互感。

振荡器电路与高频电路隔离开

通常的做法是 将振荡器电路下方的接地层分开,仅在一点点连接分离的接地层,就在微控制器接地旁边。 这可以防止来自其他信号源的返回电流通过振荡器使用的接地层。 上图的示例就是按照这种方法,只是没有很明显。

因为内部石英晶体的存在,由于外部冲击或跌落容易损坏石英晶体,从而造成晶体不振荡,在设计可靠的安装电路时要考虑晶体,靠近 CPU 芯片的位置优先放置远离板块的一面。

晶振放置图

(圆柱晶振)外壳接地后,加一个与晶振形状相似的长方形焊盘,让晶振“平放”在这个焊盘上,并在焊盘的两个长边附近开一个孔(孔要落在焊盘上,最好用多层焊盘代替孔,两个多层焊盘要接矩形焊盘),然后用铜线或其他裸线将晶振“箍”起来,铜线的两端焊接在你开的两个孔或焊盘上。 这样可以避免高温焊接对晶振的损坏,保证良好的接地。

4、手工或机器焊接时,要注意焊接温度

晶振对温度敏感,焊接时温度不宜过高,加热时间尽量短。

5、耦合电容应尽量靠近晶振的电源管脚放置

放置顺序: 根据功率流向,按电容值从小到大排列 ,电容最小的电容值最接近电源引脚。

6、晶振外壳接地

晶振外壳接地(如果接地影响负载电容的话,就不能接地) ,既可以从晶振向外辐射,也可以屏蔽外界信号对晶振的干扰。

7、不要在晶振下方布线,确保完全铺设好地线

在晶振 300mil 范围内不要布线 ,以免晶振干扰其他布线、器件和层的性能。

8、时钟信号的走线尽量短,线宽要大一些

时钟信号的走线尽量短,线宽要大一些 。 在布线长度与热源的距离之间找到平衡点。

三、示例1∶为 STM32 设计 8MHZ 晶体振荡器

1、选择晶振

STM32F427 数据手册中要求:

对于 4-26MHz 晶体,Gm_crit_max=1mA/V

频率容差必须为 +/-500ppm 或更好

CL1 和 CL2 建议在 5pF 到 25pF 之间

这里我们选择 7A-8.000MAAJ-T,虽然 STM32 的引脚间距为0.5mm,但晶振的尺寸小,可以放置在靠近在 STM32的位置。

7A-8.000MAAJ-T 晶振的特性:

CL= 18 pF

红电灯= 60 Ω

频率稳定性= 50 ppm

频率容差= 30 ppm

CO= 7pF最大值

驱动电平(DL)= 500uW max

2、检查微控制器是否可以驱动晶振,计算 gm_crit(增益裕度)∶

gm_crit计算公式

所以gm_crit低于Gm_critmax,振荡器电路将可靠启动。

3、晶振可以处理功率损耗吗?

这里粗略估计电路的驱动电平∶

驱动电平计算公式

计算得 DL =267uW,低于晶体允许的最大驱动电平500uW。

4、选择 负载电容 CL1 和 CL2

假设 Cstray=5pF,则∶

负载电容公式

CL1=26pF

STM32 建议将 CL1和CL2保持在 25pF 以下,所以可以选 24 pF 的电容。

四、示例2∶为 ATMEGA328 选择 16MHZ 晶体振荡器

1、选择晶振

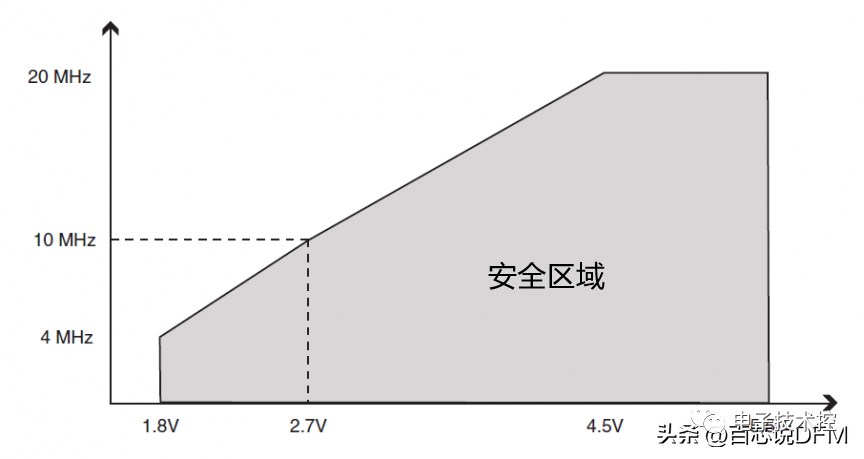

ATMega328 数据手册的要求:

16MHz 的最小电压为 3.78V,以适应安全操作,如图下所示。 要驱动 16MHz 时钟,我们必须在 3.78V 或以上,对于本设计,我们在 5V 下工作。

CL1 和 CL2 建议在 12pF 到 22pF 之间

ATMega328 数据手册

这里选择 9B-16.000MAAE-B 晶振。 9B-16.000MAAE-B 晶振 的特性参数如下所示:

CL= 12pF

红氧化 = 30Ω

频率稳定性= 30ppm

频率容差= 30ppm

C0= 7pF最大值

驱动电平( DL)=500uWmax

2、检查微控制器是否可以驱动晶振

ATMega328 的数据表中 没有跨导规范,这里就必须让开发人员设置好保险丝 ,以便在填充 PCB 后启用振荡器。

3、晶振可以处理功率损耗吗?

粗略估计电路的驱动电平(DL)∶

驱动电平计算

驱动电平( DL )=545uW。

驱动电平估计值太高。 但是,如果选择 CL1并且表明设计的功耗是可以承受的,就可以改进这个估计值。

4、选择 负载电容 CL1 和 CL2

假设Cstray=5pF,则∶

负载电容 计算

CL1= 14PF。

-

pcb

+关注

关注

4319文章

23082浏览量

397551 -

电路设计

+关注

关注

6673文章

2451浏览量

204193 -

晶体

+关注

关注

2文章

1351浏览量

35418 -

振荡电路

+关注

关注

17文章

502浏览量

98778 -

晶体振荡器

+关注

关注

9文章

618浏览量

29111 -

晶体振荡电路

+关注

关注

0文章

29浏览量

6207

原文标题:四、示例2∶为 ATMEGA328 选择 16MHZ 晶体振荡器

文章出处:【微信号:电子威廉希尔官方网站 控,微信公众号:电子威廉希尔官方网站 控】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

3ms之内起振!Epson低功耗晶体振荡器助力FA相机的时钟振荡电路设计

石英晶体振荡器的振幅条件及其在电路设计中的应用

压控晶体振荡器和石英晶体振荡器的区别

振荡电路评估方法(2)为评估振荡电路而进行的工作(振荡裕度与激励功率篇)

低频振荡电路新常识

为评估振荡电路而进行的工作振荡裕度与激励功率篇(振荡电路评估方法2)

为评估振荡电路而进行的工作频率匹配篇(振荡电路评价方法1)

PCB上晶体振荡电路的设计

PCB上晶体振荡电路的设计

评论