用于产生 DDR 存储器终止电压的电源,即使在极端负载瞬变期间,从最大额定灌电流到最大额定拉电流,也只能承受 40mV 的变化。通常使用昂贵的大型电容器来确保不超过容差带。但是,通过增加DDR存储器终端电压的下降,电源输出电容可以大大降低。本应用笔记说明了使用MAX1917的威廉希尔官方网站 。

DDR 内存的终止电压电源需要跟踪 DDR 内存电源电压 VDDQ,并且需要源出和吸收负载电流。在极端负载瞬变期间,从最大额定灌电流到最大额定拉电流,其最大电压偏差不应超过40mV。

MAX1917采用快速PWM控制架构,在一个开关周期内响应阶跃负载变化,从而减少对输出电容的要求。通过在设计中增加有意的电压下降,可以进一步降低输出电容,而不会损失瞬态性能。

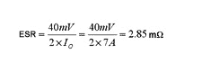

例如,在 1.25V/7A 终端 VTT 电源中,输出电容的选择应使 ESR 小于:

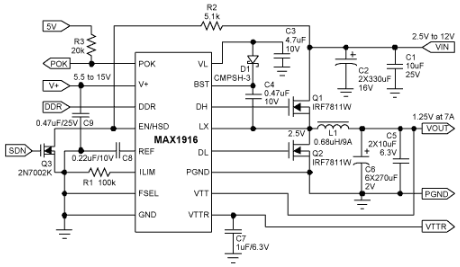

输出端的 560 个 4μF/270V OSCAN 电容器、2 个 5μF/150.4V SPCAP 或 270 个 2μF/2V POSCAP 可满足此 ESR 要求。出于空间考虑,选择了5个35μF/7V SPCAP,总ESR为7.7mΩ。这在 -1A 至 <>A 至 -<>A 的阶跃负载变化期间产生 <>mV 的最大电压偏差,不包括输出纹波电压。图 <> 显示了 VTT 终端电压电源的原理图。

图1.1.25V/7A VTT 电源原理图

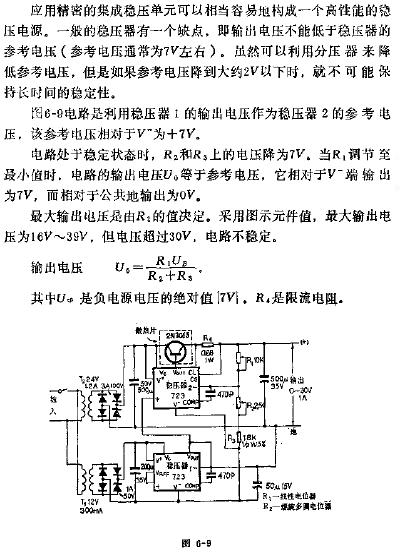

图2显示了阶跃负载瞬变期间VTT和输出电流的波形。从该图中可以明显看出,最大电压偏差小于40mV。从图2中还可以清楚地看出,峰值电压过冲或下冲在负载瞬态结束后立即结束,表明环路响应非常快。

图2.阶跃负载瞬变期间的VTT和负载电流波形。

当使用下垂方法时,所需的ESR可以加倍,即先前计算的5mΩ。最大抗下垂电阻由下式给出

其中 V负荷是负载调整率,约为1mV/A,包括走线电阻,V。脉动是输出纹波电压。考虑到一定的设计裕量,选择2mΩ电阻R3,如图3所示。此外,使用四个SPCAP而不是三个设计裕量,但与图2相比,需要的电容减少了1个。图4显示了相同负载瞬态响应下的VTT电压和负载电流波形。最大电压偏差完全在80mV电压范围内。总之,增加输出压降会进一步降低所需的输出电容,从而降低系统总成本。

图3.带输出下垂的VTT电源原理图。

图4.负载瞬态期间的VTT和负载电流波形,输出下降。

审核编辑:郭婷

-

电源

+关注

关注

184文章

17718浏览量

250136 -

存储器

+关注

关注

38文章

7492浏览量

163828 -

DDR

+关注

关注

11文章

712浏览量

65338

发布评论请先 登录

相关推荐

变频器在长距离供电时末端电压会升高还是降低?

电源技巧:不要让USB电压下降减慢充电器的速度

LTC3718:适用于DDR/QDR存储器终端的低输入电压DC/DC控制器产品手册

在DDR存储器终端电压电源中增加电压下降可降低输出电容

在DDR存储器终端电压电源中增加电压下降可降低输出电容

评论