要实现可靠的RF布局,首先要了解电路板堆叠、电源布线和接地的基本原理。本讨论将探讨这些基本原理,并提供有关电源布线、电源旁路和接地威廉希尔官方网站 的实用且经过设计验证的指南,以最大限度地提高任何RF设计的性能。本文讨论了控制PLL杂散电平的实际示例,因为PLL杂散对电源去耦、接地和滤波器元件放置特别敏感。MAX2827 802.11a/g收发器参考设计PCB布局用于说明。

第 1 部分:供应路由和旁路基础知识

在设计RF电路时,电源部分的实现和布局通常被视为高频信号路径的事后考虑。如果不仔细考虑,电路周围的电源电压很容易损坏和产生噪声,从而对RF电路的系统性能产生不利影响。正确规划PCB层堆叠,Vcc使用星形拓扑进行布线,并正确解耦 Vcc引脚将有助于实现最佳的射频性能。

从合理的PCB层定义开始将简化剩余的布局过程.给定WLAN路由中常用的四层板,典型的堆叠将使用顶层进行元件放置和RF路由,第二层使用接地层,第三层使用电源路由,第四层保留任何信号路由。在第二层放置一个不间断的接地层对于为RF信号路径建立良好控制的阻抗至关重要。它还允许接地返回尽可能短,并隔离第一层和第三层,从而最大限度地减少耦合。虽然可以有效地使用其他堆叠方法(如果使用不同数量的层,则需要),但此处介绍的方法已被证明是成功的。

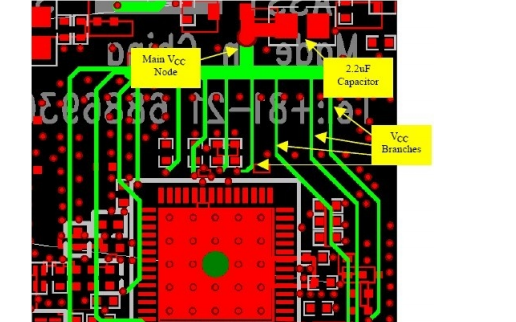

虽然使用大功率平面来简化VCC信号的路由可能很诱人,但这种方法肯定会导致系统性能下降。通过将所有电源电压连接到一个大平面上,不可能防止噪声从一个引脚传递到另一个引脚。相反,使用星形拓扑可减少系统中各种电源引脚之间的耦合。图1所示为通过星形拓扑分配VCC的示例,取自MAX2826 IEEE 802.11a/g收发器评估板的布局。建立一个主VCC节点,从该节点分支出各个走线,为每个RF IC电源引脚供电。对每个电源引脚使用独立的走线可在引脚之间实现空间分离,从而最大限度地减少耦合量。每条线路还将具有与之相关的有限量的寄生电感,并有助于过滤线路中的高频噪声。

图1.星形拓扑 V抄送路由。

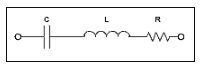

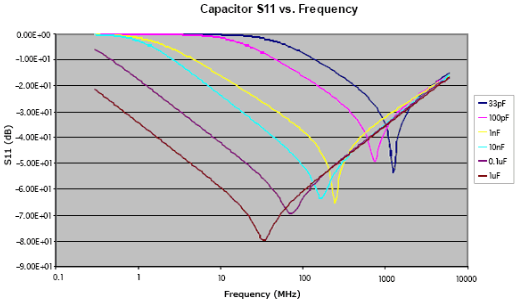

使用星形拓扑进行VCC布线时,必须正确去耦电源线。由于电容器具有寄生电感,去耦变得复杂。实际上,电容器表示为串联RLC电路,如图2所示。电容在低频时占主导地位,但在自谐振频率(SRF)之后,电容器的阻抗将开始看起来是感性的。因此,电容器仅用于在接近或低于其SRF的频率范围内进行去耦,其中电容器在目标频率下呈现低阻抗。图3显示了各种电容值下的典型S11性能。从这些图中,可以通过图中的下降清楚地看到SRF。还可以看出,与较低值的电容器相比,较高的电容在较低频率下提供更好的去耦(显示较低的阻抗)。

图2.电容器的等效电路。

图3.电容阻抗随频率的变化。

在VCC星形的主节点处,最好放置一个大值电容,例如2.2μF。该电容器具有低SRF,但在消除低频噪声和产生稳定的直流电压方面非常有效。在IC的每个电源引脚上,应使用一个较低值的电容,例如10nF,以消除可能耦合到VCC线路上的任何较高频率噪声。如果电源引脚供电的电路部分(即VCO电源)对噪声特别敏感,则可能需要在IC附近放置两个电容器。例如,将100pF电容与10nF电容并联将提供更宽的去耦频率范围,从而使电源不易受到噪声的影响。应仔细检查每个电源引脚,以确定需要多少去耦,以及特定电路在什么频率下最容易受到噪声的影响。

将良好的电源去耦威廉希尔官方网站 与经过深思熟虑的PCB层堆叠和谨慎的Vcc相结合布线(实现星形拓扑)将为任何RF系统设计提供坚实的基础。虽然还有许多其他因素会降低系统性能,但尽可能无噪声的电源对于实现最佳性能至关重要。

第2部分:RF接地和使用接地过孔的基础知识

接地和布线也是WLAN电路板布局和制造中的关键步骤。这些步骤将直接影响电路板寄生参数,有时会导致不良的系统性能。射频板设计中没有独特的接地分布解决方案;有几种方法可以实现令人满意的系统性能。分离接地层或分离走线可用于分离interwetten与威廉的赔率体系 和数字信号,或隔离大电流或高发热部分。然而,根据以前的WLAN板设计经验,四层堆叠板中的单个实心接地层效果很好。一般规则是通过使用接地层将RF部分与电路板中的其他电路屏蔽来避免交叉干扰。如上文第 1 部分所述,第 2 层通常指定为接地层,而第 1 层用于组件和射频路由。

接地布置建立后,重要的是以尽可能短的路径将所有信号接地返回到固体接地层。将过孔从顶层接地降至接地层是此任务的常见解决方案。然而,过孔是相当感应的。过孔的物理模型如图 4 所示。图5给出了精确的电气模型,其中L通过通过电感和 C通过是过孔PCB焊盘的寄生电容。在这里讨论的接地威廉希尔官方网站 中,寄生电容可以忽略不计。直径为1.6mm的0.2mm深孔可提供约0.75nH的电感。2.5GHz/5.0GHz WLAN频段的等效电抗分别约为12Ω/24Ω。因此,单通孔接地不能为RF信号提供真正的接地。在良好的电路板设计中,在RF电路部分将尽可能多的过孔接地,特别是对于常用IC封装的裸露接地焊盘。例如,如果不这样做,将导致接收前端或功率放大器电路中发生不希望的发射极退化,从而导致增益降低和噪声系数性能下降。应该注意的是,焊接不良的接地焊盘会导致类似的问题影响。此外,功率放大器的散热需要许多过孔连接到坚固的接地层。

图4.通孔的物理模型。

图5.过孔的电气模型

滤除来自其他级的噪声,并约束局部产生的噪声,以避免通过V的级之间的交叉干扰抄送线条是使用 V 的一些优点抄送解耦。如果去耦电容共享相同的接地过孔,则由于通孔电感对地,接头端的这些过孔将承载来自两个电源的所有RF干扰。这不仅使去耦电容失去其功能,而且还为系统中各级之间的噪声耦合提供了另一条路径。

如第3部分后面所述,PLL实现始终是系统设计中面临的挑战。如果没有良好的接地分离,可能无法实现令人满意的杂散电平性能。在当今的IC设计中,所有PLL和VCO都集成到芯片中;大多数PLL利用数字电流电荷泵输出通过环路滤波器控制VCO。通常,需要使用二阶或三阶RC环路滤波器将电荷泵的数字脉冲电流滤波至模拟控制电压。最靠近电荷泵输出的两个电容必须直接接地至电荷泵电路地。这样可以将接地返回脉冲电流路径与VCO接地隔离,从而最大限度地减少LO上的比较频率杂散。第三个电容(用于三阶滤波器)应直接连接到VCO地,以防止控制电压随数字电流浮动。偏离这些原则会增加高比较杂散的风险。

用于接地的PCB布局示例如图6所示。接地焊盘中有许多接地过孔,允许每个 Vcc去耦电容具有自己的接地通孔。盒子内的电路是PLL环路滤波器。第一个电容器直接连接到GND_CP,而第二个电容器(与R串联)旋转180度并以相同的GND_CP返回。然而,第三个电容器连接到GND_VCO。这种接地分布产生了卓越的系统性能。

图6.PLL滤波器元件放置和接地示例,如MAX2827参考设计板所示。

第 3 部分:通过适当的电源旁路和接地管理 PLL 杂散

在 802.11a/b/g 系统中满足发射光谱模板要求也是设计过程中具有挑战性的组成部分。线性度和功耗必须平衡,有足够的裕量,以符合IEEE和FCC规范,同时保持足够的发射输出功率。IEEE 802.11g系统的典型目标是天线+15dBm,28MHz偏移时为-20dBr。带内邻道功率比(ACPR)在很大程度上被认为是器件线性度的函数,可以在合理的范围内适应特定应用。优化发射线中ACPR的艰巨任务通常是通过Tx IC和PA中的偏置调整以及PA输入、输出和级间匹配网络的微调来实现的。

然而,并非所有明显的ACPR问题都必然是由于器件线性度造成的。在一个主要的例子中,即使对功率放大器和PA驱动器(ACPR的两个主要贡献因素)进行了广泛的调谐和优化,WLAN发射器的相邻信道性能也可能低于理想水平。来自发射器锁相环(PLL)的本振(LO)上的杂散也会导致ACPR性能不佳。LO杂散很容易与调制基带信号混合,产物将与所需通道一起放大(见图7)。仅当PLL杂散高于特定阈值时,此混频作用才是一个问题。当它们低于此阈值时,ACPR将由PA非线性主导。当Tx输出功率和频谱模板性能“线性度受限”时,我们可以以电流换取线性度和输出功率,这是理想的情况。如果LO杂散主导ACPR性能,那么我们就“杂散有限”,并且需要将PA偏置得更高,以降低其在给定P下的ACPR贡献外.后一种解决方案需要更大的电流,并且设计灵活性较低。

图7。 802.11g频谱模板要求和比较杂散的退化。

这种情况导致人们质疑如何有效地将PLL杂散限制在不影响发射频谱的幅度?一旦确定了有问题的支线,就可以使用一些威廉希尔官方网站 。第一个也是最诱人的解决方案可能是缩小PLL的环路滤波器带宽,以试图衰减杂散。这在少数特定情况下可能有效,但一个例子将暴露这种推理的潜在愚蠢。

以图 8 所示的假设情况为例。假设使用比较频率为20MHz的小数N分频频率合成器。如果环路滤波器是二阶滤波器,截止频率为200kHz,则标称滚降约为40dB/十倍频程,在80MHz时产生20dB的衰减。如果基准杂散是在-40dBc(可能导致不希望的调制的水平)下测量的,则产生杂散的机制可能会超出环路滤波器的影响。(如果它是在过滤器之前生成的,那么它从一开始就会非常强大)。缩小滤波器带宽不太可能改善这种杂散,但会增加PLL锁定时间——这显然是不希望看到的。

图8.简化的PLL滤波器渐近线,以及转折频率和比较杂散的相对位置。

可以说,对抗PLL杂散的最有效方法是利用适当的接地、电源布线和去耦威廉希尔官方网站 。本文开头讨论的项目是缓解PLL杂散问题的良好起点。由于电荷泵中发生的电流变化相对较大,因此星形拓扑结构在这里势在必行。如果隔离不足,电流脉冲产生的噪声会耦合到VCO的电源,并将在比较频率下有效地调制VCO。这通常被称为“VCO 推送”。通过对电源线进行物理隔离、在每个VCC引脚上进行去耦、明智地放置接地过孔以及引入串联铁氧体元件(考虑作为最后的手段),可以改善隔离。虽然并非所有这些措施在每个设计中都是必要的,但每种措施都可以用作更大的杂散缓解策略的一部分。

图9显示了去耦VCO电源不充分的影响。所示的电源纹波与损坏电源线的电荷泵活动直接相关。幸运的是,在这种情况下,通过增加本地旁路电容可以显著减少损坏。图10是在更改后的同一点测量的。

图9.解耦不充分的VCC_VCO

图 10.VCO电源旁路电容增加可降低噪声。

在另一个例子中,在VCO电源上观察到类似的噪声。由此产生的杂散足以影响ACPR,并且没有多少脱钩改善这种情况。在本例中,对PCB布局的审查显示,VCO电源走线直接位于电荷泵电源下方。重新路由走线将杂散降低到符合规范的水平。

审核编辑:郭婷

-

电源

+关注

关注

184文章

17719浏览量

250209 -

滤波器

+关注

关注

161文章

7817浏览量

178144 -

RF

+关注

关注

65文章

3055浏览量

167029

发布评论请先 登录

相关推荐

WiFi收发器的电源和接地设计

从WIFI收发器的PCB布局看射频电路电源和基地的设计方法

怎么设计WiFi收发器的电源和接地?

CAN收发器驱动程序模块的功能描述

WiFi收发器的电源和接地设计

光纤收发器的分类

如何实现WiFi收发器的电源和接地设计

WiFi收发器的电源和接地设计

WiFi收发器的电源和接地设计

评论