当今的基站系统(BTS)必须满足各种不同的标准,并且必须满足信号链各个模块中的关键规范。以下本文介绍了高动态性能ADC、可变增益放大器、混频器和本振等信号链组件的这些需求,并详细介绍了它们在典型BTS应用中的使用,以及它们如何满足对高动态性能、高交调性能和低噪声的严格要求。

大多数数字接收器对高性能模数转换器(ADC)和interwetten与威廉的赔率体系 元件提出了苛刻的要求。例如,在蜂窝基站数字接收器中,需要足够的动态范围来处理高电平干扰源(或阻塞信号),同时正确解调较低电平的所需信号。Maxim的MAX1418 15位65Msps或MAX1211 12位65Msps ADC与MAX9993 2GHz或MAX9982 900MHz集成混频器相结合,可为接收器系列中最关键的两个级提供出色的动态范围。此外,Maxim的MAX2027和MAX2055 IF数字可变增益放大器(DVGA)具有极高的三阶输出交调截点性能(OIP3),具有许多应用所需的增益调节范围。

蜂窝基站(BTS:基收发器站)由许多不同的硬件模块组成,包括执行射频接收器(Rx)和发射器(Tx)功能的模块 - 即收发器(TRx)。在较旧的模拟放大器和 TACS BTS 中,一个收发器处理双工 Rx 和 Tx 射频载波。需要许多收发器来提供足够的载波以获得所需的呼叫覆盖范围。模拟威廉希尔官方网站 正在被CDMA和WCDMA在全球范围内取代,欧洲在十多年前就采用了GSM。在CDMA中,许多呼叫者使用相同的RF频率,这允许单个收发器同时处理许多呼叫者的信号。如今存在各种CDMA和GSM设计,BTS制造商一直在寻求降低成本和功耗的方法。优化单载波解决方案或开发多载波接收器可以实现这一目标。图1显示了BTS设备中常用的子采样接收器架构中的主要模块。

图1.子采样接收器架构。

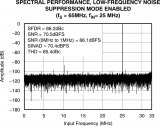

Maxim的MAX9993 2GHz混频器和MAX9982 900MHz混频器提供增益、高线性度以及低噪声系数,使设计人员能够消除许多设计中的有损无源混频器。MAX2027和MAX2055设计工作在接收器的第一或第二中频级。两款器件均在整个增益调整范围内提供+1dBm三阶输出交调截点(OIP2)性能。尽管MAX40 (3位1418Msps)和MAX15 (65位1211Msps)数据转换器如图12所示,但两个转换器系列都包含满足大多数应用的其他速度等级。如果取消了第二个下变频(以虚线显示),则该图描述了单个下变频架构。

美信的低噪声ADC,MAX1418

对于图1所示的子采样接收器架构,对ADC提出了严格的噪声和失真要求。在接收器应用中,较低电平的目标信号单独数字化,或者在存在幅度可能明显较大的无用信号的情况下进行数字化。为了正确设计接收器,必须在这两个信号极端下确定ADC有效噪声系数。转换器的噪声系数是通过将其总噪声功率与本底热噪声进行比较来确定的。对于小模拟输入信号,热+量化噪声功率主导ADC的本底噪声,用于近似ADC的有效噪声系数(NF)。

在实践中,一旦在小信号条件下知道ADC的有效噪声系数,并确定模拟电路(RF&IF)的级联噪声系数,就会选择ADC之前的最小功率增益以满足所需的接收器噪声系数。功率增益量决定了最大阻塞信号的上限,或者是接收器在ADC过载之前可以容忍的最高干扰电平。对于BTS应用,如果不实施自动增益控制(AGC),ADC通常没有足够的动态范围来满足噪声系数要求(接收器灵敏度)和最大阻塞信号要求。AGC 可以包含在射频级和/或中频级中。

MAX1418系列中的其它转换器针对基带性能进行了优化,其中输入= f时钟/2.在此频率范围内工作并使用这些基带优化部件可提供最佳的转换器动态范围。这些转换器包括针对1419Msps时钟速率优化的MAX65和针对1427Msps时钟速率优化的MAX80,在基带时SFDR性能均等于94.5dBc。

以下示例使用表1418中列出的MAX1规格:

表 1.MAX1418电气特性

| 参数 | 条件 | 象征 | 典型值 | 单位 |

| 分辨率 | N | 15 | Bits | |

| 模拟输入范围 | VID | 2.56 | VP-P | |

| 差分输入电阻 |

RIN |

1 | kΩ | |

| 交流规格 | f时钟= 65毫秒 | |||

| 热+量化本底噪声 | 模拟输入 = -35dBFS | Nfloor | -78.2 | dBFS |

| 信噪比模拟 = -2dBFS | fIN = 70兆赫 | 信 噪 比 | 73.6 | 分贝 |

| 无杂散动态范围模拟 = -2dBFS | fIN = 70兆赫 | SFDR | 84 | 分贝 |

| 信噪比和失真模拟 = -2dBFS | fIN = 70兆赫 | SINAD | 73.3 | 分贝 |

MAX1418无需连接LSB即可与14位接口配合使用。如果这样使用,SNR性能会略有下降,SFDR性能基本上不受影响。

图2显示了在没有大电平阻塞器的情况下ADC噪声贡献。假设ADC前面的所有模拟电路的级联噪声系数均为3.5dB。作为第一个近似值,假设设计人员的目标是让ADC将接收器总噪声系数降低不超过0.2dB,以满足CDMA基站接收器中的某些目标灵敏度。该噪声系数值应为空口要求提供足够的裕量,这也取决于最终探测器的Eb/No(位能量与噪声功率谱密度比)要求。如果使用表1418中的MAX1热+量化本底噪声值,当器件时钟频率为26.9Msps (61倍芯片速率)时,可以计算出44.50dB的等效噪声系数。由于实现了处理增益,1.23MHz CDMA通道带宽中的ADC噪声比奈奎斯特带宽中的噪声低14dB。需要36dB的总增益才能实现3.7dB的理想级联接收器噪声系数值。

图2.无阻塞信号的ADC噪声贡献。

当增益领先于ADC36dB时,天线端的最大单音阻塞电平高于-30dBm将超过ADC满量程输入。cdma2000®蜂窝基站标准规定天线端子上允许的最大阻塞电平为-30dBm。在本例中,6dB增益降低用于增加施加到ADC的最大允许阻塞信号,从而为标准规格提供裕量。假设允许2dB裕量,6dB增益降低会导致天线的最大阻塞电平为-26dBm,ADC输入端的最大阻塞电平为+4dBm(见图3)。当存在单音阻塞信号时,蜂窝标准允许相对于基准灵敏度的整体(噪声+失真)下降3dB。各个噪声和失真分量的分配由设计人员决定。

假设设计人员允许RF前端级联噪声加上失真在阻塞信号施加1dBAGC的情况下将NF降低3dB(标称5.6dB)。由于ADC前面只有30dB的增益,有效噪声系数为29.4dB,由ADC SNR性能决定,在“阻塞条件”下,级联接收器噪声系数为5.7dB,与根据接收器灵敏度计算的2.3dB噪声系数相比下降了7dB。由于该计算未考虑杂散性能,因此ADC的无杂散动态范围(SFDR)性能可能会再降低1dB。当存在阻塞信号时,SINAD 可用于计算有效 NF,而不是单独计算噪声和 SFDR 贡献。

图3.ADC噪声对阻塞信号的贡献。

MAX1211允许单次下变频架构

如果转换器在较高的IF频率下可以获得足够的SNR和SFDR性能,则子采样架构可以与单个下变频架构一起使用。Maxim的MAX1211是一款12位65Msps转换器,设计时考虑了这种架构,并即将推出引脚兼容的80Msps和95Msps版本。该系列转换器允许对高达 400MHz 的输入频率进行直接 IF 采样,并具有差分或单端时钟输入等高级功能,允许 20% 至 80% 的时钟占空比,数据有效指示器允许简化时钟和数据定时,2 的补码或格雷码数字输出数据格式全部采用小型 40 引脚薄型 QFN 封装 (6mm x 6mm x 0.8mm)。MAX2的典型交流规格见表1211,说明了175MHz模拟输入频率下出色的交流性能。 (注:改进型MAX1211版本将在大约一个月内上市,其交流规格见下表。

表 2.MAX1211电气特性

| 参数 | 条件 | 象征 | 典型值 | 单位 |

| 分辨率 | N | 12 | Bits | |

| 模拟输入范围 | VID | 2 | VP-P | |

| 差分输入电阻 | RIN | 15 | kΩ | |

| 交流规格 | f时钟= 65毫秒 | |||

| 热+量化本底噪声 | 模拟输入 = -35dBFS | Nfloor | 69.3 | dBFS |

| 信噪比模拟 = -0.2dBFS |

fIN= 32.5兆赫 fIN= 175兆赫 |

信 噪 比 |

68.3 66.8 |

分贝 |

| 无杂散动态范围模拟 = -0.2dBFS |

fIN= 32.5兆赫 fIN= 175兆赫 |

SFDR |

82.4 79.7 |

分贝 |

| 信噪比和失真模拟 = -2dBFS |

fIN= 32.5兆赫 fIN= 175兆赫 |

SINAD |

68.1 66.5 |

分贝 |

选择单次向下转换而不是双次向下转换时,可以获得显着的优势。通过消除第二个下变频混频器、秒中频增益级和 2德·LO频率合成器电路,器件数量和电路板空间可减少约10%,成本可减少10至20美元。

不同架构的杂散考虑

如果节省器件数量、电路板空间、功耗和成本不能提供足够的激励,以下示例说明了在单下变频架构中使用MAX1211时获得的频率规划优势。假设cdma2000接收器设计为在PCS频段内工作。对于61.44Msps的采样速率和30.72MHz的合成器参考频率,请选择以第六奈奎斯特频段为中心的第一中频频率,频率为169MHz,带宽约为1.24MHz。使用相同的第一中频中心频率 169MHz,DDC 架构假设 2德·中频频率居中为 2德·奈奎斯特频段为46.08MHz。

表 3.SDC 和 DDC 架构的刺激搜索假设

| SDC | DDC | 参数 | 价值 |

| x | x | 接收频段 | 1904.3800 至 1905.6200MHz |

| x | x | 时钟频率 | 61.44000兆赫 |

| x | x | 最大时钟谐波 | 30 |

| x | x | 合成器参考频率 | 30.7200兆赫 |

| x | x | 最大合成器谐波 | 40 |

| x | x | 首次注射LS | 1736.0000兆赫 |

| x | x | 最大第一LO谐波 | 5 |

| x | x | 接收图像波段 | 1566.3800 至 1567.6200MHz |

| x | x | 第一个中频波段 | 168.3800 至 169.6200MHz |

| x | 第二次注射LS | 122.9200兆赫 | |

| x | 最大第二LO谐波 | 5 | |

| x | 第一中频影像波段 | 76.2200 至 77.4600MHz | |

| x | 第二中频波段 | 45.4600 至 46.7000MHz |

表3列出了单载波、单下变频(SDC)和双下变频(DDC)架构中接近PCS频段上限的RF载波的杂散搜索假设。对于SDC架构,杂散搜索在RF接收频段、接收镜像频段、IF频段和IF镜像频段总共产生134个杂散。这些杂散中的大多数都是高阶的,不会降低接收器的性能。对于 DDC 架构,此杂散搜索结果超过 2400 个杂散,是 SDC 架构计算结果的 18 倍。这些杂散产物出现在RF接收频带、接收镜像频带、1圣中频波段,1圣中频像段,2德·中频波段和 2德·中频图像波段。通过良好的电路板布局实践和滤波,由较高时钟谐波和频率合成器参考频率组合产生的杂散将相对容易降低。然而,大量的低阶杂散将难以最小化。

Maxim的IF放大器,MAX2027和MAX2055

Maxim还提供高性能IF放大器,具有以1dB增量进行数字可变增益控制。MAX2027为数字可变增益放大器(DVGA),具有单端输入/单端输出,频率范围为50MHz至400MHz。该DVGA在最大增益下提供5dB的低噪声系数。MAX2055为单端输入/差分输出DVGA,用于驱动频率范围为30MHz至300MHz的高性能ADC。升压变压器可在MAX2055的差分输出和ADC差分输入之间使用。变压器由差分驱动;从而优化变压器性能和输出信号之间的平衡。两个DVGA均采用5V偏置工作,在所有增益设置范围内具有+40dBm OIP3。

Maxim的高线性度混频器,MAX9993和MAX9982

在接收器电路中,混频器受到大输入信号的影响,这对它们的性能提出了严格的要求。理想情况下,混频器输出信号的幅度和相位与输入信号的幅度和相位成正比,与LO信号特性无关。根据这一假设,混频器的幅度响应对于RF输入是线性的,并且与LO输入无关。

然而,混频器的非线性会产生不需要的混频产物,称为杂散响应,这是由于不需要的信号到达混频器的RF输入端口并在IF频率下产生响应引起的。当它们干扰所需的IF频率时,混频机制可以描述为:

f如果= ±毫频射频±瞧其中IF、RF和LO分别指指定端口的信号,m和n是RF和LO频率的整数谐波,它们混合以产生许多杂散产物的组合。

集成(或有源)平衡混频器设计,如Maxim的MAX9993和MAX9982,其性能可与无源混频器方案相媲美,因此越来越受欢迎。平衡混频器在 m 或 n 偶数时抑制某些杂散响应,从而产生出色的 2德·阶谐波性能。理想的双平衡混频器可抑制m或n(或两者)为偶数的所有响应。IF、RF和LO端口在所有双平衡混频器中相互隔离。使用设计合理的巴伦,这些混频器可以具有重叠的RF、IF和LO频段。MAX9993和MAX9982的特性包括:增益、低噪声系数、集成LO缓冲器、低LO驱动、允许两个LO频率输入的LO开关、出色的LO噪声性能以及RF和LO端口上的集成RF巴伦。

Maxim的混频器内置LO缓冲器,具有出色的LO噪声性能,可降低驱动它们的输入LO功率要求。LO噪声与高电平输入阻塞信号相互混合,使接收器脱敏。MAX9993和MAX9982均具有低噪声LO缓冲器,设计在存在阻塞信号时对接收器脱敏的影响最小。例如,假设提供注入信号的VCO具有-145dBc/Hz的边带噪声性能。MAX9993的典型LO噪声性能为-164dBc/Hz,因此复合边带噪声性能仅下降0.05dBc/Hz至-144.95dBc/Hz。这样,用户不仅需要向混频器提供低电平LO注入信号,而且可以确保接收器的互易混频性能不会因MAX9993 LO缓冲器性能而下降。

特别麻烦的2德·阶次杂散响应称为半IF(1/2 IF)杂散响应,用于低边注入的混频器指数(m = 2,n = -2)和(m = -2,n = 2)用于高端注入。对于低侧注入,产生半中频杂散响应的输入频率位于所需RF频率以下,数量为f如果/2所需的RF输入频率(见图4)。所需的RF频率由1909MHz表示,结合LO频率1740MHz,得到的IF频率为169MHz。虽然CDMA RF和IF载波占用1.24MHz带宽,但它表示为表示中心载波频率的单个频率。在本例中,1824.5MHz处的不需要信号会导致169MHz处的半IF杂散产物。

验证:

2 x fHalf-IF - 2 x fLO =

2 x (fRF - fIF/2) - 2 x (fRF - fIF) =

2 x (fRF - 2 x fIF/2) - 2 x fRF + 2 x fIF = fIF

结果在:

2 x 1824.5MHz - 2 x 1740MHz = 169MHz

图4.所需频率的位置射频, f瞧, f如果和不需要的 f半中频。

抑制量称为2x2杂散响应,可通过混频器的二阶交调截点IP2进行预测。图2中的2x5 IMR或杂散值取自Maxim的MAX9993数据资料。请注意,图中的信号电平是指计算输入IP2(IIP2)性能的混频器的输入。

如此卓越的 2x2 性能水平可带来以下结果:

IIP2 = 2 x IMR + PSPUR = IMR + PRF

= 2 x 70dBc + (-75dBm) = 70dBc + (-5dBm)

= +65dBm

类似地,Maxim的MAX9982 900 MHz有源混频器在类似条件下提供相当于2dBc的典型2RF - 65LO杂散响应,从而产生:

IIP2 = 2 x IMR + PSPUR = IMR + PRF

= 2 x 65dBc + (-70dBm) = 65dBc + (-5dBm)

= +60dBm

图5.2德·-参考混频器输入的信号的阶次截点计算,IIP2。

混频器前方RF路径中使用的镜像抑制滤波器可衰减任何放大器谐波。LO路径中的噪声滤波器衰减由LO注入源引起的谐波。高电平输入信号会产生失真或互调产物,可以通过计算器件或系统输入或输出端的截点来量化。对于混频器LO功率保持恒定的情况,交调截点或失真积的阶数仅由RF乘法器决定,而不由LO乘法器决定,因为RF信号的变化仅是问题。阶数是指失真产物的幅度随着输入电平的升高而增加的速度。

研究表明,Maxim的MAX1418 15位ADC具有出色的噪声性能,因此所需的接收器增益较低,因此能够以最小的AGC承受更高的阻塞或干扰电平。MAX1211 ADC系列非常适合单变频接收器架构,具有1圣中频输入频率高达400MHz。此外,Maxim的RF MAX9993和MAX9982混频器提供所需的线性度、低噪声系数和足够的功率增益,无需当今许多接收器设计中的无源混频器。Maxim的MAX2027和MAX2055 DVGA在整个增益调整范围内提供约+3dBm的典型OIP40值。综上所述,包含这些组件的接收器阵容可以在极具成本效益的解决方案中实现高水平的性能。

审核编辑:郭婷

-

放大器

+关注

关注

143文章

13595浏览量

213528 -

接收器

+关注

关注

14文章

2472浏览量

71926 -

adc

+关注

关注

98文章

6500浏览量

544718

发布评论请先 登录

相关推荐

如何实现超宽带直接转换接收器的性能优化

基于RF混频器的3G无线基站接收器应用

数字接收机中高性能ADC和射频器件的动态性能要求

数字接收机中高性能ADC和射频器件的动态性能要求

基于分集接收机实现高性能系统

数字接收器应用中高性能ADC和RF元件的动态性能要求

数字接收器应用中高性能ADC和RF元件的动态性能要求

评论