介绍

在芯片做功能ECO时,DFT部分的逻辑常常被破坏,这是由于正常工作模式下修改设计的原因。在功能ECO时,DFT的控制信号被设为无效,ECO工具意识不到DFT逻辑被更改,并且形式验证也验证不出来。我们发现,当ECO过的网表送给DFT工具,DFT工具需要运行很长时间来识别网表是否存在问题。

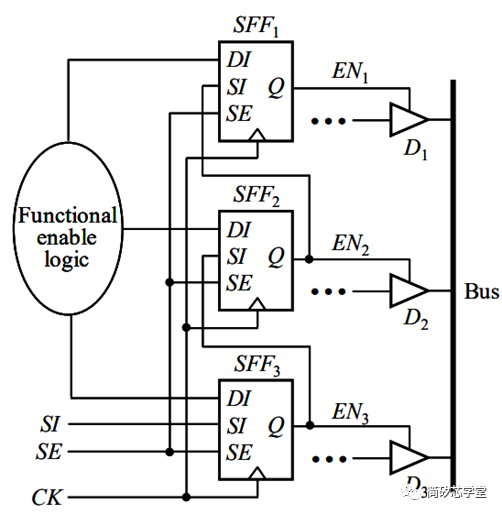

NanDigits GOF提供了一种快速DFT DRC检查的功能,来检查DFT逻辑中的问题。DFT中最基本的DRC检查就是确认扫描链是否完整,就是说,GOF可以捕获和输出测试进行中的测试pattern。另外,在测试模式下,DFT的时钟和复位必须是要受控的,以便来使能合适的测试pattern。

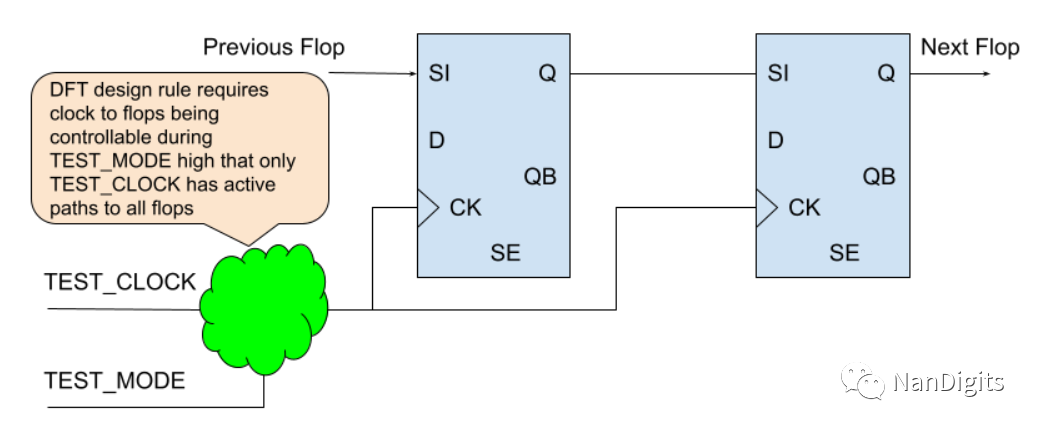

下图是DFT模式使能后的示意图,TEST_MODE=1,TEST_CLOCK被送到每个DFF的时钟端。

示例

下面是GOF做DFT DRC检查的脚本,先读入lib库和网表,再设置使能DFT模式,并创建时钟、复位、si/so扫描链对,最后运行dft_drc()命令来执行DFT DRC的检查。

# dft_drc.pl

set_log_file("dft_drc.log");#设计log

read_library("art.5nm.lib");#读入lib库

read_design('-imp', 'dft_top.v'); # 读入带有DFT的网表

set_top("DFT_TOP"); # 设置顶层

set_pin_constant("test_scan_shift",1);# 设scanshift为1

set_pin_constant("all_test_reg/Q",1);#设TDRall_test寄存器输出Q为1

set_pin_constant("test_mode_reg/Q",1);#设TDRtest_mode寄存器输出Q为1

create_clock("occ_add_1_inst/U0/Z",10);#创建时钟,周期10ns,可能有多个

create_clock("occ_add_2_inst/U0/Z",10);

create_reset("power_on_reset",0);#创建reset

set_top("DESIGN_TOP"); # pin_si/pin_so是DFT_TOP的内部pin

set_scan_pairs("pin_si[0]","pin_so[0]");#添加扫描链对

set_scan_pairs("pin_si[1]", "pin_so[1]");

set_top("DFT_TOP");#回到顶层

my$err=dft_drc;#运行DFT DRC检查

if($err){

gprint("DFT DRC found $err errors

");

}

运行DFT DRC检查:

gof -run dft_drc.pl

结语

NanDigits GOF提供了快速DFT DRC的检查和修复,来保证功能ECO不会影响到DFT扫描链,缩短功能ECO后的DFT修复和验证的时间,帮助客户更快的Tapeout。最新版GOF10.4支持此功能,欢迎试用评估。

审核编辑:刘清

-

DFT

+关注

关注

2文章

231浏览量

22729 -

DRC

+关注

关注

2文章

149浏览量

36183 -

ECO

+关注

关注

0文章

52浏览量

14900 -

控制信号

+关注

关注

0文章

164浏览量

11968

原文标题:用NanDigits GOF来做DFT DRC检查

文章出处:【微信号:ExASIC,微信公众号:ExASIC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

HyperLynx DRC功能和优势

电气设计规则检查工具HyperLynx DRC

PCB设计电气规则检查器解决DRC问题

基于Cadence软件DRACULA工具的DRC检查

NanDigits GOF提供一种快速DFT DRC检查的功能

NanDigits GOF提供一种快速DFT DRC检查的功能

评论