No.1 案例背景

当芯片底部出现焊接不良的问题时,我们可以怎么进行失效分析呢?

本篇案例运用X-ray检测——断面检测——焊锡高度检测——SEM检测的方法,推断出芯片底部出现焊接不良的失效原因,并据此给出改善建议。

No.2 分析过程

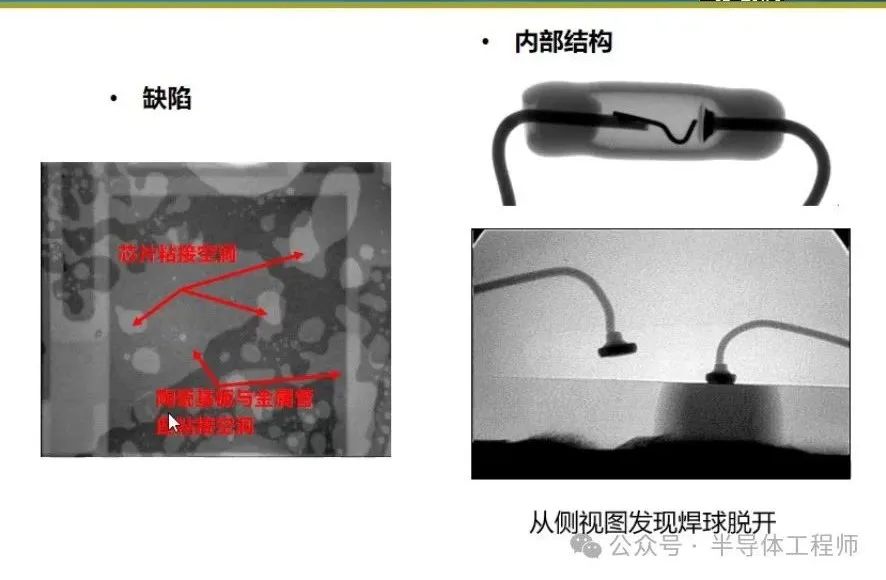

X-ray检测

说明

对样品进行X-ray检测,存在锡少、疑似虚焊不良的现象。

断面检测

#样品断面检测研磨示意图

位置1

位置2

位置3

说明

样品进行断面检测,底部存在锡少,虚焊的现象。且芯片底部焊锡与PCB焊锡未完全融合。

焊锡高度检测

引脚焊锡高度0.014mm

芯片底部焊锡高度0.106mm

说明

芯片引脚位置焊锡高度0.014mm,芯片未浮起,芯片底部高度为0.106mm,锡膏高度要大于芯片底部高度才能保证焊接完好。

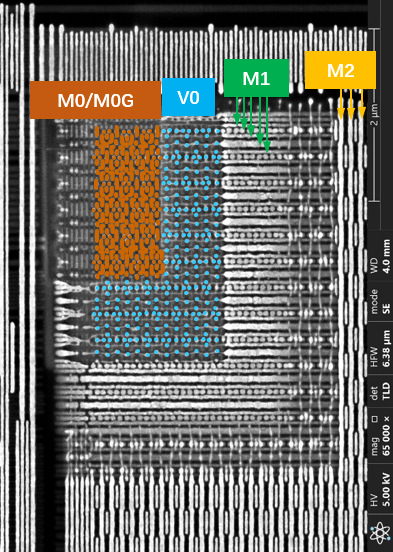

SEM检测

说明

对底部焊接的位置进行SEM检测,芯片与PCB之间焊锡有缝隙,焊锡未完全融合,IMC致密性差,高度5μm左右。

No.3 分析结果

通过X-ray、断面分析以及SEM分析,判断引起芯片底部焊接失效的原因主要有——

① 芯片底部存在锡少及疑似虚焊不良的现象;

② 芯片底部焊锡与PCB焊锡未完全融合的现象。而且,芯片焊接未浮起,芯片底部高度仅为0.106mm。只有当锡膏高度大于芯片底部高度时,才能保证焊接完好;

③ 芯片与PCB之间焊锡有缝隙,焊锡未完全融合,IMC致密性差,高度4-5μm左右;

根据以上综合分析,造成芯片底部焊接虚焊的原因推测为:

1. 锡膏厚度不足导致底部焊接虚焊;

2.焊接时热量不足导致焊锡液相时间不足。

No.4 改善方案

1. 建议实际测量锡膏高度(L)与芯片底部高度(A1)后进行调整;

2. 建议根据实际测量情况,适当调整芯片底部焊锡液相时间。

新阳检测中心有话说:

本篇文章介绍了芯片底部焊接失效分析。如需转载本篇文章,后台私信获取授权即可。若未经授权转载,我们将依法维护法定权利。原创不易,感谢支持!

新阳检测中心将继续分享关于PCB/PCBA、汽车电子及相关电子元器件失效分析、可靠性评价、真伪鉴别等方面的专业知识,点击关注获取更多知识分享与资讯信息。

审核编辑黄宇

-

芯片

+关注

关注

455文章

50771浏览量

423406 -

失效分析

+关注

关注

18文章

214浏览量

66401

发布评论请先 登录

相关推荐

PCBA加工常见质量问题揭秘:焊接不良与解决方案

FIB威廉希尔官方网站 :芯片失效分析的关键工具

显微镜在芯片失效分析中的具体应用场景及前景

SMT锡膏贴片加工中有哪些焊接不良?

芯片开封decap简介及芯片开封在失效分析中应用案例分析

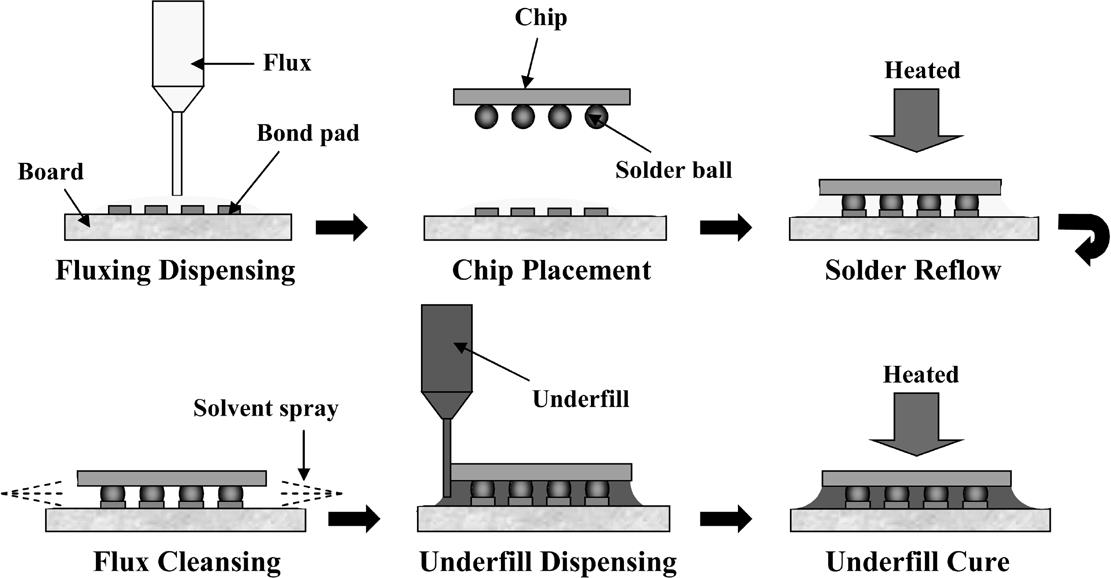

底部填充工艺在倒装芯片上的应用

芯片底部焊接不良失效分析

芯片底部焊接不良失效分析

评论