》nameWhenByFile

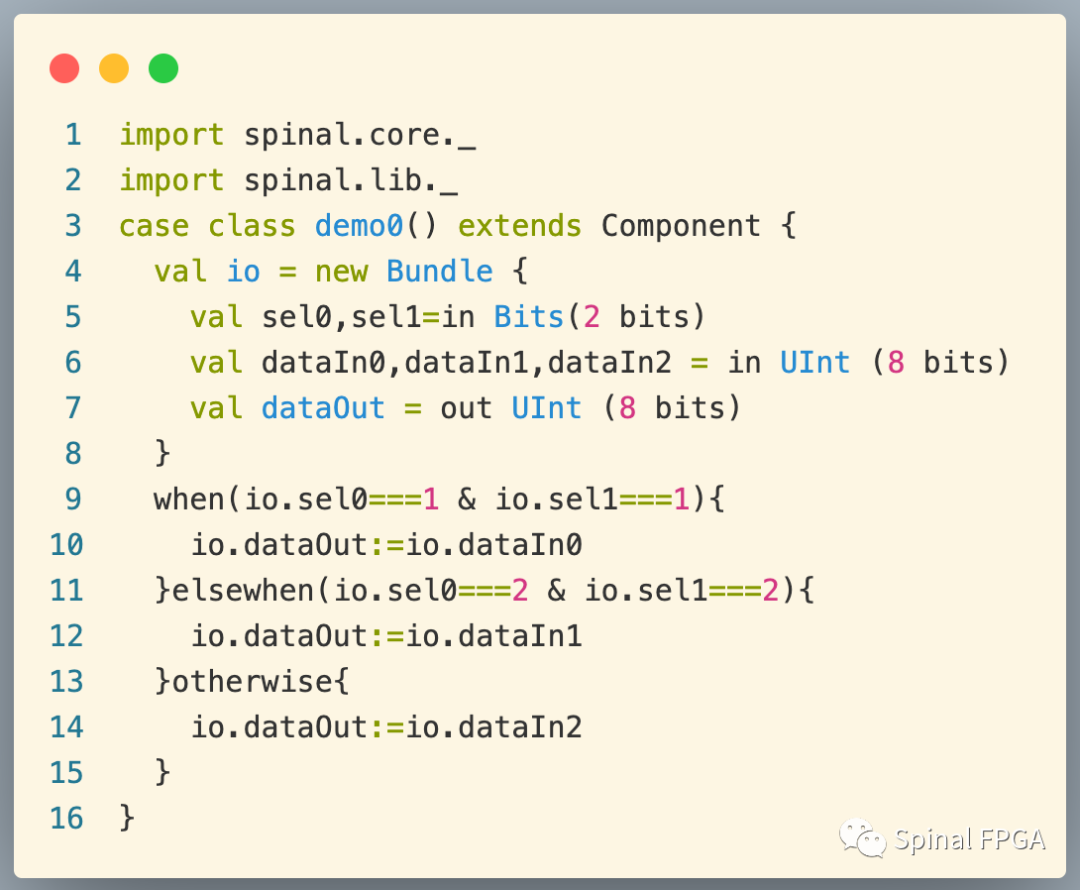

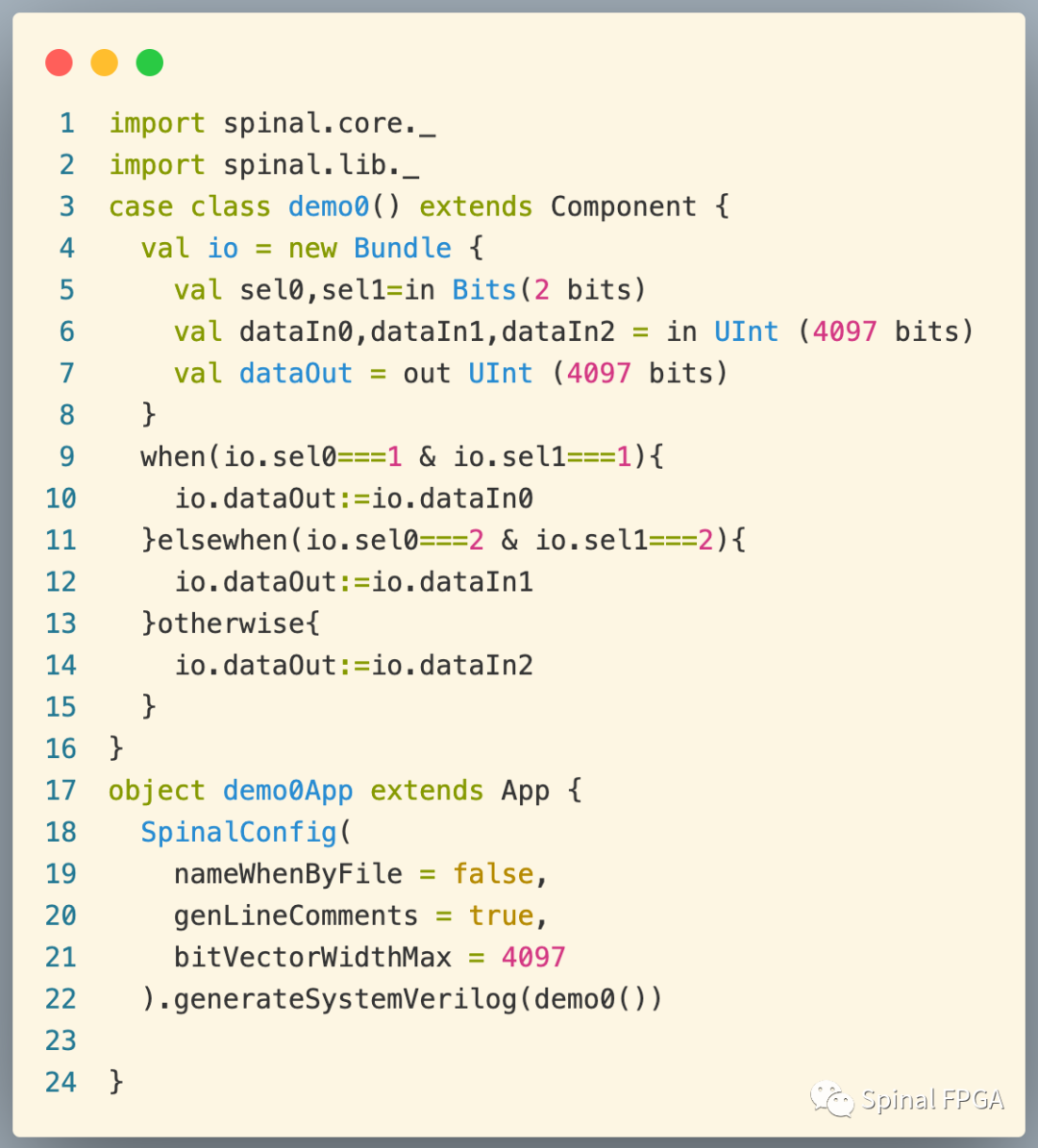

测试代码如下:

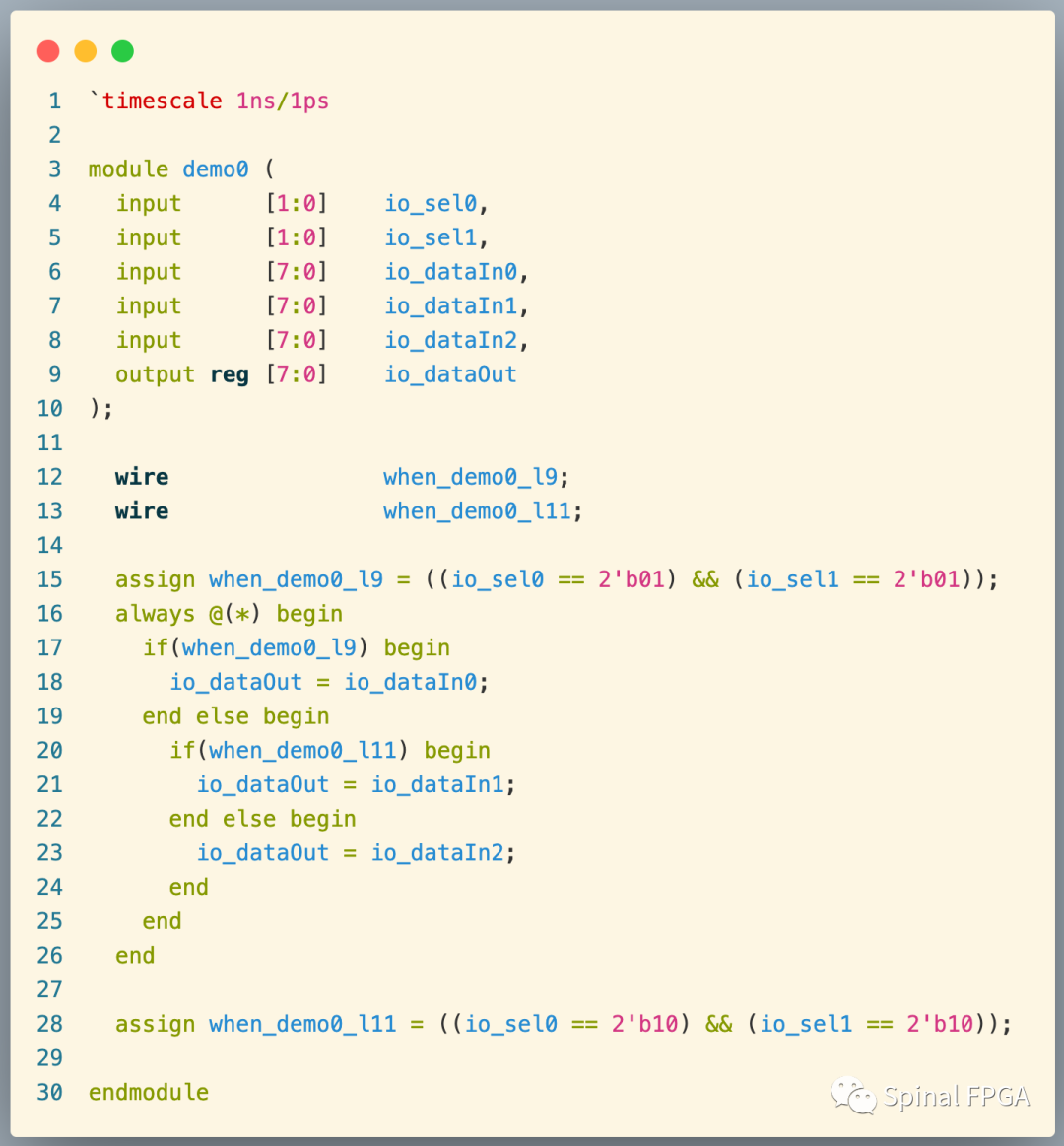

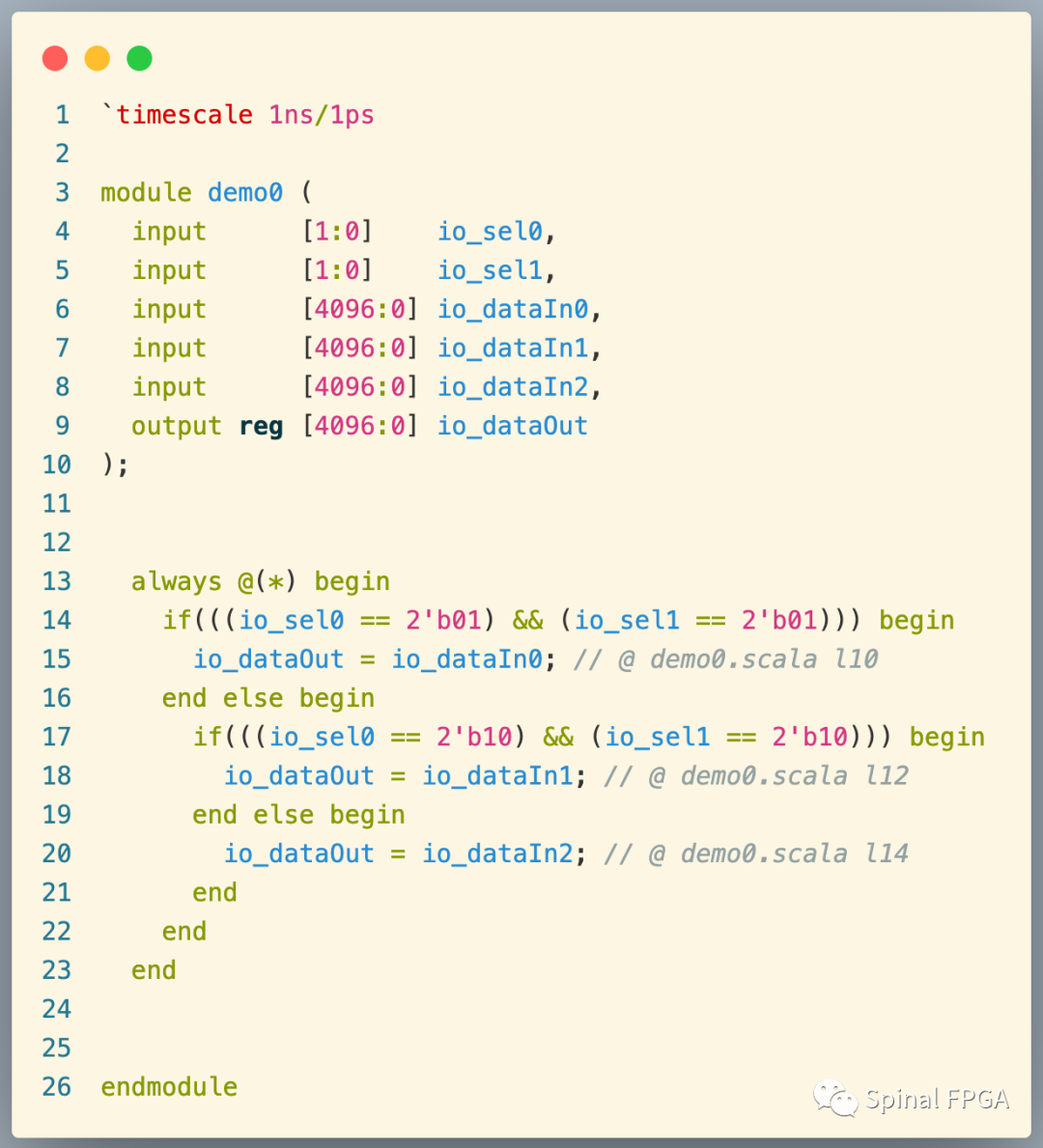

当我们采用SpinalSystemVerilog(demo0())的方式生成RTL代码时其生成的代码风格如下:

在SpinalHDL中对于when的使用,when中所包含的条件往往会生成以一个when+fileName+行号的变量来替代,看起来无非代码多了几行,并不影响功能。

因为有行号的引入,我们一旦对SpinalHDL代码中这部分代码哪怕是添加了几行注释也会引起生成代码的部分修改,虽然不影响功能,但对于那些喜欢看RTL代码的人就显得略显得不爽了。

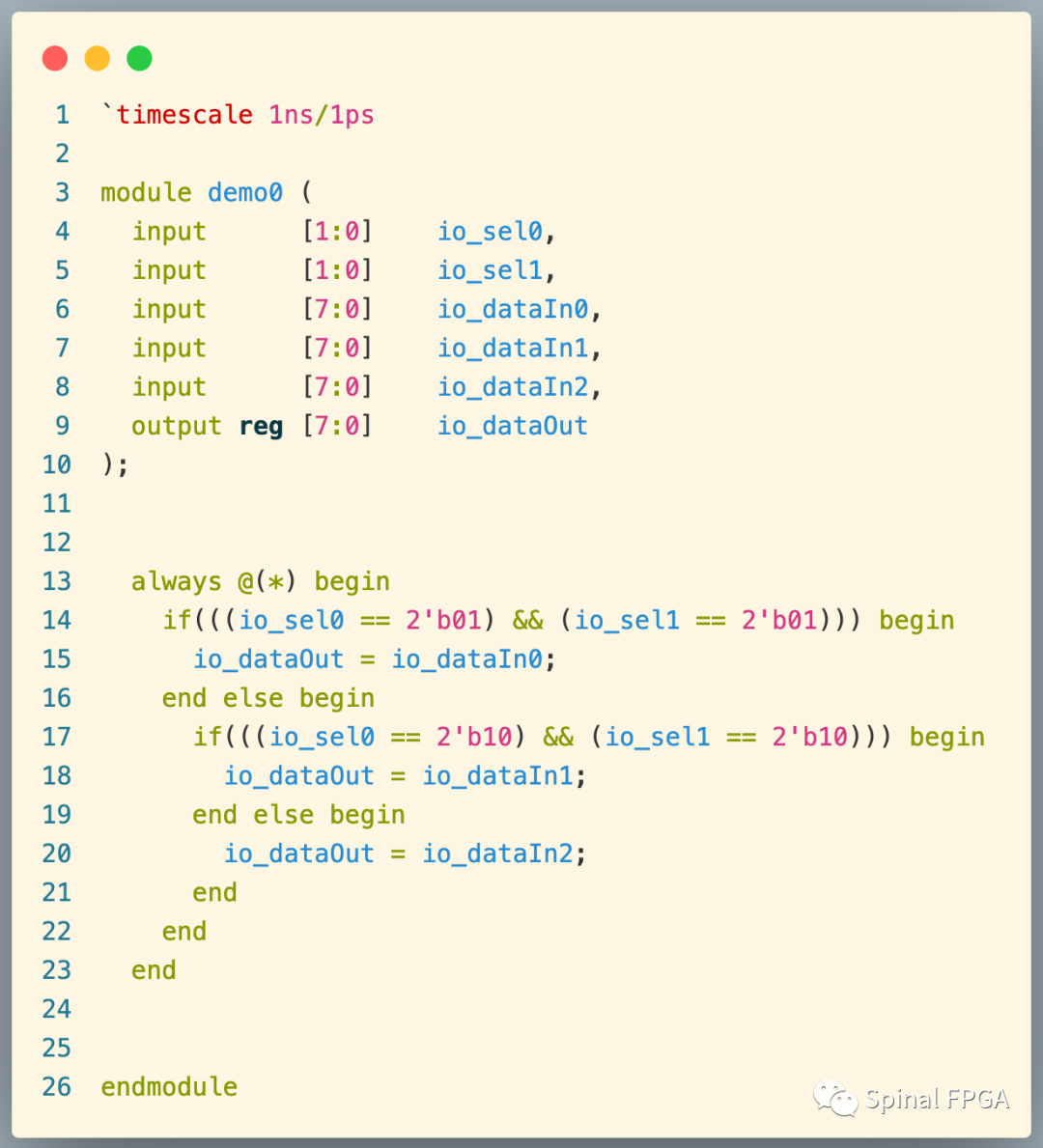

对于when的使用,可以在生成RTL代码时采用下面的形式来生成:

SpinalConfig( nameWhenByFile=false ).generateSystemVerilog(demo0())

生成代码如下:

如此生成的代码不会再对when语句声明单独的变量,代码看起来和那些采用Verilog写代码的人毫无差异吧~

这对于生层的RTL尽可能减少非必要的信号名称变化。

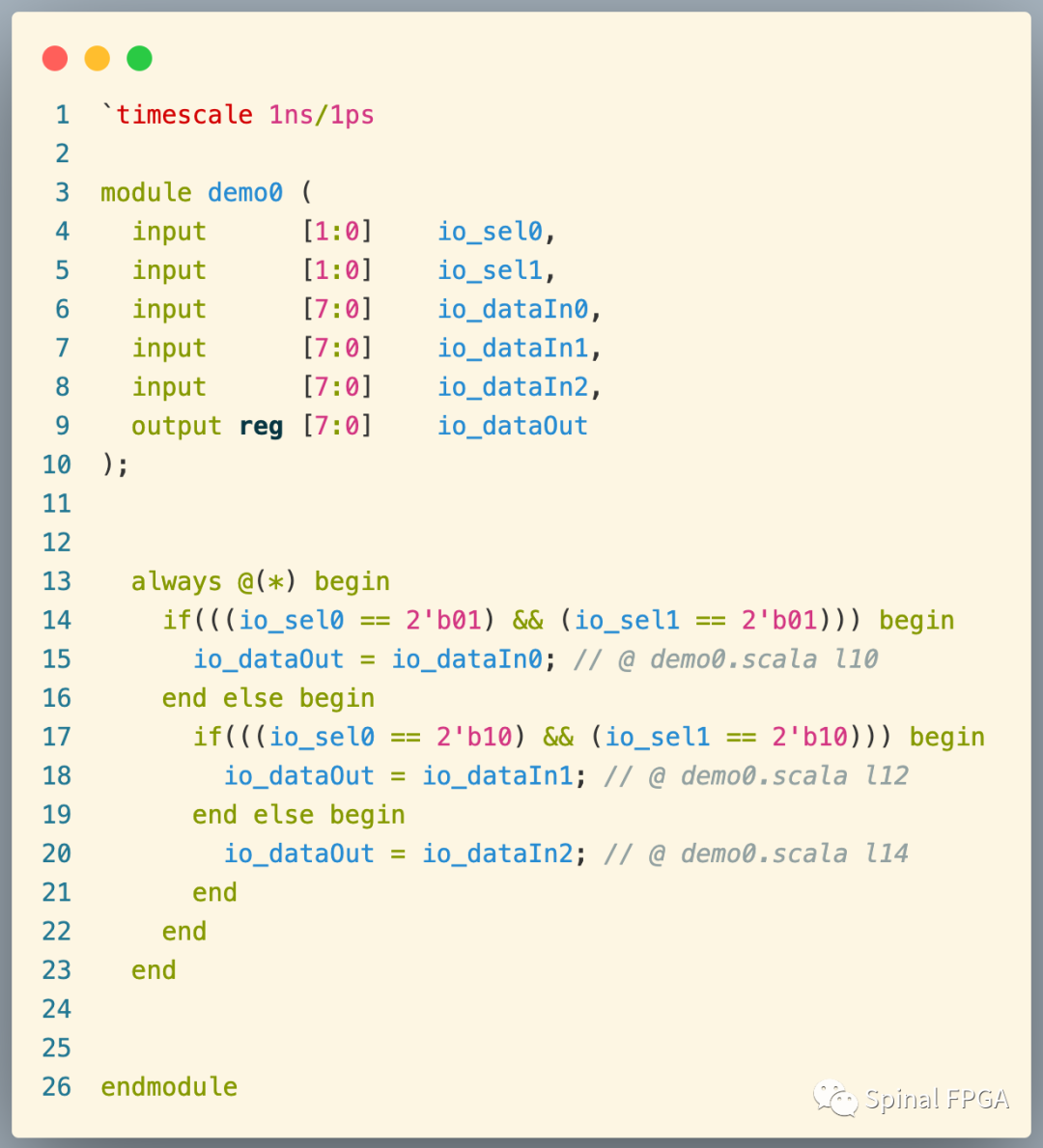

》genLineComments

更近一步,对于代码生成时采用下面的形式生成:

SpinalConfig(

nameWhenByFile = false,

genLineComments = true

).generateSystemVerilog(demo0())

此时生成的代码风格如下:

当genLineComments声明为true时,在生成RTL代码中会标注映射对应的SpinalHDL代码行号,这对于初学者在对比生成的RTL代码学习SpinalHDL还是非常的有帮助~

》bitVectorWidthMax

SpinalHDL中对于信号位宽默认是最大不超过4096(Intel DDR校准控制IP里面就有信号位宽就是4096 bit位宽),当设计里定义了信号 位宽超过4096,则会在生成RTL代码时报错,可通过SpianlConfig中的bitVectorWidthMax对最大位宽进行修改:

审核编辑:刘清

-

DDR

+关注

关注

11文章

712浏览量

65339 -

Verilog

+关注

关注

28文章

1351浏览量

110095 -

RTL

+关注

关注

1文章

385浏览量

59783

原文标题:SpinalConfig Tips——让代码优雅点儿

文章出处:【微信号:Spinal FPGA,微信公众号:Spinal FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

分享下SpinalHDL中SpinalConfig中的三项参数

分享下SpinalHDL中SpinalConfig中的三项参数

评论