1测试背景

USB总线自面世第一代开始,就对电气性能的要求特别高,特别是信号完整性。随着USB总线的不断升级,速率也是成倍的增长,从当年USB1.0的1.5Mbps,到后来的USB1.1的12Mbps,USB2.0的速率达到了480Mbps,USB3.0 Super Speed规范发布的时候已经高达5Gbps,在2015年,USB-IF协会更是发布了速率为10Gbps的USB3.1版本。如此高的速率对于设计中任何一点的瑕疵都是难以接受的,比如电源干扰、布线过长、线缆、连接器品质不好等等。USB版本的升级,不仅仅是信号速率的提升,原本只有一组信号线,也在USB3.0之后也增加到了三组信号线,信号的幅值也变得更低。这些综合在一起因素给产品硬件工程师在设计和测试验证时带来了非常大的挑战。

2 USB3.0简单的原理框图

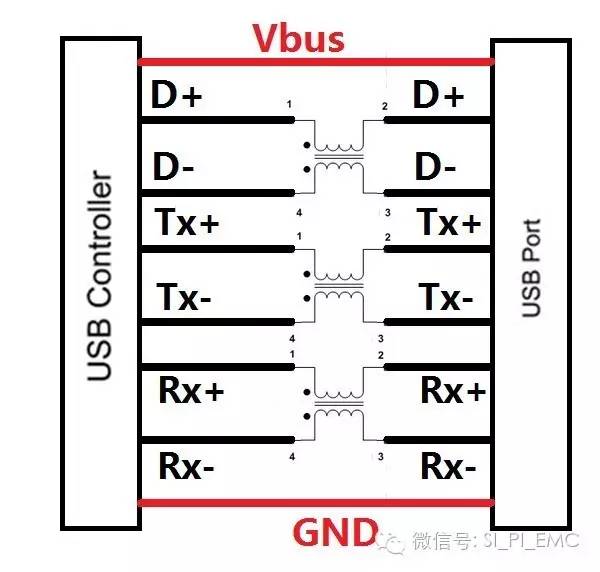

图1USB3.0简单的原理框图

USB3.0又称为SuperSpeed USB总线,与高速(High Speed)USB2.0总线相比,为了达到总线对USB2.0/1.1/1.0的向下兼容,总线保留了USB2.0信号线(D+,D-,Vbus,GND),同时增加了两对USB 3.0超高速差分信号(SSTX+,SSTX-,SSRX+,SSRX-),一组差分对用来发射信号,另一组接收信号,从而实现全双工传输,USB3.0信号传输速率达到5Gbps;电流最大达到900mA;在EMC方面,为了达到降低EMI的影响,增加了SSC(扩频时钟)功能。

3测试系统搭建和介绍

任何测试系统的搭建都是以测试目的为导向的,在测试之前一定要明确测试的目的。对于完整的USB3.0信号完整性测试,需要对TX端和RX端都进行完整的测试,但是对于大多数厂商来讲,可能只能完成基本的TX端测试。我们这个测试也只对TX端进行测试,所以测试的系统就是一台示波器、DUT、测试夹具和测试线缆。如下所示:

图2测试系统

示波器:Keysight Infiniium DSO90804A,带宽为8GHz,采样率为40GSa/s;

测试夹具:Keysight U7242-66501 USB3.0 test fixture

线缆:18GHz SMA头的线缆

测试软件:KeysightU7243B USB3 Test App

Keysight的USB 3.0 发送端一致性测试软件U7243A可以支持嵌入(Embed)、去嵌入(De-embed)的功能,这对研发工程师的作用非常大。在软件中还直接内置提供Host和Device的一致性通道传递函数,可以嵌入一致性通道模型,完成对一致性测试的要求,这主要体现在包含了测试过程中加入了长通道和短通道的S参数在其中,这时不管你是做的Host端的产品还是Device端的产品,只要在测试时选择对应参数即可代表真实的使用情况。这样也符合一致性测试规范。

4测试过程

Keysight示波器对于USB3.0这类接口的测试都有非常完善的测试解决方案,这些方案都是标准流程化的,只要进入到软件测试界面即可按照流程图一步一步的往下进行测试。下面是测试时的相关设置和注意事项:

在测试前,首先要预热、校准示波器(大约20分钟)、线缆需要做de-skew。这一步非常的关键,特别是线缆做de-skew,因为很多时候线缆与线缆之间有一些偏差,如果不做de-skew就会导致在差分信号的正端和负端引入系统误差。

然后就开启测试USB3.0软件U7243B USB3Test App,如下所示:

图3开启测试软件

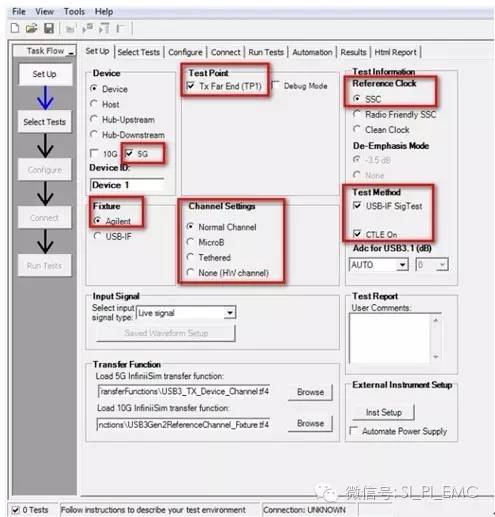

接着就是设置DUT类型、速率、夹具和测试分析模式,由于DUT是device,所以在Device一栏选择Device;USB3.0的速率为5G;测试的夹具分为了两类,一类是USB-IF协会的,另一类就是keysight(Agilent)的,在这里选择的是keysight(Agilent)的测试夹具;另外一个非常关键的点就是Test Method,是否选用USB-IF SigTest的分析方法,通常,我们会选择使用;选择参考时钟,一般高速串行信号都会选用SSC模式;还要根据产品使用。

图4 keysight示波器设置界面

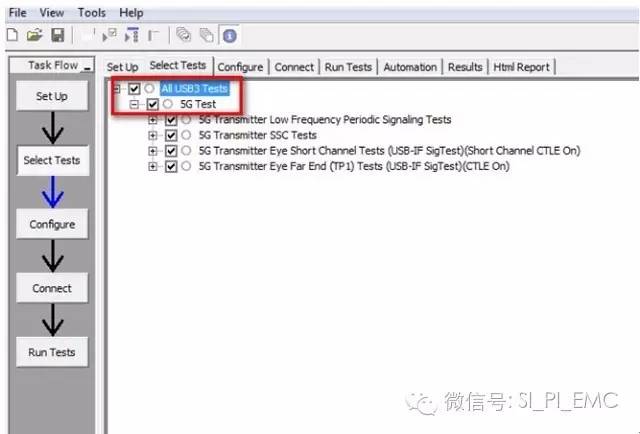

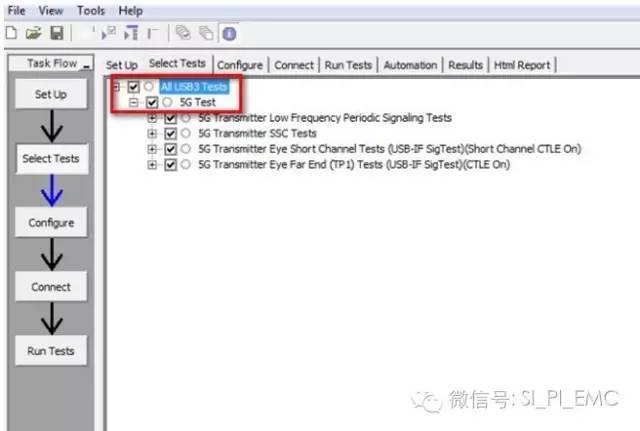

选择测试项目,一般情况,工程师都会选择全部测试项,这样才能最完整的按照规范要求进行测试,当然,这也要看测试目的,如果只是debug,那么可以选择相对应的选项即可,这样可以节约测试时间。具体操作如下图所示:

图5选择测试项目

配置测试条件。一般使用默认设置,常用的调整配置item有:使用的示波器通道,测试码型,测试的UI数,自动切换测试码型。如下图所示:

图6配置测试条件

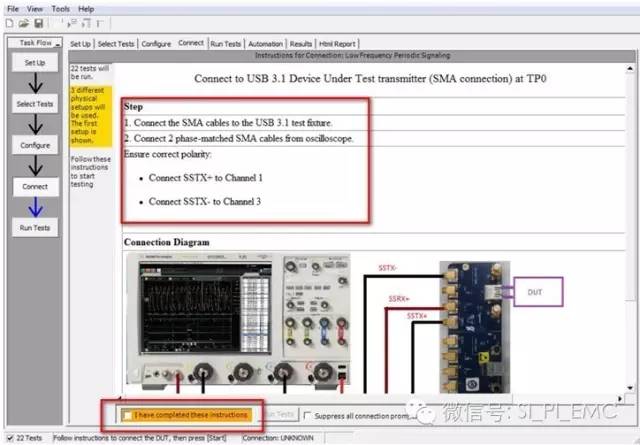

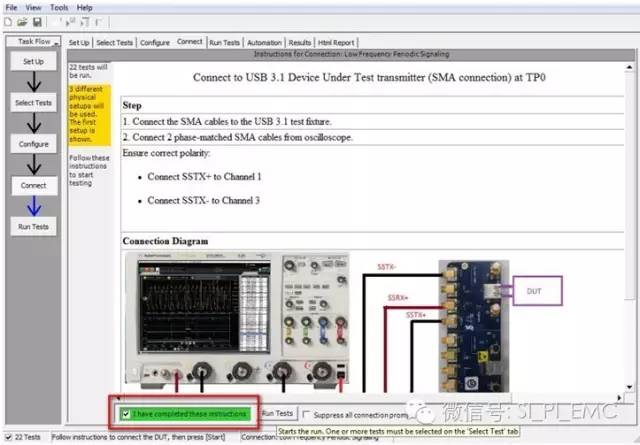

连接测试系统,包含示波器、夹具和DUT。测试软件会指示工程师的每一步连接,连接完成后,这里要注意,在连接完成之前,左下角的颜色是黄色的,连接完成之后,勾选’ I have completed theseinstructions’,就会变成绿色。如下两图所示:

图7连接测试系统

图8连接完成后

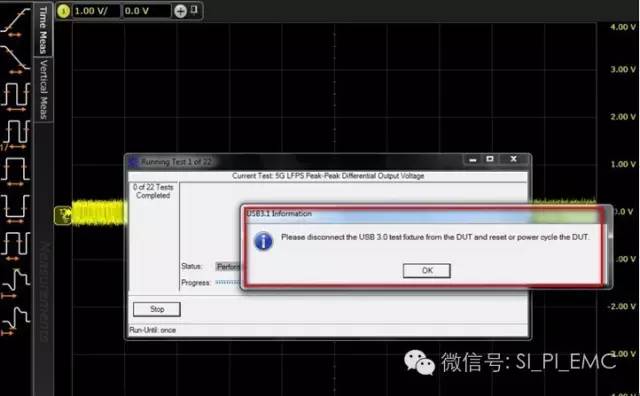

最后,单击Run test。软件会自动开始测试,但是要随时注意软件的提示,按提示进行一些触发动作等等。

断开被测件和夹具,然后重启被测件,完成这两个操作后,点击OK。

图9重启DUT

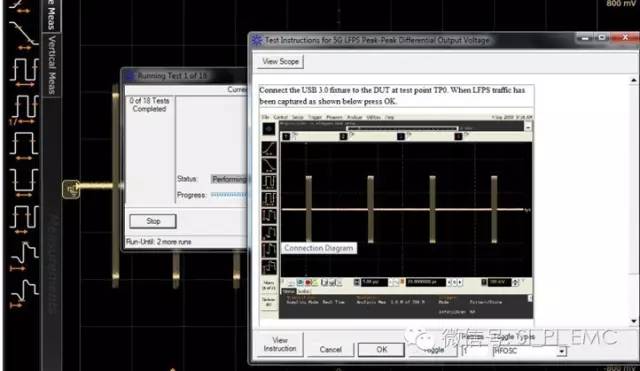

将被测件接入夹具,观察示波器是否捕捉到参考波形,如参考波形和示波器显示波形相同,点击成这两个操作后,点击OK

图10 测试TP0

完成LFPS信号测试后,软件提示更改连接,注意:此时提示连接夹具的’SSRX+‘和示波器的AUX OUT。

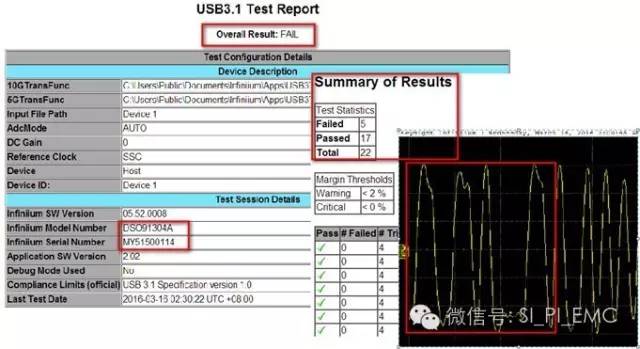

测试完成之后软件会自动生成报告,如下为部分测试报告内容:

图11测试报告内容

在报告中包含了测试的结果、波形和眼图以及SSC相关内容。对测试项也有比较清晰的说明,这非常有利于理解测试报告以及问题的分析。

5问题描述和结果分析

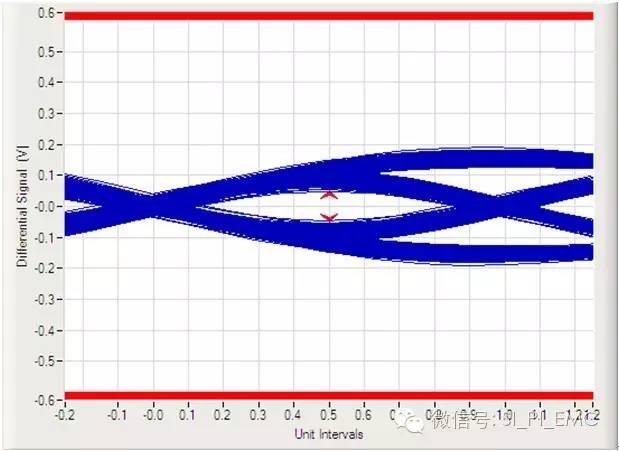

由于这个项目在上一版本的时候是没有任何问题的,所以在新版本生产好之后没有及时的对USB接口进行测试,当在产线上进行系统测试时,发现时断时续的读取不到device。然后分析USB口的电源和信号完整性是否满足设计要求,测试之后发现,电源是没有问题的,但是USB3.0的信号完整性确实存在问题,测试眼图如下:

图12原始眼图

从眼图分析,出现了眼图压到内模板。出现这种情况首先想到的就是另外再测试其他的产品,发现结果都是一样;接着就考虑是链路上的损耗是否变大?由于CPU芯片、连USB连接器和PCB材料都使用的是相同的物料,唯一改变的物料就是共模电感。上一版本的共模电感为M公司的物料,为了降低产品设计成本,新版本使用的是Y公司的物料,有可能问题就出现在这颗物料上。

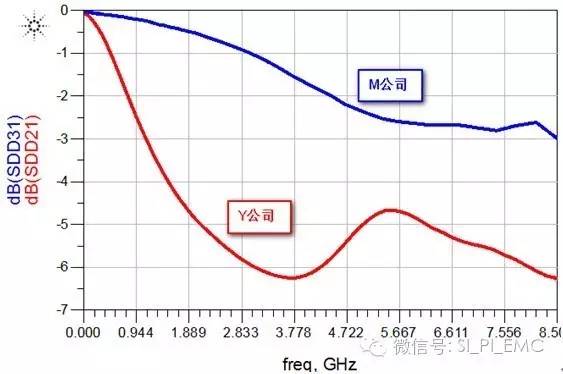

不同点找到之后,要求Y供应商提供物料的S参数,然后对比两家的参数如下:

图13对比两家物料的S参数(使用Keysight公司的仿真软件ADS)

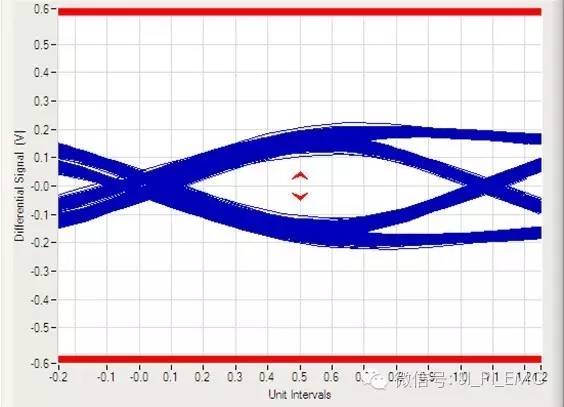

从对比结果上分析,很显然Y公司的物料与M公司的物料存在很大的差异性,在频率为一开始就差距很大,Y公司的物料在3.778GHz时有一个比较大的谐振点,损耗降到了-6dB以下,而M公司的物料损耗一直都保持在-3dB以上,显然,用在电路上会有一个非常大的差异。通过更换物料之后,再进行信号完整性测试,眼图如下:

图14改善后的眼图

对比两个眼图的参数,发现结果得到很大的改善。再进行系统测试,插拔100次都没有再出现读取不到device的现象。

6总结

在这个项目中,由于硬件研发工程师在换物料之后,没有及时的告知相关部门进行可靠性和电气性能的评估,单纯从数值上就确定使用物料,这就导致了USB3.0口无法正常读取到device。在通过使用Keysight的一系列的硬件和软件工具验证之后,最终问题得以找到点,并解决。

审核编辑 :李倩

-

usb

+关注

关注

60文章

7928浏览量

264404 -

信号完整性

+关注

关注

68文章

1403浏览量

95454

发布评论请先 登录

相关推荐

信号完整性实战:USB3.0

信号完整性实战:USB3.0

评论