本文主要给大家分享一下PCIe5.0的发展历程、以及在设计、仿真中一些挑战和如何进行仿真。--蒋修国

1、PCIE 发展历程及PCIE 5.0的发布

作为PC系统中最重要的总线, PCI Express由Intel于2001年提出,用于替代PCI总线,以满足更高的带宽和吞吐量需求。

由上面的图表可以看到,为了满足日益增长的信息传递速率,每一代PCIE标准在速度上都几乎是成倍增长。

目前,由于 PCIE 4.0拥有相较于前代PCIE 3.0两倍的16GT/s传输速率,其被广泛应用于超算,企业级高速存储,网络设备等产品中。而去年年中,AMD发布了支持PCIE4.0的7nm锐龙3000系列处理器,正式将PCIE4.0带入了消费级平台。

随着人工智能威廉希尔官方网站 的飞速发展,对运算能力的需求不断提升,高速总线也面临着更大的挑战。因此,在PCIE 4.0发布仅仅两年后,PCI-SIG便于2019年5月发布了PCIE 5.0规范。相比较之前PCIE 4.0的16GT/s,PCIE5.0 将信号速率翻倍到了32GT/s,x16双工带宽更是接近128GB/s。极高的信号速率,使得PCIE5.0能够更好的支持对吞吐量要求高的高性能设备,如用于AI的GPU,网络设备等等。

2019年底,Intel便出货了支持PCIE 5.0的Agilex FPGA,也拉开了PCIE 5.0时代的大幕。

2、PCIE 5.0主要指标

由于速率的翻倍,PCIE 5.0在均衡,损耗等指标上,与前代均有较大差别。

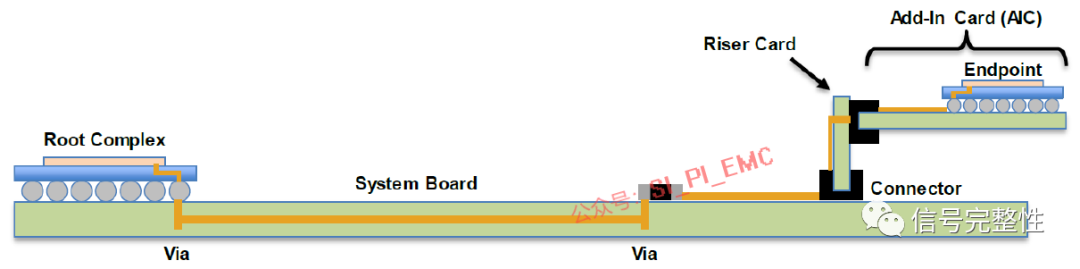

(1)、拓扑结构

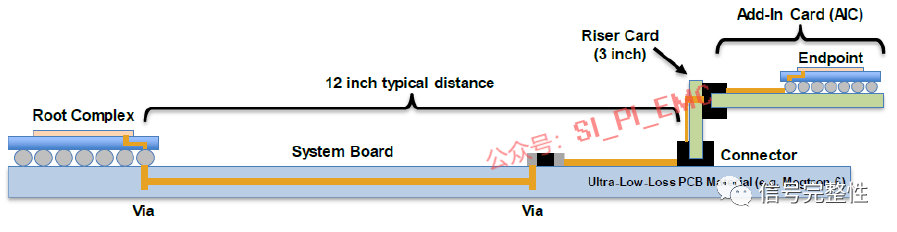

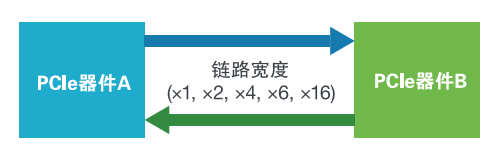

上图展示了基本的双连接器PCIE拓扑结构,这种结构被广泛应用于服务器、存储和加速器系统。

在PCIE 5.0中,当线路损耗过大,或使用多个连接器时,可以在信号拓扑中加入Re-timer以提高系统信号质量。关于加入Re-timer后的拓扑结构,在之后的章节会有具体的介绍。

(2)、损耗

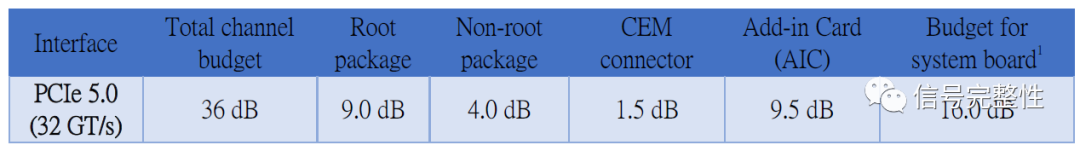

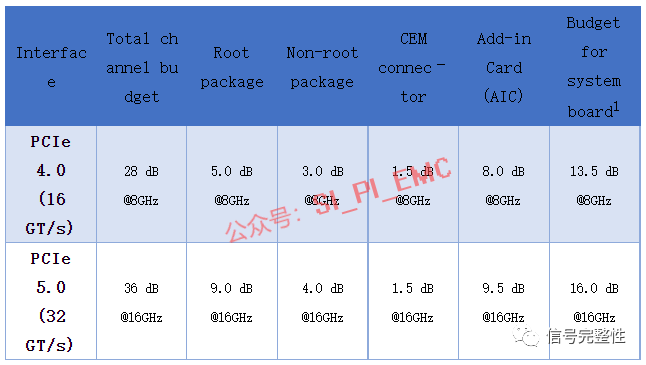

上述拓扑结构中包括各种损耗组件,而PCIe 5.0已经为这些组件制定了如下的损耗预算。可以看到,整体通道的损耗在16GHz时不能高于36dB。

1System Board budget includes the baseboard,riser card, the baseboard-to-riser-card, and PCIe card electromechanical (CEM)form factor connectors.

(3)、均衡

PCIE 5.0在发射端和接收端都使用了均衡威廉希尔官方网站 来提高信号质量。

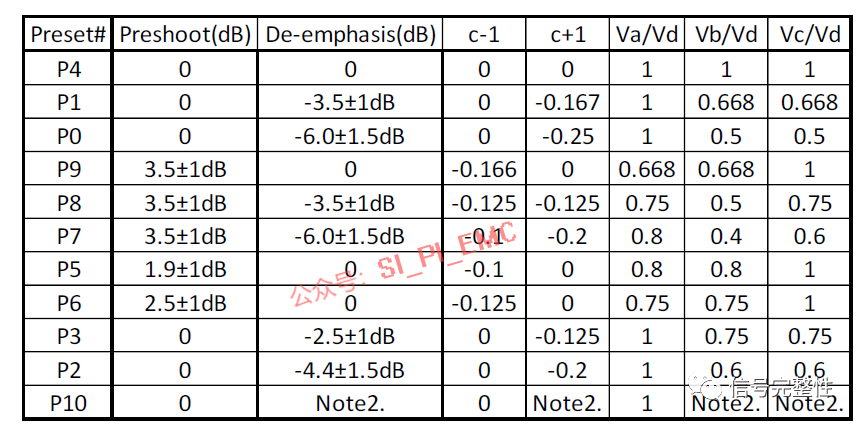

A.Tx EQ

在发射机端,PCIE 5.0沿用了PCIE 4.0的三阶FIR滤波器(如下图所示),通过对信号高频分量的抬高和低频分量的减少来弥补这一影响。

B.RX EQ

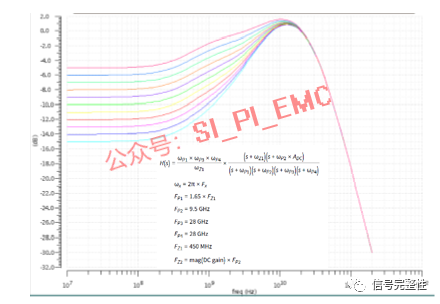

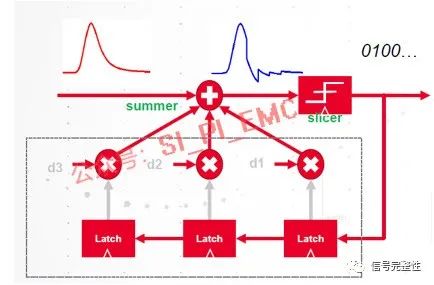

与Tx均衡不同,在接收端,PCIE 5.0对PCIE 4.0的均衡进行了升级,二阶CTLE和三阶DFE被用来替换前代的一阶CTLE和二阶DFE,以应对更高的信号速率,使闭合的眼图张开。通过CTLE可以减小由更高频通道损耗造成的影响。而DFE则可以进一步减少ISI带来的影响。

2-order CTLE

3-tap DFE

通过使用以上威廉希尔官方网站 ,也促使PCIE 5.0在PCIE 4.0的基础上实现了速度翻倍(这并不是是唯二的威廉希尔官方网站 ),同时,其信号延迟和编码开销也大幅优化。

3、PCIE 5.0 设计面对的挑战

(1)、无源通道设计

在2.2中介绍到PCIE 5.0对整体信道的损耗有严格的要求。下表中对比了PCIE4.0在16GT/s速率下,与PCIE 5.0在32GT/s速率下的损耗要求。

可以看到,虽然PCIE 5.0的速率提高了一倍,损耗要求却没有下降太多。这意味对设计的损耗控制要求提高了几乎一倍。使用低损耗或超低损耗的材料的固然使减少损耗的一个方法,但其在降低了损耗的同时,也大大提高了产品的成本。如果能够在使用较低成本材料的同时,通过对叠层,传输线结构的调整,达到符合要求的通道性能,无疑能使产品获得更大的竞争力。平衡成本与性能之间的关系,将成为工程师们不得不面对的挑战。

(2)、Repeater使用

PCIe 4.0对通道损耗的要求是8GHz小于28dB,而PCIE5.0则是16GHz小于36dB,若大于这些值,接收机不能保证可以正确地解出信号。控制损耗固然是解决方法之一,但对于损耗过大的设计,受到产品结构,尺寸和成本的限制,留给工程师的优化空间往往十分有限,因此Repeater被使用来给予看似绝望的设计一线生机。

Repeater的目的是为了避免抵达接收机的信号恶化太严重以至于无法被正确识别,在信道中提前对信号做处理。以PCIe 5.0为例,因成本的考虑不能用太贵的板材,若初步的通道设计差损48dB@16GHz,为了让信号可以正确地传送,可以选择在通道中间加上Repeater,这样就可以把通道的设计拆成两半,Repeater和RX各分担24dB@16GHz的差损。关于Repeater的使用我们会在后面作更深入的探讨。

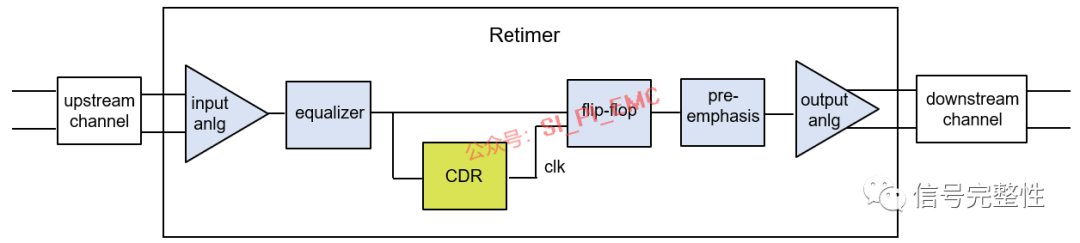

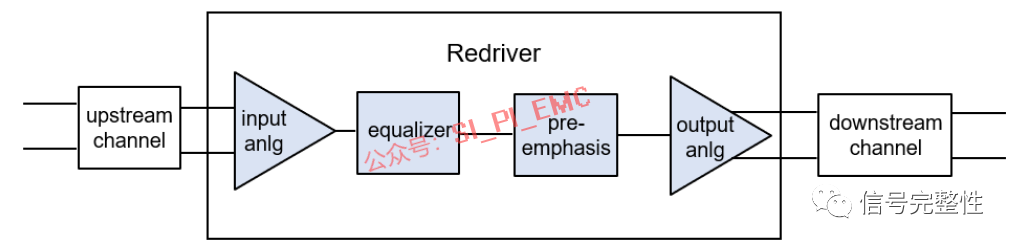

Repeater是由一个RX加上TX芯片所组成,而依信号处理方式的不同分为两类,Retimer和Redriver。

A.Retimer

有CDR(Clock Data Recovery,时钟恢复),若TX到该Retimer之前的通道设计符合Retimer的规范,则信号可以被正确的还原,之前的通道损耗和抖动都可以被Retimer消除,因此就像TX的位置被移动到Retimer,对SI工程师来说,信号就可以走得更远了。

B. Redriver

没有CDR,因此只能补偿信号的衰减,无法去除抖动。

4、应对PCIE5.0设计挑战

针对以上提到的设计难题,就需要一套非常完整的仿真方案来解决。

(1)、无源通道设计

在前面介绍到,无源通道的损耗是PCIE 5.0设计中的一大挑战。为了平衡成本与性能,工程师需要进行大量的预研,在layout之前评估出适合的PCB材料,传输线和叠层结构等。在使设计符合协议要求的同时,尽可能降低产品的成本。

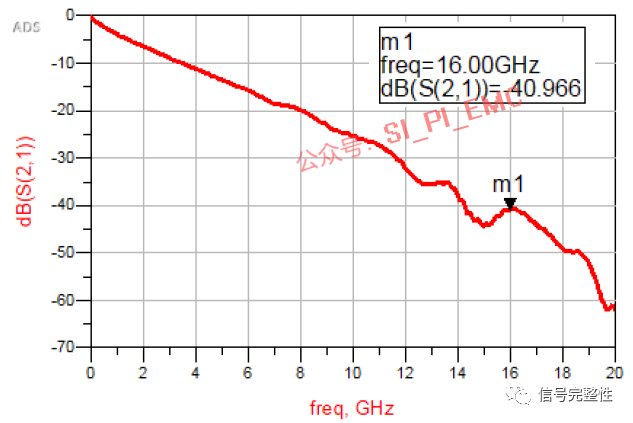

而针对设计完成的layout,工程师需要准确的提取其中的S参数,用于验证通道损耗是否符合设计要求。由于PCIE 5.0的奈奎斯特频率高达16GHz,工程师需要一款能够在高频情况下准确高效提取通道S参数的工具。

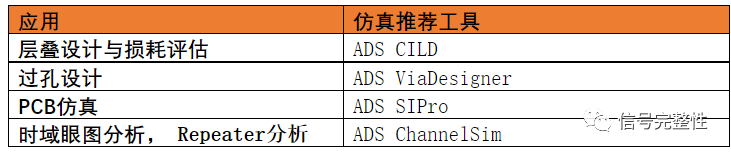

在ADS中,CILD和SIPro两个工具,可以分别满足layout前、后的设计验证要求。

A.传输线结构设计(Pre-layout)

工程师在正式layout之前,需要预先确定设计的叠层,材料和走线结构。为了控制产品的成本,超低损耗材料往往无法很普遍的被使用。受到材料的约束,工程师更需要通过合理的叠层和线宽,线间距设置,降低通道的损耗。

这里,以Dk=3.8, Df=0.005的低损耗材料,core/pp介质厚度3/6mil,85ohm阻抗为例,对比不同的传输线线宽与线间距对损耗的影响。

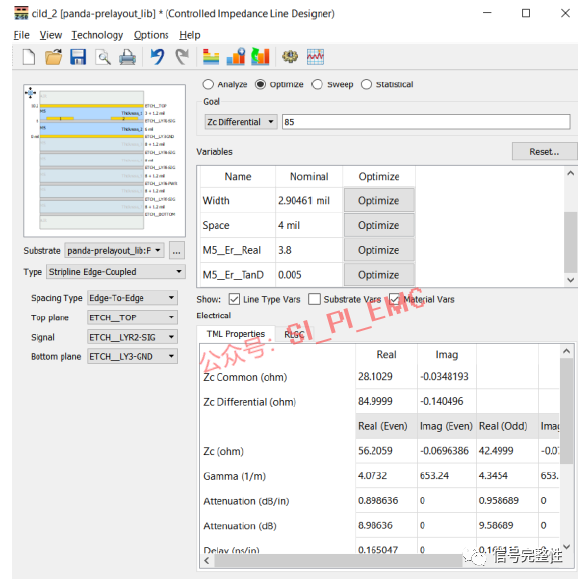

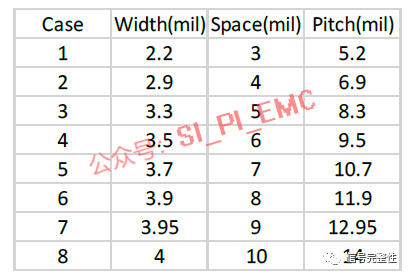

在ADS中,CILD是专门用于在layout前构建传输线结构,并仿真其主要参数的工具。在CILD中,可以通过设定目标阻抗,使用优化模式自动优化出符合阻抗要求的线宽和线间距。如下图中,统计出了8种不同的线宽及线间距组合。

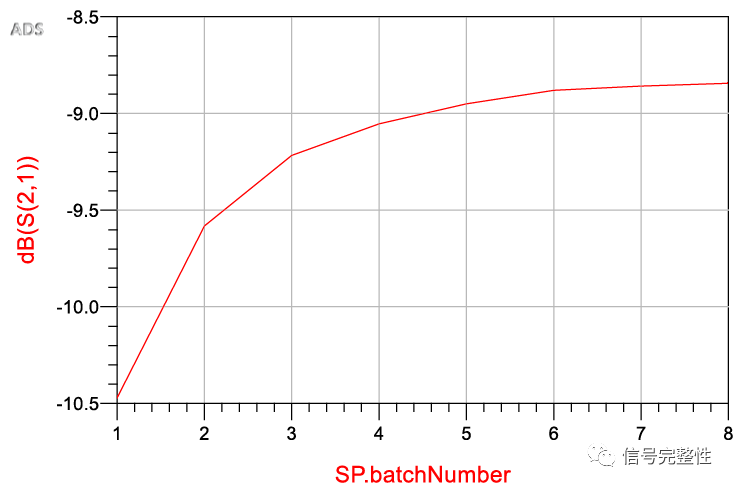

CILD的传输线模型还可以导入ADS原理图中,通过Batch Simulation对各种线宽线间距的组合进行扫描。如下图所示,对8种传输线结构都进行了仿真,得到了16GHz时的损耗。可以发现随着线宽的增宽,传输线的损耗逐步下降。4/10的情况下,相较2.2/3损耗下降了超过1.5dB。 考虑到case 4~7的pitch虽然增加了近50%,但是损耗仅减小了0.3dB。选择Case4或Case5的情况进行layout,既减少了损耗,又可以保证足够的走线空间。

除了线宽与线间距,CILD也可以考虑材料参数和叠层的变化。通过ADS CILD的使用,用户可以对传输线结构进行快速评估,获得设计参考。

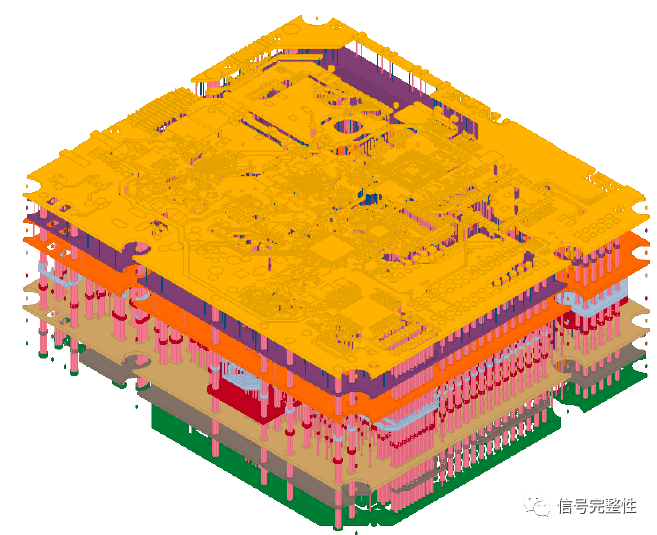

B.Layout EM验证(Post-layout)

完成layout之后,工程师需要使用电磁仿真工具提取PCB的S参数对设计进行验证。由于PCIE 5.0的高速率,工程师使用的电磁仿真工具需要能在高频段也能快速准确提取出S参数。同时,设计中往往会使用背钻来解决过孔stub的问题,因此也要求电磁仿真器能准确提取该部分信息。

ADS SIPro是一款专用于PCB仿真的电磁仿真工具。其使用独有的混合算法,可以快速提取信号走线(包含过孔)的频域模型,验证设计完成的layout性能。这一频域模型可以直接转换成ADS 的原理图,用于电路仿真,如时域瞬态仿真,通道仿真等。同时,ADS 提供了过孔设计工具ViaDesigner,使用FEM进行过孔结构的仿真设计。

(2)、Repeater应用

前文提到过Repeater的工作原理,工程师往往需要判断Repeater的使用时机和方式。通过ADS 通道仿真器,可以对是否使用Repeater以及Repeater的摆放位置进行规划与验证。

A.是否需要使用Repeater

这里提供两种判断方式,方法I比较简单但较粗糙,方法II适用于获得芯片的AMI模型的情况,可以得到很接近真实的眼图,建议初期先用方法I做系统规划,再用方法II来验证。

I.损耗评估法

通过S参数仿真,比较通道损耗(包括封装)和PCIe规范的损耗标准,若通道损耗超过标准,则建议使用Repeater。

II.统计眼图法

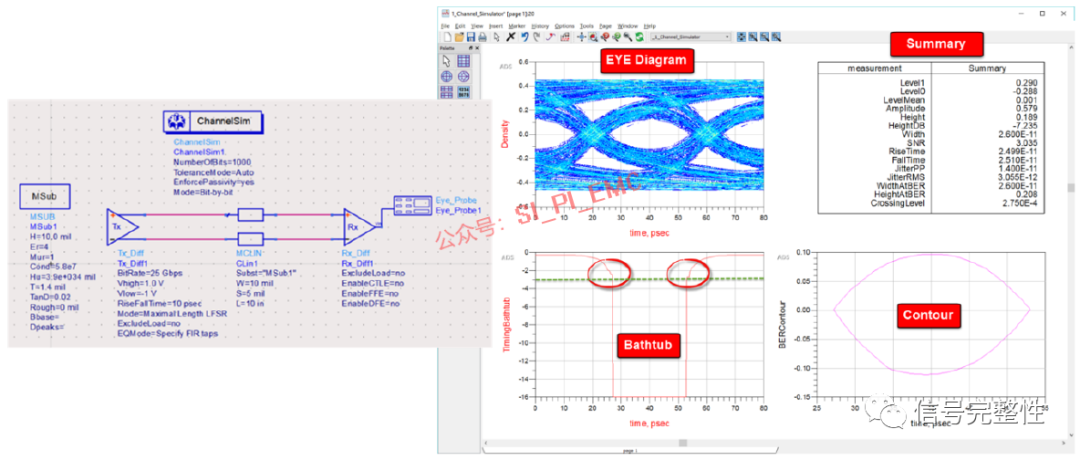

ADS通道仿真器(ChannelSim),用于分析经过通道后的信号质量。通道仿真器具有两种模式,Bit-by-bit和Statistical,是目前串行接口链路的主流仿真工具。

以下探讨是否有AMI模型的判断方式。

-没有AMI模型

把通道的S参数带入通道仿真器(ChannelSim),并设定PCIe协会对芯片规范的Jitter和EQ(De-emphasis, CTLE, DFE),找出最好的EQ组合,若该组合不能符合协会订定的眼图张开标准(5.0, 眼高15mV,眼宽0.3UI),建议使用Repeater。

-有AMI模型

不用自己设定Jitter和EQ,且眼图张开标准有可能会比协会订定的还宽松(例如眼高10mV,眼宽0.2UI,比协会规范的EYE MASK还小),这取决于RX芯片的算法能力,建议参考RX AMI模型的应用文件。若仿真得到的眼图张开不能符合该RX AMI建议的值,建议使用Repeater。

B.Repeater的摆放位置

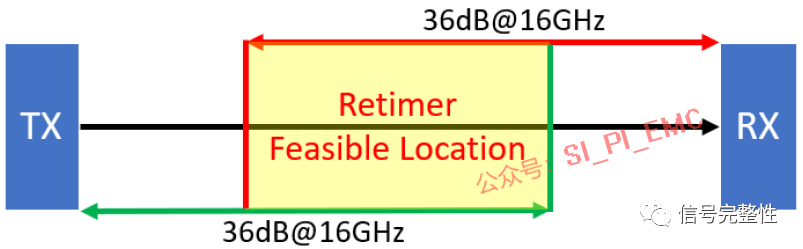

Retimer

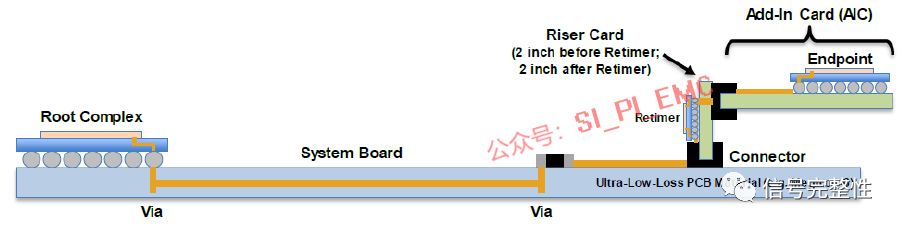

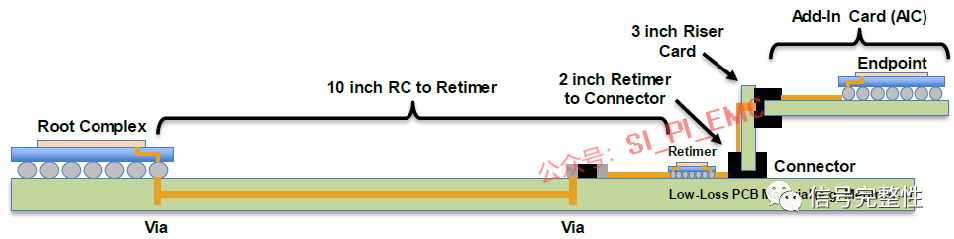

由于Retimer送出的信号已经将信号时钟对准,可以把Retimer位置视为新的TX位置,并针对协会对损耗的规范来摆放Retimer。通过损耗评估法,得到以下的黄色区间是适合摆放Retimer的位置,在该区间符合TX to Retimer和Retimer to RX之间的通道差损小于36dB@16GHz。

一旦决定Retimer的位置后,可以将两段S参数(TX to Retimer和Retimer to RX)连同Retimer AMI模型用通道仿真器来判断最后RX的眼图是否符合该RX的要求,若不符合要求,可以前后调整一下Retimer位置后,再用通道仿真验证,直到RX的眼图符合该RX的要求为止。

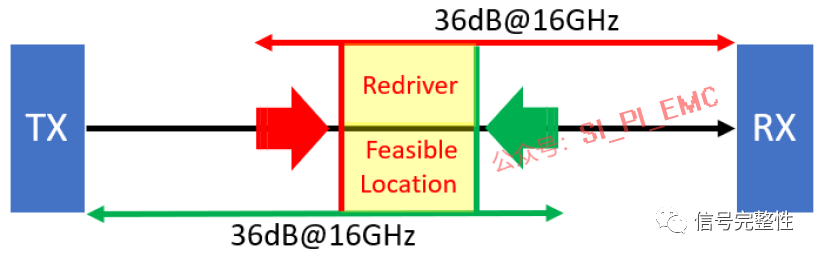

Redriver

由于没有CDR,因此在评估时无法将Redriver的位置视为新的TX位置,因为从Redriver送出的信号会带有之前信道累积的Jitter。有了这样的认知,我们在判断Redriver的位置就应该更加保守,类似下图。

确定位置后,一样也需要透过信道仿真器来判断RX的眼图是否符合RX规范。

Repeater加在Baseboard还是Riser Card上?

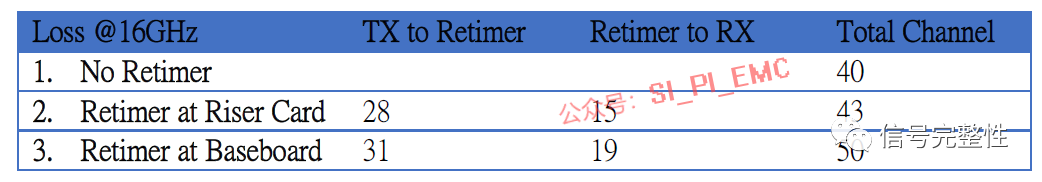

以下两种常见的Repeater摆放位置(Topology 2 and 3),最后仿真结果也都远优于协会规范,这表示在系统设计上还有许多优化空间,例如可以选择较低成本的板材,或是走线可以走得更长。

Topology 1 - 无Retimer,Baseboard用Ultra-Low-Loss板材

Topology 2 - Retimer加在Riser card上,Baseboard用Ultra-Low-Loss板材

Topology 3 - Retimer加在Baseboard上,Baseboard用Low-Loss板材

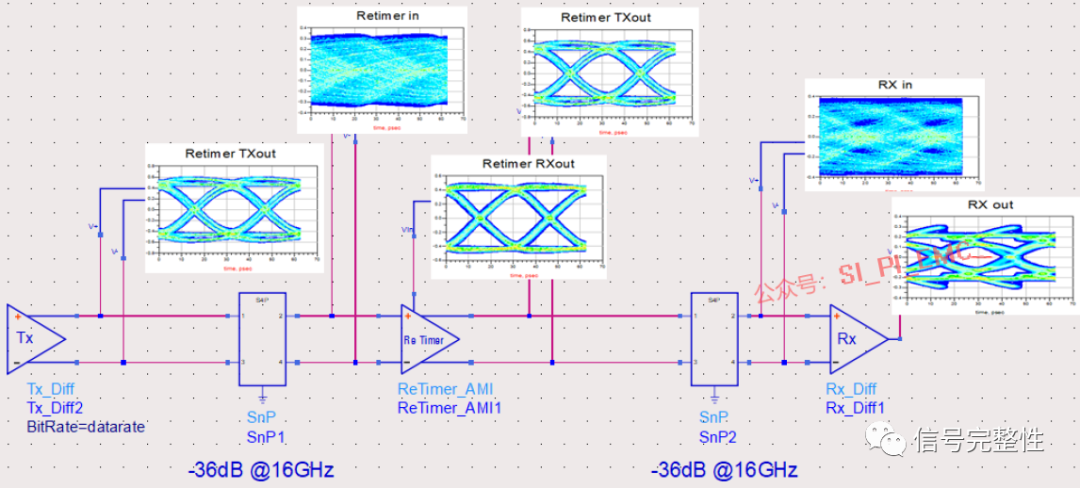

(5)、PCIe 5.0仿真实例

以下是我们基于PCIe 5.0的规范设定的Retimer测试模板。通过仿真结果我们可以看到,即使进到Retimer前的眼图已经完全关闭(Retimer in),但通过CDR以及均衡器的处理,再次送出张开的眼睛(Retimer TXout),来协助RX正确地显示眼图(RX out)。

(6)、PCIe5.0仿真推荐配置

审核编辑:汤梓红

-

仿真

+关注

关注

50文章

4073浏览量

133556 -

PCI

+关注

关注

4文章

666浏览量

130251 -

总线

+关注

关注

10文章

2878浏览量

88055 -

PCIe

+关注

关注

15文章

1235浏览量

82590 -

PCIe5.0

+关注

关注

0文章

17浏览量

1375

原文标题:PCIe 5.0 设计面临的挑战以及仿真案例

文章出处:【微信号:SI_PI_EMC,微信公众号:信号完整性】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

硬盘开启PCIe 5.0时代

移动电视射频威廉希尔官方网站 面临什么挑战

PCIe 4.0 SSD尚未起飞,就要迎战速度翻倍的5.0

PCIe 5.0时代正式拉开序幕

什么是 PCIe 5.0? PCIe 5.0规范以及挑战

microchip全新的PCIe 5.0交换芯片怎么样

PCIe 5.0之PCB设计及挑战

PCIe 5.0 SSD不用风扇会怎么样?

什么是PCIe?PCIe有什么用途?PCIe 5.0有何不同?

PCIe 5.0设计面临的挑战以及仿真案例

PCIe 5.0设计面临的挑战以及仿真案例

评论