在20nm 工艺节点之后,传统的平面浮栅 NAND 闪速存储器因受到邻近浮栅 -浮栅的耦合电容干扰而达到了微缩的极限。为了实现更高的存储容量,NAND集成工艺开始向三维堆叠方向发展。在三维NAND 存储单元中,电荷的存储层可以是浮栅或氮化硅电荷俘获层(Charge-Trapping Layer, CTL)。三维CTL垂直沟道型NAND 闪存(3D NAND 或 V-NAND)基于无结型 (Junctionless, JL)薄膜场效应晶体管(TFT),具有更好的可靠性。

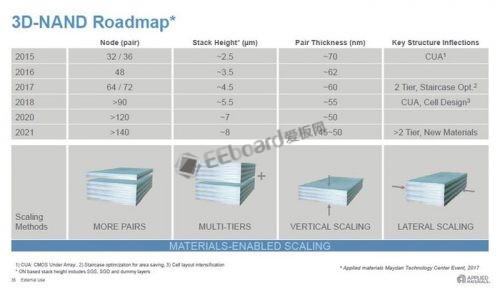

目前,国际上主流的 3D NAND 产品是韩国三星电子研发出来的,2013 年第一代产品(32~64Gbit)有24层堆叠的存储单元,2014 年第二代产品 (128Gbit)有 32层,2015 年第三代产品(256Gbit) 有48层,64层产品于 2017 年量产,128 层存储单元的3D NAND 产品目前已研发完成并量产。

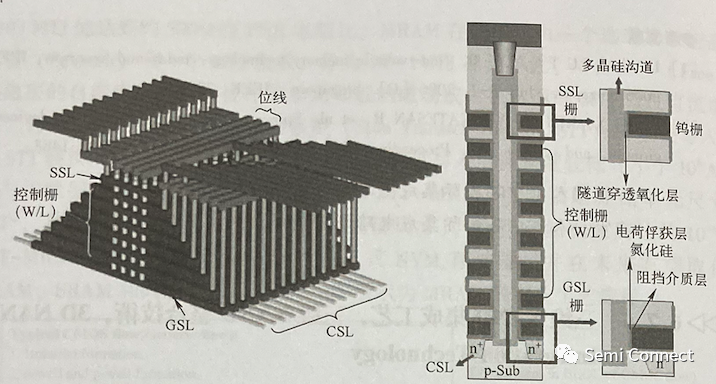

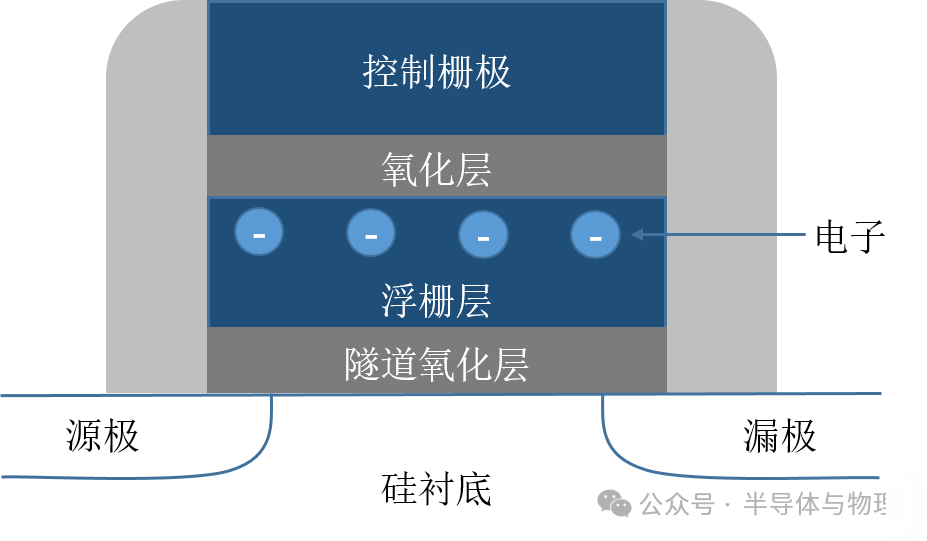

上图所示为3D NAND 闪存器件结构示意图。图中,底层的选通晶体管(CSL/GSI)为反型晶体管,其余每个存储单元的晶体管均为无结型薄膜晶体管(JL-TFT)。在晶体管关闭时,多晶硅薄膜沟道处于全耗尽状态,开关电流比大于10^6。存储层采用的是基于纸化硅的高陷阱密度材料(电子/空穴在存储层中的横向扩散会降低 3D NAND 的可靠性)。电荷存储单元之间的耦合效应低。写入 / 擦除操作分别使用电子和空穴的 FN 隧道穿透,隧道穿透层通常是基于氧化硅和氮氧化硅叠层材料结构的,阻挡层采用氧化硅或氧化铝等材料 (目的是降低栅反向注入)。3D NAND 存储单元的存储性能优异,具有写入 / 擦除快速,存储窗口大于 6V ,存储写入 / 擦除次数大于 10^4,以及在 85°C 下数据保持能力可达10年等优势。

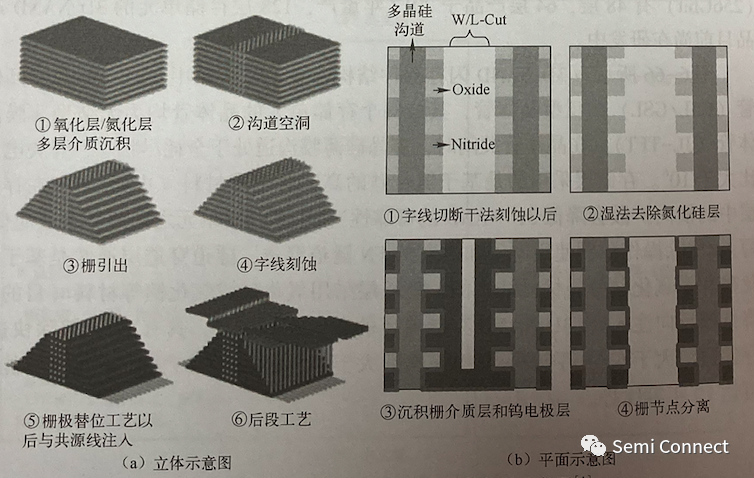

上图所示为 3D NAND 闪存器件制造工艺流程示意图。在完成 CMOS的源漏之后,开始重覆沉淀多层氧化硅/氮化硅,然后进行光刻和沟道超深孔刻蚀(深宽比大于30:1),沉淀高质量的多晶硅薄膜和沟道深孔填充并形成栅衬垫阵列(Gate Pad)。接下来进行光刻和字线刻蚀 一 离子注入形成 CSL 线 一 湿法去除氮化硅 一 沉淀栅介质和电荷俘获 ONO 薄膜(其特点是厚度和组分均匀,沟道 - 介质界面缺陷密度低) 一 沉积钨薄膜作为栅极,并刻蚀钨以分开字线。完成上述工艺后,继续进行 BEOL 工艺。

审核编辑:汤梓红

-

NAND

+关注

关注

16文章

1681浏览量

136124 -

存储器

+关注

关注

38文章

7484浏览量

163769 -

工艺

+关注

关注

4文章

592浏览量

28781 -

晶体管

+关注

关注

77文章

9684浏览量

138091 -

三维

+关注

关注

1文章

507浏览量

28967

原文标题:三维NAND 集成工艺(3D-NAND Integration Technology)

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

3D NAND良率是NAND Flash市场最大变数

NAND型三维多层1TXR阻变存储器设计

Allwinner Technology Nand Flash Support List

2017年NAND产能成长有限、价格走扬

美光与英特尔合作伙伴关系将终止 因3D-NAND不符合目前市场

Sean Kang介绍未来几年3D-NAND的发展线路图,2021年堆叠层数会超过140层,而且会不断变薄

3D工艺的转型步伐较慢,NAND闪存依然处于供给吃紧的状态

半导体行业3D NAND Flash

三星、美光3D-NAND Flash产出比重已逾50%

未来的3D NAND将如何发展?

未来的3D NAND将如何发展?如何正确判断一款3D NAND的总体效率?

什么是3D NAND闪存?

3D-NAND 闪存探索将超过300层

3D-NAND浮栅晶体管的结构解析

详解三维NAND集成工艺(3D-NAND Integration Technology)

详解三维NAND集成工艺(3D-NAND Integration Technology)

评论