锁相环频率合成器ADF4106为速度和RF相位噪声性能树立了新的基准,完全适合在高达6.0 GHz的频率下工作。这样可以大大简化 5.4 GHz 至 5.8 GHz 上层 ISM 频段的设计。它采用先进的 0.35μm BiCMOS 工艺制造,取代了引脚和软件兼容的 4 GHz ADF4113,成为市面上最快的整数 N 分频频率合成器,并且开机时相位噪声可降低 3 dB!它只需要一个 3.3V 电源,但其 VP 引脚的额定电压高达 5.5 V,以便与基站中使用的模块化 VCO 通常需要的调谐电压电平兼容。

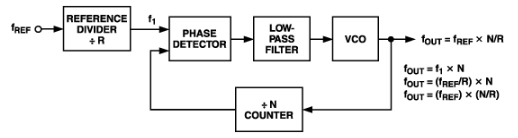

图1.ADF4106的功能框图

频率合成器ADF4106(图1)可用于在无线接收器和发射器的上变频和下变频部分实现本振(LO)。它由一个低噪声数字鉴频鉴频器(PFD)、一个精密电荷泵、一个可编程基准分频器、可编程A和B计数器以及一个双模预分频器(P/P+1)组成。A(6 位)和 B(13 位)计数器与双模预分频器 (P/P+1) 配合使用,实现 N 分频器 (N = BP+A)。此外,14位基准(R)计数器允许在PFD输入端选择REFIN频率。如果频率合成器与外部环路滤波器和压控振荡器 (VCO) 配合使用,则可以实现完整的锁相环 (PLL)。其非常高的带宽意味着在许多高频系统中可以省去倍频器,从而简化系统架构并降低成本。

宽带宽使其能够用作 6GHz 本地振荡器

图2.标准锁相环架构

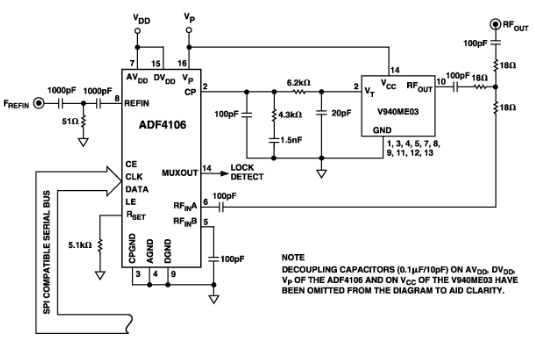

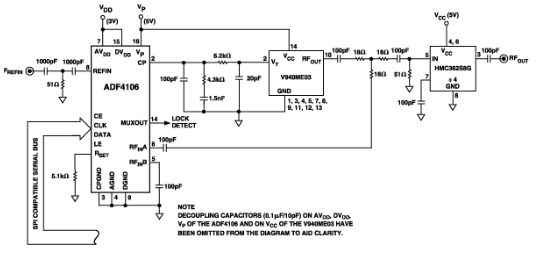

ADF4106及其前身ADF4113使用的标准PLL系统架构如图2所示。由于ADF4113的最大工作频率约为4 GHz,因此更高的频率需要使用倍频器,这通常需要额外的RF放大器才能为倍频器产生足够的电平。使用ADF4106省去了倍频器及其相关电路,实现了更简单、更节能的LO。例如,图3所示设计产生的RF输出频率为1 MHz通道间隔,频率范围为5.4 GHz至6.0 GHz。在上限测量的相位噪声为-83 dBc/Hz。

图3.ADF4106用于实现6.0 GHz本振。

由于ADF4106在这种高工作频率下的输入阻抗非常接近50 Ω,因此RF输入端不需要50欧姆端接电阻即可实现最大功率传输效率。在较低频率下工作时,数据手册中的s参数给出了匹配所需的阻抗值。

低相位噪声使其可用作低噪声、快速建立的 1.5GHz 本振

ADF4106与宽带宽分压器配合使用,可以改善标准本振电路在低于2.0 GHz频率时的相位噪声和锁定时间。

典型的无线系统可能以 200 kHz 的增量生成从 1450 MHz 到 1500 MHz 的频率。为此,使用整数 N 分频架构,需要 200 kHz 的相位/频率检波器参考频率,N 值将在 7250 (1450 MHz) 到 7500 (1500 MHz) 之间变化。

使用ADF4106获得最佳性能,相位噪声系数为–88 dBc/Hz。 此类系统中的典型基准杂散在88 kHz时为–200 dBc,在90 kHz时为–400 dBc。实现20 kHz环路带宽时,10度相位误差的典型锁定时间为250 μs。

图 4a.用于改善锁定时间、相位噪声和参考杂散的架构。

但是,ADF4106的宽带工作允许考虑另一种架构,如图4a所示。在这种配置中,内核PLL的工作频率是最终所需输出频率的倍数。在上面给出的示例中,最终所需的频率范围为1450 MHz至1500 MHz。器件频率范围内的倍数为 5800 MHz 至 6000 MHz(所需输出频段的 4 倍)。在图4a所示的方案中,FPFD的工作频率为800 kHz,FVCO频段为5800 MHz至6000 MHz,最终系统LO输出由FVCO除以4获得。

FOUT = (FPFD × N)/X (1)

下面概述了使用此体系结构的一些后果。

降相降噪

频率合成器的相位噪声为10对数F聚苯乙烯关系。这意味着PFD频率每增加一倍,频率合成器相位噪声就会下降3 dB。但是,VCO的输出将被分频,其相位噪声遵循20 logX规则。因此,X每增加一倍,相位噪声性能将增加6 dB。如果 PFD 频率翻了两番,如上所述,FVCO除以四,得到正确的F外.因此,由于F聚苯乙烯与使用标准架构相比,采用图12a时,相位噪声性能总增益为6 dB,因此采用图4a时,相位噪声性能总增益为94 dB。在上例中,产生的相位噪声为–<> dBc/Hz。

基准杂散减少

在整数N分频PLL中,杂散频率出现在VCO输出端PFD频率的整数倍处。在图 4a 中,如果您考虑FVCO,这些马刺将在F聚苯乙烯,2F聚苯乙烯,3F聚苯乙烯等。然而,在f外,基频除以X(X = 4),但杂散频率仍存在于PFD频率的整数倍处。但请注意,它们的振幅降低了 20 logX (20 log4 = 12 dB)。参见图 4b。

图 4b.比较 F 处的输出频谱VCO和 F外图4a。

因此,使用图 4a 中的架构(X = 4),并生成 1450 MHz 至 1500 MHz 的 FOUT,间距为 200 kHz,频率杂散将以 800 kHz(PFD 频率)的整数倍存在于低于 –90 dBc 的水平。请注意,虽然步进频率为200 kHz,但最低频率杂散为800 kHz。

锁定时间更短

由于图4a中的PFD以更高的频率工作,因此相位比较以更高的速率进行;这将导致循环锁定得更快。此外,由于PFD频率较高,因此可以获得更宽的环路带宽,这也有助于改善锁定时间。在本例中,对于70 kHz的PLL环路带宽,锁定时间约为10 μs,相位误差的80°以内。

图 4a 的实际实现如图 5 所示。

图5.使用带有输出分频器的ADF4106产生1.5 GHz本振。

总而言之,图5所示电路具有以下性能:

| 相位噪声 | –94 dBc/Hz @ 1kHz 偏移 | |

| 参考马刺 | <–100 dBc(系统本底噪声)@ 200kHz、400kHz、600kHz 偏移 | |

| –90 dBc @ 800-kHz 偏移 | ||

| 锁定时间 |

70 μs 至 10° 以内的相位误差 |

这种性能改进的代价是输出分压器的额外成本和整个系统的额外功耗(HMC通常会使ADF68的4106 mA电流要求增加13 mA)。因此,提高性能必须是使用此体系结构的关键要求。实现所需的额外电路板空间极少,因为 HMC 采用 8 引脚 SOIC 封装。

带宽

0.35 μm BiCMOS制造工艺和RF英国威廉希尔公司网站 的谨慎应用使ADF4106的预分频器部分能够在高达6.0 GHz的频率下工作,输入电平为–10 dBm(参考50 Ω),在–40至+85°C工业温度范围内得到保证。下图6显示了采用TSSOP封装的ADF4106在–40°C、+25°C和+85°C下的典型灵敏度曲线。 可以清楚地看到,6 GHz 的性能完全在信号低于 –15 dBm 的器件的范围内。

图6.ADF4106灵敏度与频率的关系

相位噪声

相位噪声是衡量本振信号纯度的指标,是无线电本振部分最关键的规格,直接影响接收器灵敏度。它是在给定载波偏移时,1 Hz带宽内噪声功率与输出载波功率的比率。以对数比表示,相位噪声的单位为dBc/Hz。 相位噪声通常使用频谱分析仪测量。

图7.基本锁相环模型。

图7所示电路将用作讨论相位噪声的电路模型。

锁相环中的总相位噪声(dB)可以表示如下:

PNTOTAL = PNSYNTH + 20 logN + 10 logFPFD (2)

哪里

PN总是PLL的总相位噪声

PN合成器相位噪声是由PLL频率合成器电路本身

引起的相位噪声20 log N是由于与反馈比相关的频率放大倍率引起的相位噪声增加,1/N。

10 日志F聚苯乙烯是与输入PFD频率相关的噪声增加。图8中的图表显示了ADF4106的相位噪声特性与PFD频率FPFD的函数关系。

图8.ADF4106相位噪声与PFD频率的关系

在给定测量的总噪声下,合成器噪声可以推断为:

PNSYNTH = PNTOTAL – 20 logN – 10 logFPFD (3)

这为PLL频率合成器电路本身提供了一个品质因数,而不管PLL N值和PFD频率贡献的噪声如何,因为对于要比较的任何类似电路,这些噪声都是相同的。对于ADF4106,该数字为–219 dBc/Hz,比ADF3提高了4113 dB,ADF<>是相位噪声方面最好的整数N分频频率合成器。

利用这种相位噪声品质因数,工程师可以计算出任何给定PFD频率和RF输出频率的总PLL相位噪声。例如,考虑生成频率为 1700 MHz 至 1800 MHz、通道间隔为 200 kHz 的本振信号。使用公式(2),使用ADF4106作为PLL频率合成器的近载波相位噪声为:

PNTOTAL = –219 + 20 log(9000) + 10 log(200 x 103)= (–219 + 79 + 53) dBc/Hz= –87 dBc/Hz

图8显示ADF4106遵守10个对数F聚苯乙烯“规则”(PFD相位噪声与对数频率基本成线性关系)一直相当一致,一直到30 MHz。一旦PFD频率超过1 MHz,一些整数N分频器件就会开始迅速退化。

请注意,–219 dBc/Hz品质因数是通过将图8外推回1 Hz而获得的。该图可用于在已知N值后快速识别给定PLL设置中可能的性能。例如,图表上的200 kHz对应于-166 dBc/Hz的相位噪声。 增加20 logN (79 dBc)得到-87 dBc/Hz的PLL相位噪声。

审核编辑:郭婷

-

频率合成器

+关注

关注

5文章

219浏览量

32350 -

pll

+关注

关注

6文章

776浏览量

135135 -

计数器

+关注

关注

32文章

2256浏览量

94480

发布评论请先 登录

相关推荐

设计带有新型宽带整数N分频PLL频率合成器的直接6GHz本振

设计带有新型宽带整数N分频PLL频率合成器的直接6GHz本振

评论