寄存器对于学习集成电路知识十分重要,不管是单片机亦或是现代计算机的CPU离开寄存器都无法快速的进行操作。

1、寄存器

寄存器是处理器中用来存储数据指令的电子元部件。例如在PC中数据由硬盘读取到内存,当CPU发起请求后数据由内存转储到CPU缓存中。

CPU缓存是SRAM,位于处理器内部,与ALU通过数据总线连接,物理距离S~S~是所有存储设备中最短的。

在前文中我们探究了内存的机理,内存由DRAM组成,每位DRAM由一个MOS管与电容构成,而电容充电充电时间常数的大小与电路的电阻有关,按照下式计算:

其中R是电阻;C是电容。

电路电阻和电容决定了DRAM响应速度有最大极限,SRAM由触发器组成,没有如电容、电感类的元器件,那么我们可以通过麦克斯韦电磁学方程对导体中电流速度进行定量描述。

电流在无损耗下,SRAM速度为真空中光速,考虑到电路中的阻抗,速度远小于C。并可得出以下公式:

其中 为电子在阻抗电路中移动速度;Z是阻抗;

为电子在阻抗电路中移动速度;Z是阻抗; 分别是SRAM速度、DRAM速度;S为与ALU距离。

分别是SRAM速度、DRAM速度;S为与ALU距离。

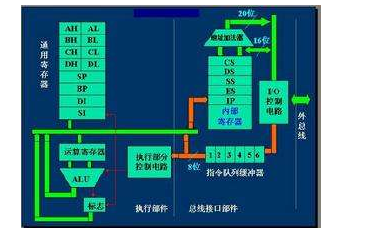

2、寄存器电路结构

寄存器由触发器与锁存器组成,触发器负责储存数据,锁存器负责保持数据。

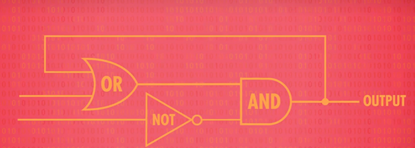

我们制造一个由或门构成的反馈电路,如图①。

0 OR 0 = 0;经反馈为0;

1 OR 0 = 1;& 1 OR 0 = 1;经反馈后为1;

1 OR 1 = 1;经反馈后为1;

在此电路中一旦输出为1不管如何改变A都无法改变输出。此电路正好可以用作记录1的电路。

同样的,如果我们用与门构建反馈电路。

1 AND 1 =1;经反馈后输出1。

0 AND 0 = 0;0 AND 1 = 0;1 AND 0 = 0;经反馈后都为0。

在此电路中一旦输出为0不管如何改变A都无法改变输出。此电路正好可以用作记录0的电路。

此时将两个电路以下图方式组合起来便称为:AND-OR锁存器。

它有两个输入,SET 将输出置1,RESET输出置0。

SET = 1;RESET = 1;OUTPUT = 0;

SET = 1;RESET = 0;OUTPUT = 1;

SET = 0;RESET = 1;OUTPUT = 0;

SET = 0;RESET = 0;OUTPUT = 之前数据,也就说电路将数据锁存起来了。

之所以叫“锁存”,是因为它“锁定”一个数据并保存状态。将数据放入叫:写入;数据输出叫:读取。

如果SET与RESET两根线不容易记忆,那么可以使用一些逻辑门构成数据输入与写入使能。

将相关电路封装起来,并使用线矩阵进行连接就可以支持多位数据位输入输出。

处理器中寄存器有很多,为了方便使用,我们一般将寄存器编号、命名。名字对应寄存器功能,寄存器编号对应寄存器地址。

3、寄存器惯常用法

我们本次汇编学习是基于80386进行的。

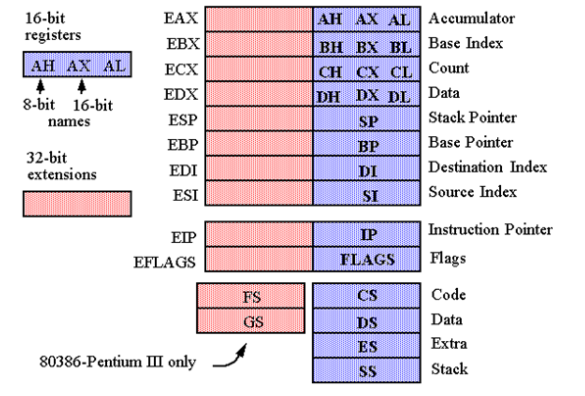

80386共提供7种类型的32位寄存器,如下:

通用寄存器(EAX、EBX、ECX、EDX、ESP、EBP、ESI、EDI)

段寄存器(CS、SS、DS、ES、FS、GS)

指令指针寄存器和标志寄存器(EIP、EFLAGS)

控制寄存器(CR0、CR1、CR2、CR3、CR4)

调试寄存器(DR0、DR1、DR2、DR3、DR4、DR5、DR6、DR7)

** 测试寄存器(TR6、TR7)**

一、通用寄存器

一组八个通用寄存器是对8086/80286通用寄存器的32位扩展,其用法与在8086/80286中相似,支持8位、16位、32位操作,进行32位操作是,寄存器名称前面冠以“E”。

这八个寄存器的名称如下:EAX(累加器)、EBX(基址)、ECX(计数)、EDX(数据)、ESP(栈指针)、EBP(基址指针)、ESI(源变址)、EDI(目的变址)。

二、段寄存器

80386比8086/80286增加了两个段寄存器FS、GS。

除CS支持代码段,SS支持堆栈段外,程序员可以利用其它的所有段寄存器支持数据段。

每个段寄存器对应这一个64位高速缓存器(有些资料中说有96位,但值使用其中的64位),这在8086中是没有的(在80286中为48位),它的具体作用将另文介绍。

三、指令指针寄存器和标志寄存器

指令寄存器EIP是对8086/80286指令指针寄存器的32位扩展,它包含着待执行指令的32位偏移量,该值总是相对CS所代表的段基址而言的。

**IOPL** (I/O Privilege Level)是从80286开始出现的,占2个bit表示I/O特权级,如果当前特权级小于或等于IOPL,则可以执行I/O操作,否则将出现一个保护性异常。IOPL只能由特权级为0的程序或任务来修改。

**NT** (Nested Task)也是从80286开始出现的,表示嵌套任务,用于控制中断返回指令IRET,当NT=0时,用堆栈中保存的值恢复EFLAGS、CS和EIP,从而实现返回;若NT=1,则通过任务切换实现中断返回。

下面的标志位是80386以后的CPU才有的标志。

**VM** (Virtual-8086 mode)表示虚拟8086模式,如果VM被置位且80386已出于保护模式下,则CPU切换到虚拟8086模式,此时,对段的任何操作又回到了实模式,如同在8086下运行一样。

RF(Resume flag)表示恢复标志(也叫重启标志),与调试寄存器一起用于断点和单步操作,当RF=1 时,下一条指令的任何调试故障将被忽略,不产生异常中断。当RF=0时,调试故障被接受,并产生异常中断。用于调试失败后,强迫程序恢复执行,在成功执行每条指令后,RF自动复位。

**AC** (Alignment check)表示对齐检查。这个标志是80486以后的CPU才有的。当AC=1且CR0中的AM=1时,允许存储器进行地址对齐检查,若发现地址未对齐,将产生异常中断。所谓地址对齐,是指当访问一个字(2字节长)时,其地址必须是偶数(2的倍数),当访问双字(4字节长)时,其地址必须是4的倍数。

但是只有运行在特权级3的程序才执行地址对齐检查,特权级0、1、2忽略该标志。

**VIF** (Virtual interrupt flag)表示虚拟中断标志。以下的三个标志是Pentium以后的CPU才有的。当VIF=1时,可以使用虚拟中断,当VIF=0时不能使用虚拟中断。该标志要和下面的VIP和CR4中的VME配合使用。

**VIP** (Virtual interrupt pending flag)表示虚拟中断挂起标志。当VIP=1时,VIF有效,VIP=0时VIF无效。

**ID** (Identification flag)表示鉴别标志。该标志用来只是Pentium CPU是否支持CPUID的指令。

实际上,如果不编写操作系统,大部分标志可能很难得用到一次,有个印象就好了,用到了再去查不迟。

四、系统表寄存器

80386 中有4个系统表寄存器,分别是全局描述符表寄存器(GDTR)、中断描述符表寄存器(IDTR)、局部描述符表寄存器(LDTR)、任务状态寄存器(TR)。系统表寄存器用于在保护方式下,管理4 个系统表,由于只能在保护方式下使用,因此又称为保护方式寄存器。有关描述附表的问题,另文介绍。

五、控制寄存器

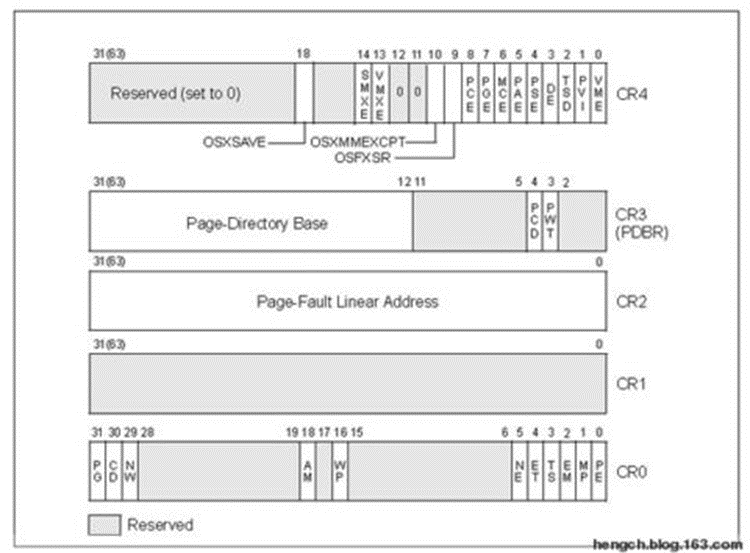

80386的控制寄存器有4个,其中CR1保留以后使用,从Pentium开始,又增加了一个CR4,CR0的低16位包含了与80286的MSW一致的位定义,保持了和80286的兼容,同时也兼容了从80286开始的两条指令LMSW/SMSW,其基本定义如下:

CR0中各位含义如下:

·PE (Protection Enable)保护模式允许,PE=0表示CPU工作在实模式,PE=1表示CPU工作在保护模式

·MP (Monitor Coprocessor)监控协处理器,MP=1表示协处理器在工作,MP=0表示协处理器未工作。

·EM (Emulation)协处理器仿真,当MP=0,EM=1时,表示正在使用软件仿真协处理器工作。

·TS (Task Switched)任务转换,每当进行任务转换时,TS=1,任务转换完毕,TS=0。TS=1时不允许协处理器工作。

以上4个定义从80286开始,下面的2个定义从80386开始存在

·ET (Extension Type)处理器扩展类型,反映了所扩展的协处理器的类型,ET=0为80287,ET=1为80387。

·PG (Paging)页式管理机制使能,PG=1时页式管理机制工作,否则不工作。

从80486开始又增加了如下位定义。

·NE (Numeric Error)数值异常中断控制,NE=1时,如果运行协处理器指令发生故障,则用异常中断处理,NE=0时,则用外部中断处理。

·WP (Write Protect)写保护,当WP=1时,对只读页面进行写操作会产生页故障。

·AM(Alignment Mask)对齐标志,AM=1时,允许对齐检查,AM=0时不允许,关于对齐,在EFLAGS的AC标志时介绍过,在80486以后的CPU中,CPU进行对齐检查需要满足三个条件,AC=1、AM=1并且当前特权级为3。

·NW (Not Write-through)和CD(Cache Disable),这两个标志都是用来控制CPU内部的CACHE的,当NW=0且CD=0时,CACHE使能,其它的组合说起来比较复杂,如果有读者真的想搞清楚的话,可以参阅《Intel? 64 and IA-32 Architectures》中的“Software Developer’s Manual Volume 3A”这一册,在第10章对这两个标志的各种组合有比较详细的说明。

CR1保留未用;CR2存放引起页故障的线性地址,只有在PG=1时,CR2才有效,当页故障处理程序被激活时,压入页故障处理程序堆栈中的错误码提供页故障的状态信息。

CR3的bit12--bit31存放页目录的基地址,因为也目录总是页对齐的(一页为4K),所以页目录基地址从bit12开始就可以了。只有当CR0中的PG=1时,CR3的页目录基地址才有效。

从80486开始,在CR3的低12位定义了两个控制位,如下:

·PCD (Page-level Cache Disable)页CACHE禁止,当PCD=0时,页目录表进行高速缓存,PCD=1时,不进行高速缓存;该位控制PCD引脚控制外部CACHE工作还是不工作。

·PWT (Page-level Writes Transparent),CACHE的写入分为透写(Write-Through)和回写(Write-Back),80486以上的CPU内部的CACHE都是透写的,但对外部CACHE而言,允许某些页是回写的,而另一些页是透写的,当PWT=1时,外部CACHE对页目录进行透写,否则进行回写;此位驱动PWT引脚以控制外部CACHE是透写还是回写。

CR4是从Pentium CPU开始出现的。

·VME (Virtual-8086 Mode Extensions)虚拟8086方式扩展,VME=1允许使用虚拟8086扩展模式,否则只能使用80386/80486的虚拟8086模式。

·PVI (Protected-Mode Virtual Interrupts)保护模式虚拟中断,PVI=1时,在保护模式下支持虚拟中断标志VIF(EFLAGS中),PVI=0则不支持虚拟中断标志。

·TSD (Time Stamp Disable)时间戳禁止,TSD=1时,允许在特权级为0的程序中执行RDTSC指令(读时间戳计数指令),TSD=0时,允许任何特权级执行RDTSC指令。

·DE (Debugging Extensions)调试扩展,

·PSE (Page Size Extensions)页大小扩展,PSE=1时,页大小可以扩展到2M或4M,PSE=0时,页大小只能是4K.

·PAE (Physical Address Extension)物理地址扩展,PAE=1时,页物理地址可以扩展到36bits以上,PAE=0时只能用32bits的物理地址。

·MCE (Machine-Check Enable)硬件检查使能,Pentium以后的CPU有一种硬件检测功能,MCE=1时允许使用该功能。

·PGE (Page Global Enable)全局页使能,PGE=1时,允许使用全局页,PGE=0时禁止使用全局页。

·PCE (Performance-Monitoring Counter Enable)性能监视计数器使能,当PCE=1时,允许在任何保护级下执行RDPMC指令,PCE=0时,只有特权级0的程序可以执行RDPMC指令。

·OSFXSR (Operating System Support for FXSAVE and FXRSTOR instructions)

·OSXMMEXCPT (Operating System Support for Unmasked SIMD Floating-Point Exceptions)

·VMXE (VMX-Enable Bit)VMX使能位,VMXE=1时,允许VMX操作。

·SMXE (SMX-Enable Bit)SMX使能位,SMXE=1时,允许SMX操作。

·OSXSAVE (XSAVE and Processor Extended States-Enable Bit)

六、调试寄存器

一共有8个调试寄存器DR0--DR7,DR0-DR3可以分别设置4个断点的线性地址,DR4-DR5保留未用,DR6是断点状态寄存器,DR7是断点控制寄存器(包括断点类型、断点长度,断点开放/禁止)

七、测试寄存器

一共有8个测试寄存器TR0--TR7,TR0-TR2保留,TR3-TR5用作CACHE测试,TR6为命令测试寄存器,TR7为测试数据寄存器。

参考文献:

1、 INTEL 80386 PROGRAMMER'S REFERENCE MANUAL 1986 (mit.edu)

2、 https://www.cnblogs.com/darknife/p/3159059.html

-

集成电路

+关注

关注

5388文章

11545浏览量

361789 -

寄存器

+关注

关注

31文章

5343浏览量

120332 -

cpu

+关注

关注

68文章

10862浏览量

211730

发布评论请先 登录

相关推荐

定时器A各寄存器的用法以及功能

ADC0809用法详解_引脚图及功能_工作原理_内部结构及应用电路

Java数组的常用方法_Java:数组工具类Arrays类的常用方法的用法及代码

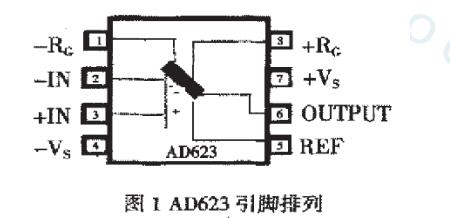

ad623典型电路用法介绍_ad623结构与工作原理

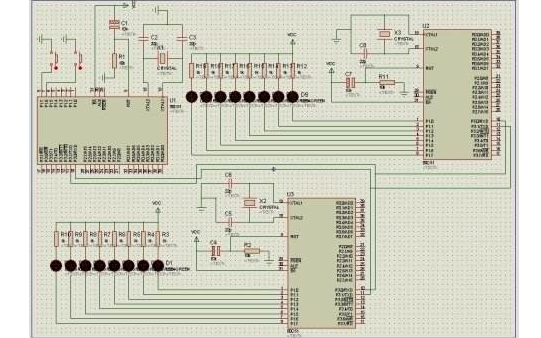

51单片机的原理,指令,寄存器,以及接口

探究寄存机的电路结构以及惯常用法

探究寄存机的电路结构以及惯常用法

评论