作者:Doug Mercer and Joe DiPilato

引脚兼容的AD976x系列8位、10位、12位和14位TxDAC™低失真DAC以高达125 MSPS的时钟速率提供出色的无杂散动态范围(SFDR)规格,具有CMOS器件典型的低价格和功耗水平。

面向消费者的无线和有线通信市场的迅速扩张催生了对高速模数和数模转换器的永不满足的需求,这些转换器具有良好的动态(频域)性能,成本低,功耗低。最明显的表现是为满足接收路径的需求而开发的新型CMOS ADC产品的盛宴;但是,目前缺乏适合许多发射信号路径应用的具有动态性能的低成本CMOS DAC产品。

传统的时域和直流线性度特性,如积分非线性(INL)、差分非线性(DNL)、毛刺脉冲和建立时间,都不足以反映频域中的响应和失真。大多数现有的高速CMOS DAC主要用于视频应用,其无杂散动态范围(SFDR)和谐波失真(THD)往往较差。双极性和BiCMOS器件可以提供所需的动态性能,但它们通常成本太高,需要双电源,并且功耗过高,不适合未来的大容量通信应用。

低功耗需求是由通信平台的变化驱动的。它们要么在物理上变得越来越小,需要更高的组件封装密度(例如,微型和微型基站封装在悬挂在电线杆和建筑物侧面的小盒子中);或便携式和电池供电(例如,电话、寻呼机、抄表终端等);或由电话线供电(无线本地环路);或需要备用电池(电缆电话、生命线服务)。这些要求都要求低功耗以延长电池寿命,最大限度地减少散热,并在有限的可用功率下运行。在这方面,单电源组件避免了额外电源的成本和低效率。3V 单电源器件正变得非常流行,以实现更低的功耗并与高密度数字电路兼容。

这些对低成本、低功耗和良好动态性能的要求导致了用于发射应用的新型高速CMOS DAC的开发。这种新型低成本TxDAC™系列的额定更新速率高达125 MHz,是高速发送路径CMOS DAC的重大突破。它们提供的SFDR性能是迄今为止高速CMOS DAC无法实现的。

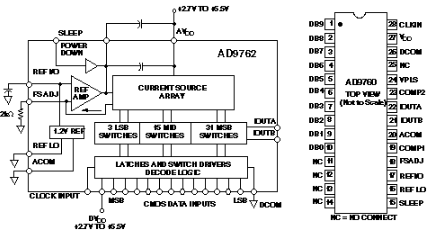

TxDAC系列的前五款产品包括8位、50 MSPS AD9708AR;10位、50 MSPS AD9760AR-50;10位、125 MSPS AD9760AR;12位、125 MSPS AD9762AR;以及14位、125MSPS AD9764AR。所有五种型号均采用引脚兼容的28引脚SOIC封装,使设计人员能够在设计周期的评估阶段轻松权衡性价比。图1显示了12位AD9762的功能框图和10位AD9760的引脚排列。无论分辨率如何,MSB (DB N1) 在该系列中始终是引脚 1;低分辨率设备可以直接连接到为高分辨率设备布线的电路。这允许统一的设计尺寸和直接交换不同分辨率的模型,以便进行比较、升级和降低定价。

图1.AD9762框图和AD9760引脚排列。

这些器件采用低成本亚微米单多晶硅双金属CMOS工艺制造。每个DAC的interwetten与威廉的赔率体系 和数字电路均可采用+2.7 V至+5.5 V单电源供电(提供全3 V单电源供电)。每个DAC包括一个温度补偿型1.2 V带隙基准电压源,提供高达20 mA满量程(顺从电压= 1.25 V)的差分电流输出,由片内基准电压放大器调节,可使用外部电阻在2 mA至20 mA范围内进行设置。DAC输出在35 ns内稳定至最终值的0.25%以内。满量程10%至90%的上升和下降时间规定为2.5 ns,输出传播延迟仅为1 ns。

设计特点

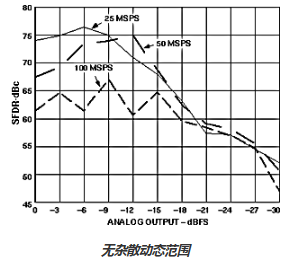

为了消除与传统R-2R梯形架构相关的幅度相关失真,并实现卓越的交流和直流性能,TxDAC采用了分段电流源。例如,12位AD9762的核心是49个电流源(图1)。5 个最高有效位对输出的贡献由最多 31 个相等的电流源相加而成,每个电流源的权重为 25司 司长。接下来四位的贡献是通过将最多 15 个电流源相加,其权重是第一组的 1/16(即 29FS 每个)。3 LSB 由或多或少的传统 3 位二进制 DAC 开关电流组成,其权重为第二组的 1/2、1/4 和 1/8。这种分段架构是AD9762实现±0.5 LSB 12位DNL性能和5 pV-s低输出毛刺脉冲规格以及多音应用中出色SFDR的关键,在这些应用中,DAC的输出通常以1/2或1/4满量程工作。图2显示了AD9762在不同速率下的单音SFDR与输出电平的关系。

对于通信应用的传输路径,分段电流源架构本身不足以实现所需的SFDR。为了减少交流失真的固有原因,尤其是谐波,我们集中精力在改进输出开关时序上。由此产生的创新专有锁存器和开关电路使SFDR比传统的CMOS“视频”DAC产品提高了约20 dB。此外,TxDAC 系列的 SFDR 性能可与最好的双极性和 BiCMOS IC 器件相媲美,但功耗和价格仅为其一小部分。

无杂散动态范围图2.SFDR与不同采样率下的输出幅度的关系。

为什么SFDR在通信中很重要?通常,传输的信息与其他通信信道和应用程序共享频谱/带宽(例如,通过公共电缆广播或传输的不同电视频道,蜂窝系统中的不同呼叫者,不同的FM广播电台等)。如果发射器将杂散信号发送到其他频段,它们可能会损坏、中断或消除相邻信号。这被认为是不好的做法,违反了FCC(和其他监管机构)的规定,并可能导致法律诉讼。

TxDAC系列在奈奎斯特频段的SFDR从时钟频率为100 MSPS并产生40 MHz输出信号时的57 dB(10位AD9760)到78 dB(时钟频率为20 MSPS,产生2 MHz输出)(14位AD9764)。表1显示了AD9760、AD9762和AD9764在不同时钟速率和输出频率下的典型SFDR和THD规格。虽然 12 位和 14 位器件为满量程正弦波提供类似的 SFDR,但更高分辨率器件对于具有高峰均比和大量低电平内容的信号具有更好的 SFDR。图3显示了12位AD9762奈奎斯特范围内的典型频谱图,输出由时钟速率为100 MSPS的单个20 MHz信号组成;图中为60.8 dB的二次谐波,其余杂散为<75 dB。在大多数窄带应用中,谐波被滤除,“一个窗口”或“无谐波”内的SFDR才是最重要的。在这种情况下,TxDAC系列提供80 dB范围内的性能,即使对于10位AD9760,时钟频率为100 MSPS的5 MHz范围内的输出也是如此。

在宽带应用中,DAC将在其输出端产生多个信号,双音或多音性能尤其令人感兴趣。突出的应用是通过电缆同时发送两个或多个数据/语音/视频通道。宽带蜂窝基站是另一个,除此之外,还有ADSL(非对称数字用户线)等应用,它利用基于多音调的离散调制方案,并依赖于良好的多音性能。

| 表 1.典型的 SFDR 和 THD 规格 | |||

| SFDR | AD9760 | AD9762 | AD9764 |

|

FC=50兆赫;F外=5.05 MHz 至奈奎斯特 |

67分贝 |

70分贝 |

70分贝 |

|

FC=50兆赫;F外=20.2 MHz 至奈奎斯特 |

642分贝 |

67分贝 |

67分贝 |

|

FC=100兆赫;F外=5.05 MHz 至奈奎斯特 |

61分贝 |

64分贝 |

64分贝 |

| FC=100兆赫;F外=40.4 MHz 至奈奎斯特 | 57分贝 | 60分贝 |

60分贝 |

| FC=50兆赫;F外=5.05兆赫;2 兆赫跨度 | 84分贝 | 84分贝 | 84分贝 |

| FC=100兆赫;F外=5.05兆赫;2 兆赫跨度 | 84分贝 | 84分贝 | 84分贝 |

| 谐波失真 | |||

| FC=50兆赫;F外=5.05兆赫 |

-61 分贝 |

-64 分贝 |

-64 分贝 |

| FC=100兆赫;F外=5.05 |

-57 分贝 |

-60 分贝 |

-60 分贝 |

图3.以 100 MSPS 采样的 19.96MHz 正弦波;差分输出,50(欧姆),20 pf,SFDR = 60.8 dB。

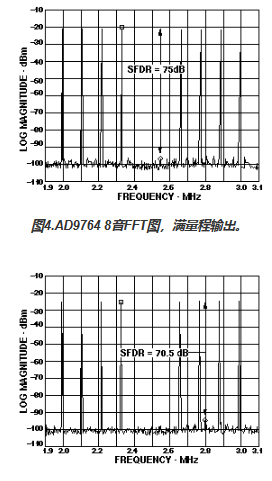

在大多数多音应用中,发射路径DAC的输出通常在满量程范围的一小部分(例如,1/2或1/4 FS)下工作,以确保DAC输出不会与接近满量程的所有通道削波(削波发射波形产生的谐波可能导致非法“飞溅”)。图4和图5分别显示了AD9764满量程和半量程8音波形的频谱图;两者都表示SFDR>70 dBc,这是创新转换器架构的重要结果。TxDAC系列的各种型号已经针对在单音测试中表现相当的BiCMOS DAC进行了测量;TxDAC在多音应用中实现了可重复的更好性能。这可能与广泛使用的R-2R梯形网络架构引起的时序偏差有关,TxDAC专有的电流开关架构已经过优化以最小化。

图5.AD9764 8音FFT图,1/2电平输出。

TxDAC 内核中使用的开关电路提供真正的差分输出,从而在差分使用器件时提高性能。尽管TxDAC系列的单端性能本身非常出色,但当输出通过变压器差分驱动时,可以实现最佳的谐波性能。表2显示了12位AD9762的差分性能比单端性能的改善,特别是在较高频率下。

| 表 2.AD9762 无杂散动态范围,fs = 125 MSPS | ||

| 单音 | 单端 | 微分 |

|

1兆赫 |

70分贝 |

72分贝 |

|

5兆赫 |

63分贝 |

70分贝 |

|

10兆赫 |

58分贝 |

65分贝 |

| 39兆赫 | 46分贝 | 54分贝 |

每个DAC采用+5 V单电源供电,时钟频率为100 MSPS,功耗为150 mW,配置为20 mA满量程电流输出。时钟频率为40 MSPS,采用+3 V单电源供电,配置为2 mA满量程输出,功耗降至极低的35 mW。每个器件都支持睡眠模式,当DAC不工作时,功耗从+5 V降至<30 mW。

在许多情况下,数字通信系统的品质因数是其误码率(BER)。误码率通常由适当的标准/规范决定,并受模拟元件性能、传输介质、调制方案、数据速率以及可用的均衡和纠错电路的组合影响。各种不同的无线和有线应用(包括用于蜂窝、PCS、寻呼机、无线本地环路和卫星服务的无线基站和终端,以及用于互联网接入的有线调制解调器、交互式视频机顶盒和数字用户线路,如 ADSL、HDSL、VDSL 等)使用许多不同的调制方案,适应不同的数据速率,并需要不同的系统级性能。

在这些情况下,由于与DAC性能缺乏独特的关系,通信系统设计人员很难确定转换器所需的分辨率/动态范围。幸运的是,TxDAC的引脚兼容尺寸允许在开发周期的任何阶段进行性价比权衡,并为未来更高性能的系统提供了升级途径。系统设计人员可以灵活地在误码率性能与系统成本之间进行权衡。该选择允许设计人员适应一定的误差范围,补偿均衡和纠错方法和性能。此外,由于给定调制方案的数据速率与带宽和动态范围成正比,因此设计人员可以在高端器件上提供更高的数据速率。

两种基本的发射架构如图6和图7所示。在基于正交的调制方案中,例如QPSK和QAM,部署混频器以将同相(I)和正交(Q-90度异相)信号混合成复合单边带信号以进行传输。图6所示为基带发射架构,该架构可模拟I和Q信号混合。在本例中,每个发射通道需要两个DAC。即使在许多基带应用中使用的低输出频率下,TxDAC系列也是最佳选择,因为该系列的所有成员在低输出频率下都结合了(1)高SFDR;(2)低功耗,单电源和3V操作,提高系统电源效率;(3)有竞争力的价格(通过对信号进行过采样(插值)来减少DAC的带内混叠镜像,从而减轻低通滤波器的工作,从而进一步降低总成本);(4) 同一引脚布局中提供的各种分辨率允许最终的成本/性能权衡。例如,在许多 TxDAC 测试版站点应用程序中,用户从一个分辨率模型开始,然后根据实际系统性能设计更高或更低分辨率的设备。

图6.具有模拟正交混频的基带发射架构。

图7中的系统架构使用I和Q信号的数字混频,并将调制信号直接输入到单个DAC。在这种情况下,DAC的带宽要求更加严格。通过数字调制,可以通过TxDAC芯片产生40 MHz范围内的中频(IF)。这足以直接传输高速调制解调器中的数据和交互式机顶盒中的上游信息。在其他应用中,它可以消除上变频器级。在这里,高SFDR、低价格、低功耗和系列引脚兼容性也是理想的(必需)属性。如果将多个数字I&Q调制器馈入图7所示的单个DAC,则系统将对应于宽带发射架构,为此,TxDAC系列产品的卓越多音性能是一个主要的性能属性。

10位AD9760正在进入高速互联网数据调制解调器和交互式机顶盒,其中SFDR要求在50 dB范围内,输出频率为40 MHz,时钟速率高达120 MSPS。它们还用于无线本地环路和高速无线集群基站。这些 12 位器件被设计用于蜂窝和个人通信服务 (PCS) 基站、电缆头端设备和混合光纤同轴调制解调器,在这些器件中,在不同的时钟和采样速率下需要高达 70 dB 的 SFDR。14位AD9764正在ADSL调制解调器和下一代PCS基站中找到一>,在这些基站中,1 MHz至6 MHz信号需要70 dB<时钟速率为15 MSPS。

图7.具有数字调制的传输架构。

用于普通CMOS制造的芯片设计的一个主要优势是数字集成兼容性。TxDAC内核基于CMOS工艺进行了优化,可实现与数字信号处理(DSP)电路的高效集成,从而进一步节省电路板和成本,并增强性能和可靠性。通过将数字处理与DAC内核集成,可以实现比以往任何时候都更高速的数字切换。

例如,在使用数字DDS引擎和高性能(双极性)DAC的传统双芯片直接数字合成(DDS)系统中,速度和分辨率受到将数字数据从DDS芯片时钟传输到DAC所需的速度和功率的限制(TTL逻辑限制为约100 MSPS)。通过将DDS电路与DAC集成,内部数据速率将>200 MSPS可用且经济。除了单芯片高性能DDS(见第12页)外,未来的片上数字电路还将包括数字调制器和插值滤波器。

审核编辑:郭婷

-

电源

+关注

关注

184文章

17706浏览量

250002 -

转换器

+关注

关注

27文章

8696浏览量

147105 -

变频器

+关注

关注

251文章

6549浏览量

144547

发布评论请先 登录

相关推荐

FPGA通过SPI对DAC进行了配置,用频谱仪测不到输出是怎么回事?

HV857已针对各种应用进行了优化

AD9637-80EBZ,在小封装尺寸至关重要的应用中针对出色的动态性能和低功耗进行了优化

采用AD9114双路低功耗8位TxDAC的AD9114-EBZ评估板

DC2103A演示电路针对低启动电压进行了优化,采用100:1匝数比变压器

MIKROE-2815,基于MAX31865电阻数字转换器,针对铂电阻温度检测器或RTD进行了优化

AD9481-PCB,AD9481评估板是一款8位,单芯片模数转换器(ADC),针对高速和低功耗进行了优化

对结构体成员进行了赋值

RS通信编码器怎么进行优化设计?

STM32CubeIDE是否针对新MAC中的Apple M1芯片进行了优化?

TxDAC系列高速DAC的引脚兼容性

DAC针对通信传输路径进行了优化

DAC针对通信传输路径进行了优化

评论