作者:Steven Xie, Karl Wei, and Claire Croke

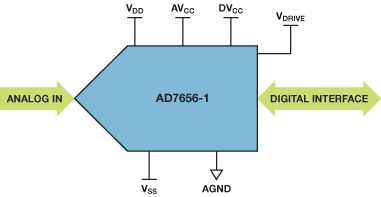

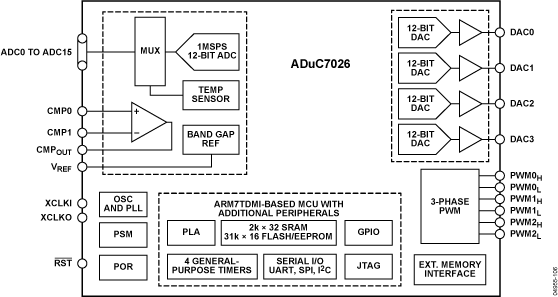

高压开关、双极性ADC和其他具有多个电源的器件通常需要按特定顺序施加或移除电源电压。本文提出了一种简单、经济高效的方法,用于确定系统在受到电源瞬变、中断或序列变化时的行为。采用多个电源的器件示例是AD7656-1(表1),这是一款16位、250 kSPS、6通道、同步采样、双极性输入ADC。ADuC7026精密模拟微控制器的四个12位DAC提供DUT的可编程电源电压。使用AD7656-1评估板和ADuC7026评估板,只需进行最少的硬件和软件开发即可完成原型设计。

表 1.AD7656-1 典型电源电压和最大电源电流

| Supply | AVCC, DVCC | VDRIVE | VDD | VSS |

| 电压 | 5 |

3.3 |

10 | –10 |

| 电流(毫安) | 30 | 10 | 0.25 | 0.25 |

表1显示了每个ADC电源的典型电压和最大电流。ADuC7026上的四个DAC产生的可编程时序可控电压波形由AD7656-1评估板上的超低噪声和失真运算放大器AD797进行缩放,以提供指定的电源电压和电流。微控制器的速度和可编程性有助于控制电源电压的电压电平、周期、脉冲宽度和斜坡时间。

例如,使用外部电源,AD7656-1评估板上的AD797放大器(配置为增益为5)可以产生0 V至12.5 V的电压范围,以驱动ADC的VDD供应轨。AD797的高输出驱动能力允许为每个电源轨提供高达50 mA的电流。图1显示了与ADC的连接。

图1.AD7656-1 连接图

ADuC7026 DAC数据寄存器可通过41.78 MHz内核时钟以7 MHz频率更新,从而最大限度地提高电压更新速率。以下部分介绍开发过程,并提供使用评估板获得的测量结果。

硬件开发和设置

ADuC7026评估板上的四个DAC输出引脚和AGND分别连接到AD7656-1评估板上的四个AD797输入和AGND。安捷伦 E3631A 外部电源模块为 AD797 提供 ±15 V。通过USB连接到ADuC7026评估板的计算机提供5 V电源和串行通信。

原理图设计

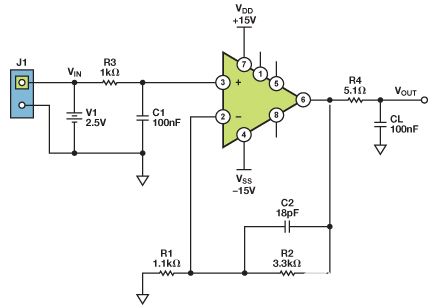

AD7656-1评估板上唯一需要的硬件更改与AD797有关。可以根据不同的增益和带宽要求选择R1和R2。图3显示AD797设置为增益= 4,以便从ADuC7026 DAC的0 V至2.5 V输出提供0 V至10 V输出。R3和C1形成一个低通滤波器,以降低高频噪声。CL用作电源轨上的负载电容器。

图3.AD797原理图设计,增益=4。

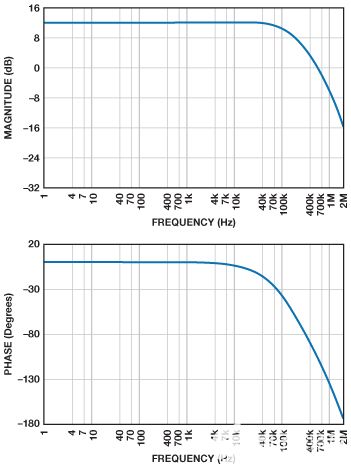

图4显示了AD797在增益= 4时的频率响应,从NI 多 SIM 卡™interwetten与威廉的赔率体系 。1.0MHz 带宽和 73° 相位裕量可提供快速瞬态响应和稳定运行。

图4.AD797的频率响应,增益=4。

AD797 设计笔记

超低失真、超低噪声运算放大器AD797具有80 μV最大失调电压、出色的直流精度、800 ns建立至16位、50 mA输出电流和±13 V输出摆幅(采用±15 V电源供电),非常适合驱动电源轨。

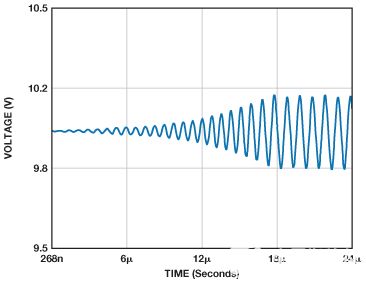

不过,它不会针对大量容性负载进行内部补偿,因此必须使用外部补偿威廉希尔官方网站 来优化此应用。图5显示了驱动容性负载引起的AD797输出振荡。

图5.无补偿振荡。

为了在电源轨上具有容性负载的情况下稳定驱动,电阻R4放置在输出和负载之间。该电阻将运算放大器输出和反馈网络与容性负载隔离开来,并在反馈网络的传递函数中引入零点,从而降低更高频率下的相移。1反馈电容C2补偿运算放大器输入端的容性负载,包括C1。

应用DAC

ADuC7026精密模拟微控制器具有四个12位电压输出DAC,具有轨到轨输出缓冲器、三个可选范围和10 μs建立时间。

每个DAC具有三个可选范围:0 V至VREF(内部带隙2.5 V基准电压源),0 V至DACREF(0 V至AVDD),和 0 V 至 AVDD.范围使用控制寄存器 DACxCON 设置。DAC接受0 V至AV范围的外部基准电压源DD.使用内部基准电压源时,必须从VREF引脚连接到AGND,以确保稳定性。

四个DAC中的每一个都可以通过控制寄存器DACxCON和数据寄存器DACxDAT独立配置。一旦通过DACxCON寄存器配置了DAC,就可以将数据写入DACxDAT以获得所需的输出电压电平。

四个DAC输出很容易使用C或汇编语言进行控制。此C代码示例展示了如何选择内部2.5 V基准电压源并将DAC0输出设置为2.5 V。

将内部 2.5 V 基准连接到 VREF 引脚

REFCON = 0x01;

//enable DAC0 operation

DAC0CON = 0x12;

//update DAC0DAT register with data 0xFFF

DAC0DAT = 0x0FFF0000;

Using assembly language,

DAC0CON[5] 被清除以使用内核时钟 (41.78 MHz) 更新 DAC0 以实现快速更新速率;

DAC0CON[1:0] 设置为“10”以使用 0 V 至 VREF (2.5 V) 输出范围

“DAC0DAT = 0x0FFF0000”可以通过两个指令编译为汇编代码:

MOV R0, #0x0FFF0000

STR R0, [R1, #0x0604]

这两个指令总共需要六个时钟周期来执行,对应于 7 MHz 更新速率和 41.78 MHz 内核时钟频率。因此,电压轨之间的时间延迟可以精确到144 ns。

测量结果

ADuC7026中的四个DAC为AD7656-1提供四个电源,以测试其在电源瞬变或时序变化下的行为。表2显示了ADC的电源和电压电平。

表 2.AD7656-1电源

| 数字转换器通道 |

DAC0 |

数字转换器1 |

DAC2 |

DAC3 |

| 输出范围 | 0 V 至 1.250 V | 0 V 至 0.825 V | 0 V 至 2.500 V | 0 V 至 2.500 V |

| AD797 增益 | 4 | 4 | 5 |

–5 |

| AD797 输出摆幅 | 0 V 至 5.00 V | 0 V 至 3.30 V | 5.00 V 至 12.50 V |

–12.50 V 至 –5.00 V |

| 标称电压 | 5.00 伏 | 3.30 伏 | 10.00 伏 | –10.00V |

| AD7656-1 电源 | AVCC, DVCC | VDRIVE | VDD | VSS |

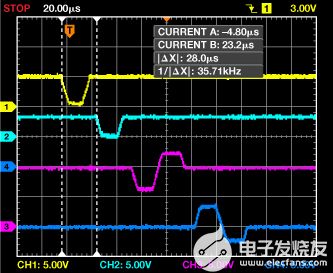

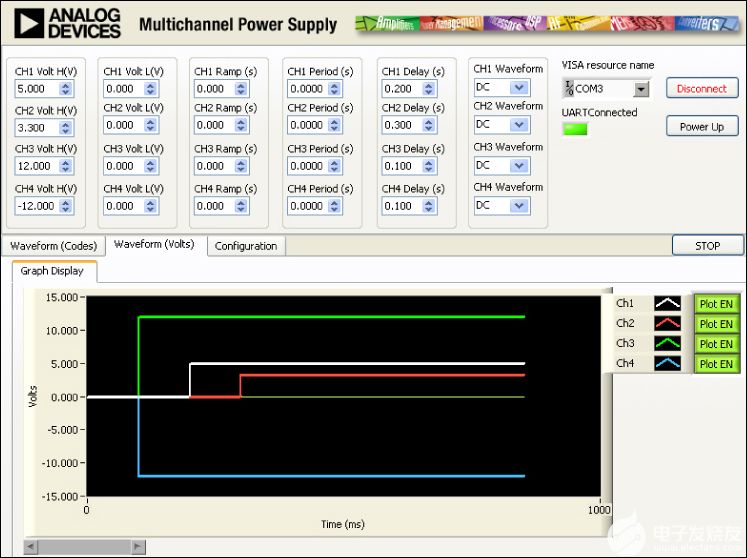

如表2所述,来自四个DAC输出的波形是使用示波器捕获的,如图6所示。每个通道的电压电平、周期、脉冲宽度和斜坡时间都是可编程的,易于控制。具体参数在以下各节中测量和描述。

图6.四通道电压波形。

为了达到每个电源的精确电压电平,图3中的R1可以使用可调电阻。通过使用安捷伦 34401A 数字万用表调节 R1 来校准电压电平。

测量上升和下降斜坡时间以确定电压波形的最大频率。斜坡时间与电阻R4的值和容性负载CL有关。对于较慢的斜坡时间,R4和CL可以使用较大的电阻和电容值。AV的上升和下降斜坡时间抄送和DV抄送用不同的负载电容进行测试,结果如表3所示。使用1 μF电容时的上升波形如图7所示。斜坡时间在10 V的10%至90%之间测量。

表 3.容性负载时的斜坡时间

| 容性负载 | 10 nF (V/μs) | 0.1 μF (V/μs) | 1 μF (伏/微秒) | 10 μF (V/μs) |

| 上升边缘 | 6.90 | 0.97 | 0.07 | 0.01 |

| 落沿 | 5.71 | 0.93 | 0.06 | 0.01 |

图7.1μF 容性负载下的上升时间。

电源纹波

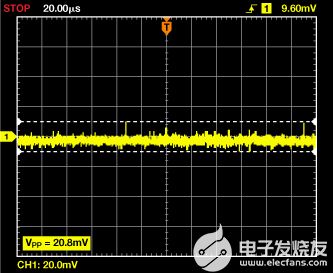

AD797具有出色的直流精度,可通过调节反馈电阻R1轻松为AD7656-1提供精确的标称电压电平。电源的峰峰值纹波是在标称电压电平下测量的,标称电压水平为200 MHz和20 MHz带宽,容性负载为0.1 μF,采用DS1204B示波器。表4显示纹波小于标称电压的1%,因此四个电源均符合要求。

表 4.每个电源的纹波

| Power Supply | AVCC, DVCC (5.00 V) | VDRIVE (3.30 V) | VDD (10.00 V) | VSS (–10.00 V) |

| 200 MHz (mV) | 20.8 | 28.0 | 25.6 | 30.4 |

| 20 MHz (mV) | 12.8 | 24.8 | 15.2 | 18.4 |

图8.AVCC 和 DVCC 上的 5V 电源纹波。

生成波形

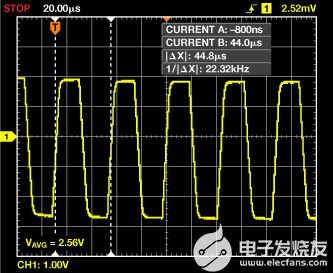

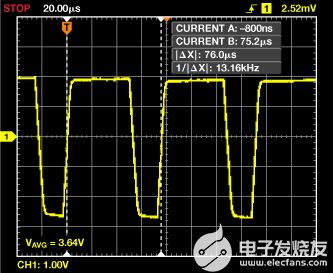

只需对ADuC7026源代码进行简单修改,就可以为需要评估不同电源条件下器件工作情况的各种不同应用生成许多不同的电压波形序列。可以生成的典型波形如图9和图10所示。

图9.22.32 kHz 方波。

图 10.13.16 kHz 脉冲波形。

图 11 中 显示 的 LabVIEW GUI 可用于 生成 电源 波形。四个通道的电压电平、斜坡时间、周期和序列延迟时间易于配置。串行端口用于GUI和ADuC7026之间的通信。

图 11.电源配置图形用户界面。

结论

使用AD7656-1和ADuC7026评估板开发并验证了一种简单、经济高效的方法来评估电源排序的影响。ADuC7026评估板为四个电源生成一个可控的可编程序列,以评估ADC在不同电源时序/斜坡条件下的工作情况。微控制器中的三相16位PWM发生器可提供总共七个电压通道。

审核编辑:郭婷

-

微控制器

+关注

关注

48文章

7547浏览量

151326 -

电源

+关注

关注

184文章

17706浏览量

249984 -

adc

+关注

关注

98文章

6496浏览量

544482

发布评论请先 登录

相关推荐

aduc7026做I2C slave,接收数据存在的疑问求解

一个基于ADuC7026实现功率放大器监控的参考设计

基于ADuC7026的网络化数据采集系统设计

ADuC7023/ADuC7024/ADuC701925/ADuC7026中文资料

ADUC7026 精密模拟微控制器,12位模拟I/O,ARM7TDMI® MCU

EVAR-ADC7026 ADUC7026/27 QUICKSTART和QUICKSTART PLUS开发

ADuC7026提供可编程电压用于评估多个电源系统

ADuC7026提供可编程电压用于评估多个电源系统

评论