SOT 降压型 DC-DC 转换器可有效地从并行端口“窃取”电源,同时 SIM/智能卡电平转换集成电路 (IC) 完成接口。这允许并行端口为低压逻辑供电并与之通信。同样的威廉希尔官方网站 也可以应用于USB设计。

对于便携式传感和数据采集应用,笔记本电脑及其并行端口(LPT)是很好的床伴。然而,为了延长电池寿命,许多微处理器和整个系统以低至1.8V的逻辑电平运行。LPT端口的5V输出信号不容易支持延长电池寿命和实现更长数据采集时间所需的低压逻辑。

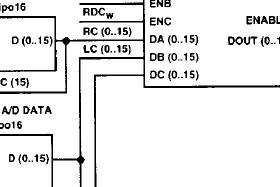

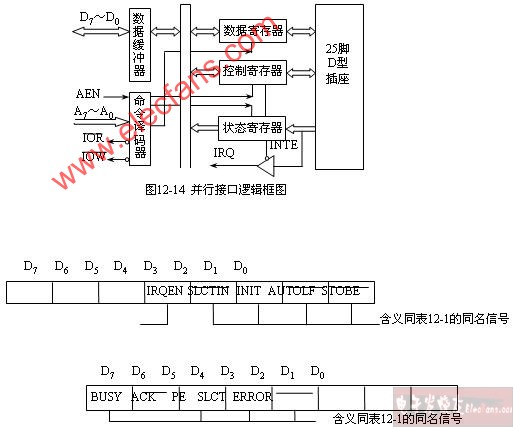

由于微处理器或时钟电路的动态功耗主要与电压(P = CV²f)有关,因此在低于5V的并行端口下工作的逻辑系统可以大大节省功耗。图中所示电路接受来自LPT端口的数据,在2V时可提供高达100mA的电流。效率高达94%。该电路将LPT端口数据引脚上的5V逻辑电平转换为2V,还提供ESD保护。

标有 U1 的低压表面贴装 IC(内置 MOSFET 和同步整流器的降压型 DC-DC 转换器)构成一个简单高效的 2V 电源。反馈电阻R1和R2将输出电压设置为低至1.25 V(示例电路中的电压设置为2V。U1 的关断引脚直接连接到 5V LPT 控制端口的位 D1(引脚 14),允许通过软件使能和禁用器件。

启用时,U1 的软启动功能可限制浪涌电流。肖特基二极管 D1 至 D3 与 5V LPT 数据端口的引脚 5 至 9 配合使用,为转换器供电。软件还可轻松启用和禁用数据端口引脚。

作为低压SIM/智能卡电平转换器,U2将逻辑电平从5V转换为2V。U2 还为输入提供 ESD 保护。低压转换器的输入侧工作在5V逻辑电平,由输入电容C1在大约5V时供电。U2 的输出侧由 2V 电源供电。数据串行读入LPT状态端口(引脚12);时钟 (CLK) 和片选(/CS)信号源自 LPT 数据端口和软件。

示例数据接口由一个8位并行负载移位寄存器(U3)和一个漏极开路逻辑门(U4)组成。它读取 U2 的 I/O 引脚并提供并行数据。PC中的软件切换CLK和/CS线,以加载并将此并行数据转移到程序中。C++软件和文本配置为将移位寄存器的并行数据转换为串行格式。但是,经过细微修改后,可以将其配置为支持微控制器接口或串行SPI、I²C或SMBus接口。

因此,该电路可以将数据发送到SPI、I²C或SMBus串行接口,或8位并行输出串行移位寄存器,如SN74HC164,后者的工作电压为2V。目前市面上的许多器件都通过工作在低至1.5V的电压来利用这些节能优势。

图1.为了节省功耗,该电路将笔记本电脑的5V LPT并行接口转换为在较低电压下工作的并行接口。

审核编辑:郭婷

-

集成电路

+关注

关注

5387文章

11536浏览量

361677 -

转换器

+关注

关注

27文章

8696浏览量

147108 -

DC-DC

+关注

关注

30文章

1943浏览量

81615

发布评论请先 登录

相关推荐

PC并行端口怎么作为数字I/O口?

增强型并行端口EPP与FIFO存储器IDT7201的接口电路

PC并行端口作为数字I/O口的应用

并行端口接口资料

可编程并行接口8255

单片机教程之并行接口P0到P3和单片机的中断系统资料概述

并行端口接口为低压系统供电

并行端口接口为低压系统供电

评论