3D NAND闪存实现了新一代的非易失性固态存储,适用于几乎所有我们可以想像得到的电子设备。

3D NAND能够实现超过2D NAND结构的数据密度,即便是在新一代威廉希尔官方网站

节点上制造时也是如此。

然而,目前提高3D NAND存储容量的方法可能会带来一些在存储器储存、结构稳定性和电气特性方面的不利影响。

3D NAND器件及其工作原理

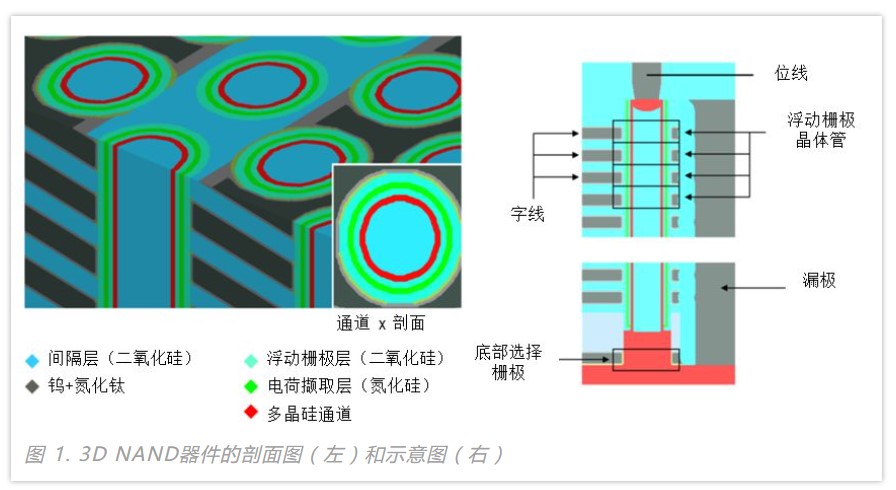

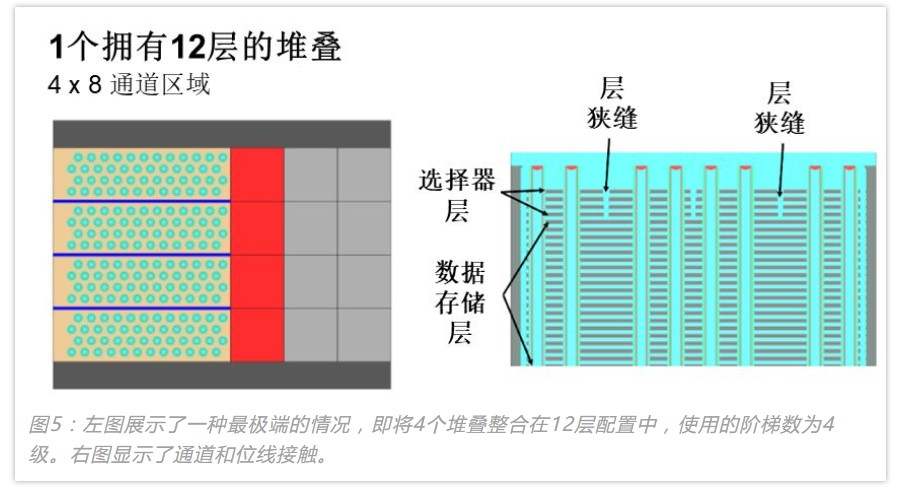

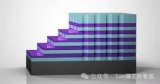

3D NAND器件包括三个主要组成部分:一是存储数据的通道区域,它以垂直方式穿过交替堆叠的导体层和绝缘层;二是“阶梯”,用于访问上文提及各层中的每个字线;三是狭缝,用于隔离连接位线的通道。下图展示了3D NAND堆叠的剖面图(左)与示意图(右):

如上图所示,电荷撷取型3D NAND结构采用钨和二氧化硅的交替堆叠,其垂直圆柱状通道穿透整个堆叠。当电压施加到字线时,电子通过隧道从通道区域移动到由氮化硅组成的电荷撷取层,数据被写入或擦除。

存储容量挑战

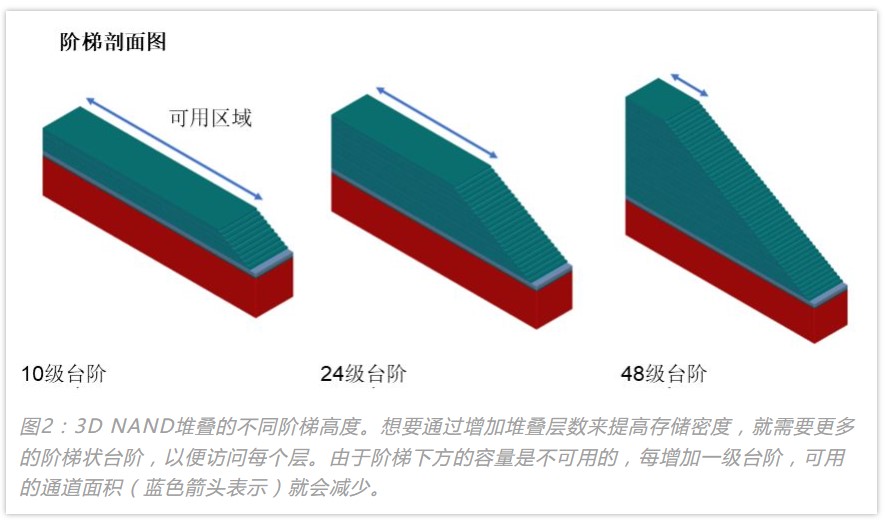

虽然3D NAND存储容量的提高看似可以通过添加更多堆叠层非常轻松地实现,但堆叠高度的增加会带来很大的挑战。如下图所示,通道的可用面积将会减小:

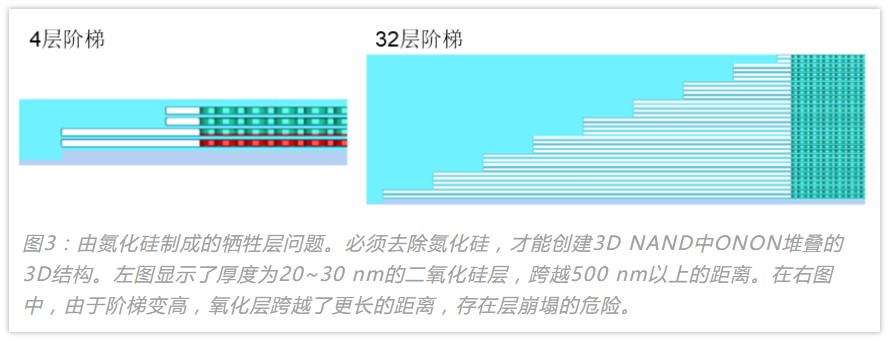

随着“阶梯”高度的提高,可用的空间随之减少。在某些类型的3D NAND中,由于去除了阶梯“台阶”之间的牺牲层,产生了更多的挑战。

在这些结构中,工程师通过湿法刻蚀去除牺牲层,是为了给之后制造工艺中的原子层沉积创造空间。

因此,更高的阶梯意味着有更长的隔离层将悬浮在空中,也意味着结构崩塌的可能性更高:

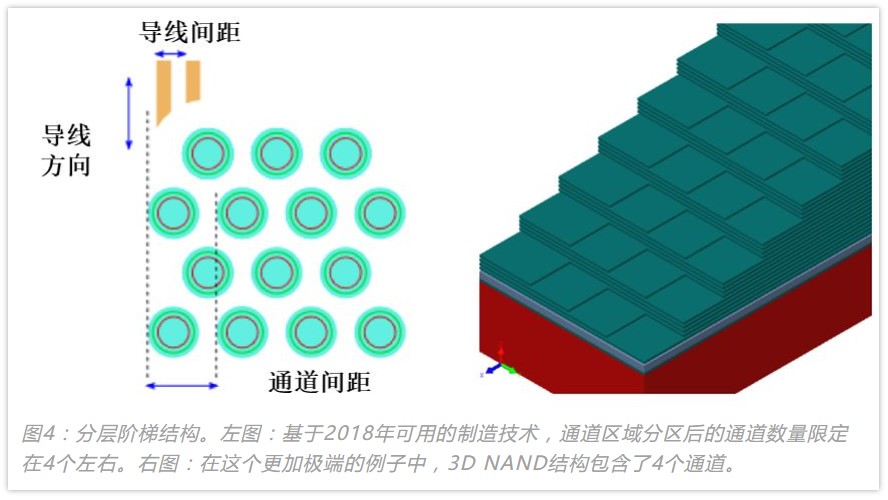

对台阶进行分区,可在台阶结构中插入更多字线接触通孔,从而创建更紧凑的阶梯,而不出现崩塌的危险。

但是,由于所有通道必须进行电气隔离,可访问通道的数量取决于适应通道间距的最小导线间距(假设每个通道都有自己的导线)。

基于目前的制造威廉希尔官方网站

(2018年底/2019年初),分区后的通道数量被限制在四个左右:

但是,更宽的堆叠(因需要的狭缝数量少而受用户欢迎)可能包含四个以上的通道,它们需要被分成多个周期组。

通过使用刻蚀工艺来穿透一部分层,将通道组隔离,有效地使用几个浮动栅级层作为选择器晶体管:

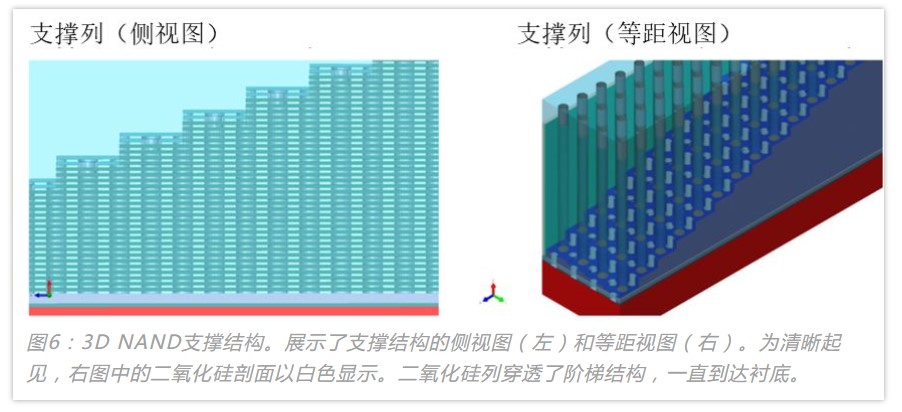

支撑列影响分析

由于3D NAND的制造工艺非常复杂,因而我们很难全面理解在存储容量和稳定性方面的各种权衡因素,以及由于在堆叠中添加更多层、台阶分区、层穿透而导致的其他属性变化。

以下所示的虚拟工艺模型interwetten与威廉的赔率体系

了建议的制造步骤。我们使用SEMulator3D®来测试不同支撑列数量和接触通孔尺寸产生的结果。

所添加的列用于在去除阶梯层之间的牺牲材料过程中支撑整个结构,它的孔由刻蚀形成,并用二氧化硅填充。

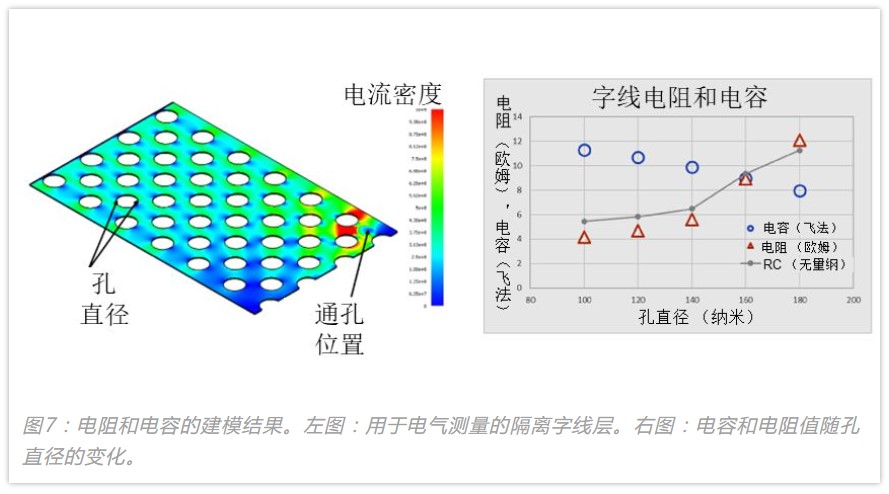

在对Semulator3D模型执行的电气分析中,我们研究了隔离字线层,并模拟了列尺寸对电阻和字线电容的影响(在右图中,孔直径表示列宽度):

扩大支撑列可以提供更好的结构稳定性,但会增加字线电阻,占用更多的空间。

因此,在器件的结构完整性允许的情况下,最大程度地减小支撑列的尺寸和数量对器件结构是有帮助的。

本研究展示了分层3D NAND阶梯结构的实际工艺模型。我们还应用了虚拟的制造威廉希尔官方网站 ,加深在使用支撑列增强高密度存储结构稳定性过程中的各种权衡因素的理解。

审核编辑:刘清

-

晶体管

+关注

关注

77文章

9684浏览量

138122 -

NAND闪存

+关注

关注

2文章

220浏览量

22751 -

固态存储

+关注

关注

1文章

51浏览量

12875

原文标题:3D NAND闪存的存储密度

文章出处:【微信号:半导体设备与材料,微信公众号:半导体设备与材料】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

预期提前,铠侠再次加速,3D NAND准备冲击1000层

3D NAND的发展方向是500到1000层

【半导体存储】关于NAND Flash的一些小知识

TechWiz LCD 3D应用:挠曲电效用仿真

3D集成电路的结构和优势

3D打印在珠宝行业的设计和制造应用-CASAIM

安宝特产品 安宝特3D Evolution:增材制造零件查找器

3D封装热设计:挑战与机遇并存

上海伯东工业级3D打印机为机器人的制造工艺带来新变革

铠侠瞄准2027年:挑战1000层堆叠的3D NAND闪存新高度

尼龙材料3D打印加工服务小批量3D打印模型制作

3D NAND结构给制造过程带来的挑战

3D NAND结构给制造过程带来的挑战

评论