AD717x是使ADC系列是市场上第一个提供真正24位无噪声输出的转换器系列。AD717x器件可为对噪声敏感度极高的仪表电路设计人员提供最大的动态范围,从而降低或消除信号调理级中的前置放大器增益。这些器件还可以高速运行,并提供比以前更短的建立时间。这改善了控制环路中输入激励的响应时间,或增加了可以通过更快的每通道吞吐量进行转换的通道密度。

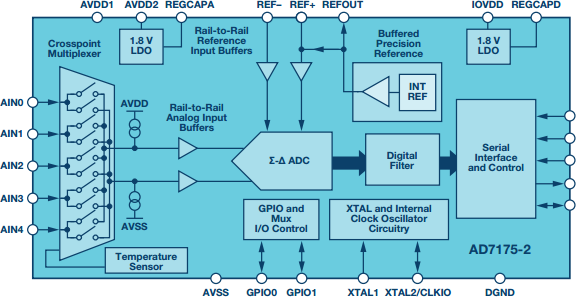

analog.com 上的AD717x页面提供了完整系列的详细信息,其中包括有关AD7172-2、AD7175-2、AD7172-4、AD7173-8和AD7175-8的信息。这些精密ADC带有完全集成的interwetten与威廉的赔率体系 信号链,具有真正的轨到轨模拟输入和基准输入缓冲器。该系列提供多种输入通道数,可通过引脚到引脚升级实现转换速度或更低噪声或低功耗替代方案。AD7175-2和AD7175-8提供最快的输出和最低的噪声。AD7177-2提供32位分辨率输出。AD7172和AD7173提供最低功耗选项。

|

无噪声峰-比特 |

输出数据速率 |

|

17.2 |

250 千秒 |

|

17.8 |

2.5 千秒 |

|

19.1 |

10 千卡SPS |

| 19.9 |

2.5 千秒 |

| 24 |

20 发 |

图1.AD7175x Σ-Δ型ADC系列;AD7175-2原理框图和噪声性能

AD7175-2内置一个非常有用的软件工具,有助于评估其。Eval+是从ADI网站下载的单个软件,可用于配置、分析和选择带或不带硬件的ADC。该软件与硬件一起运行,将按照标准评估板运行。在没有硬件的情况下,ADC的功能模型在后台运行,允许用户为其最终应用建立最佳工作配置。

图2.AD7175-2 Eval+软件在功能模型评估模式下的配置选项卡。

表 1.AD717x系列概述,显示可用的通道数选项以及系列成员的引脚对引脚对齐

|

AD717x 系列 |

24 引脚 TSSOP |

5 × 5 32 引脚 LFCSP |

6 × 6 40 引脚 LFCSP |

|||

|

无噪声位 (全速) |

调制器 (毫安) |

–阿拉伯数字 |

–4 |

–8 |

||

|

AD7175 250 千秒 |

17.2 | 8.4 |

快速、低噪声、真正的轨到轨 缓冲器,5 V电源 |

• |

• | |

|

AD7172 32 千秒 |

17.2 |

1.5 |

低功耗、真正的轨到轨缓冲器, 5 V 或 3 V 电源 |

• | • | |

|

AD7176 250 千秒 |

17.3 | 8 |

快速、低噪音、 无缓冲,5 V电源 |

• | ||

|

AD7173 32 千秒 |

17.5 | 1.5 |

低功耗、缓冲输入、 5 V 或 3 V 电源 |

• | ||

|

AD7177 10 千秒 |

19.1 | 8.4 |

快速、低噪声、32 位 真轨到轨缓冲器,5 V电源 |

• | ||

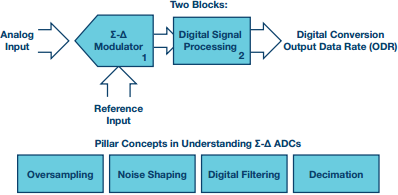

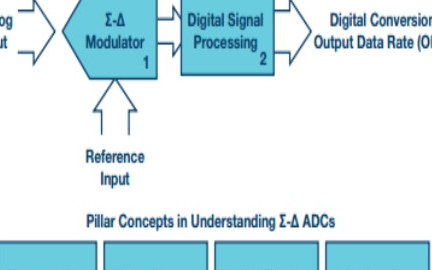

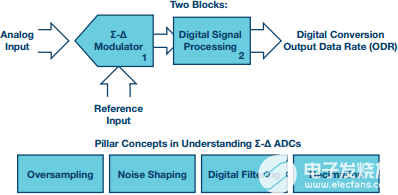

消除Σ-Δ型ADC量化噪声:噪声和带宽考虑因素

AD7175 ADC将用于说明如何利用数字滤波消除Σ-Δ型ADC的量化噪声。噪声/输入带宽和建立时间的权衡成为焦点。

图4显示了AD7175器件从直流到FMOD/2(或4 MHz)的原始调制器噪声与频率对数的关系图。AD7175调制器的有效采样率为8 MHz (FMOD)。调制器采用MASH样式,旨在为调制器噪声提供80 dB/十倍频程的斜率。电路的热噪声在到达调制器噪声开始斜坡的频轴点之前设置带内本底噪声。通过说明低本底噪声的曲线,您可以深入了解ADC对低带宽信号的高动态范围能力。这种动态范围和AD7175降低本底噪声的能力转化为用户灵敏度的提高,这在应用中采集低幅度信号时特别有用。

ADC的最小过采样比、数字滤波器阶数和转折频率都有助于确保量化噪声不是ADC噪声的限制因素。为了滤除噪声,滤波器的包络需要能够衰减,并具有足够的滚降以应对幅度量化噪声的增加速率。

AD7175的最小过采样比为×32,因此在采用8 MHz FMOD时,提供的最大输出数据速率为250 kHz。

AD7175提供多种不同的滤波器类型,可由用户选择。通过比较不同场景中的sinc5 + sinc1和sinc3滤波器来描述数字滤波器操作背后的理论。

在250 kHz ODR下,AD7175 sinc5 + sinc1直接配置为sinc5路径,−3 dB频率为~0.2 × ODR (50 kHz)。sinc5滤波器的衰减包络为−100 dB/十倍频程。这意味着sinc5滤波器的衰减和滚降足以消除调制器噪声,如图3所示。

图3.AD7175调制器输出频谱直流至FMOD/2,与sinc5 + sinc1叠加,并抽取32(实际上是sinc5 dc响应)。

图4.AD7175-2 sinc5 + sinc1滤波器:通过改变ADC的抽取率来调节输入带宽。

相反,在250 kHz ODR下更改为sinc3,衰减和滚降不足以消除调制器噪声。数据手册中250 kHz和125 kHz ODR时的噪声值表明了这一点。仅当数据速率设置为62.5 kHz及以下时,sinc3响应才能从ADC结果中完全滤除量化噪声。

除了滤除量化噪声外,数字滤波器还可用于牺牲输入带宽以降低噪声。这是通过提高抽取率来完成的。在 sinc5 + sinc1 滤波器的情况下,增加过采样率意味着初始五阶 sinc滤波器变为平均值。初始结果的平均值使用户能够从一系列不同的输出数据速率、速度和带宽中进行选择,通过sinc5和随后的sinc5 + sinc1平均值改善噪声性能(如图5所示),以改善噪声性能。对sinc5结果求平均值会在输出数据速率和该速率的倍数下引入一阶陷波,这些陷波与整个sinc5包络复合。sinc型滤波器中的陷波传统上用于抑制已知频率下的干扰源,方法是将数据速率战略性地设置为与干扰源频率一致。一个典型的例子是线路频率的50 Hz和60 Hz抑制。

图5.AD7175-2 sinc5 + sinc1滤波器 – 噪声与ODR的关系图

sinc 样式滤波器是具有 sin(x)/x 配置文件的移动平均滤波器,因此通常称为 sinc 滤波器。滤波器由一系列积分器和一个用作抽取器的开关组成,后跟一系列微分器。这是一种有限脉冲响应(FIR)类型的滤波器。它对输入端的阶跃变化表现出已知且有限的线性相位响应。作为输出数据速率和该速率的整数倍,陷波内会出现衰减信号的深陷波。

图6显示了AD7175的三阶和五阶sinc滤波器的比较,两者的抽取率为32。在这种情况下,两个滤波器都将以250 kHz的输出速率提供转换数据。滤波器的阶数决定了滚降和−3 dB频率。sincP滤波器将位于–P×20 dB/十倍频程的频率响应包络下。陡峭的滚降产生较低的−3 dB频率。不同阶次滤波器之间的主要权衡在于滤波器的建立时间,根据场景的不同,这对最终测量应用有不同的影响。

图6.sinc滤波器不同阶次的频域比较:sinc5与sinc3。

滤波器建立时间

当数字滤波器处理来自Σ-Δ调制器的数据流的移动平均值时,存在相关的建立时间。对于任何FIR滤波器,延迟都是固定的,但对于每个sinc滤波器顺序,延迟是不同的。延迟通常用两个术语来描述:群延迟和建立时间。群延迟描述了从输入端的模拟信号到数字输出端的模拟信号之间的延迟。例如,对于单音正弦波,它是模拟输入端存在的正弦波电压峰值与数字输出端出现的相同峰值之间的时间。

建立时间是数字滤波器的全平均时间。如果模拟输入端有阶跃,则滤波器需要完整的建立时间,直到ADC的数据输出与输入端的上一步没有相关性。可能存在其他延迟,例如滤波器的计算时间。对于AD7175系列,第一次转换的建立时间较长,或者由于初始计算周期为1/ODR,从待机状态出来后建立也会产生延迟。除滤波器建立时间外,任何延迟都可能因所选转换器而异,因此在阅读ADC数据手册时要小心。

通过将单个Σ-Δ型ADC场景与多路复用Σ-Δ型ADC方案进行比较,可以最好地显示滤波器建立时间效应。数字滤波器的建立时间会严重影响用户在保持每个通道结果独立的情况下循环多个输入通道的速率。

为什么需要等待完整的建立时间才能给出独立的结果?让我们看一下具有单个输入源的单个ADC的数字滤波。来自调制器Σ-Δ ADC的数据以FMOD速率传递到数字滤波器(如图5所述),每个样本通过移动平均滤波器。根据顺序和样式,滤波器在转换时间段(由滤波器抽取率设置)内对每个样本进行不同的加权,如图7所示。输入样本0和后续样本是分立调制器输出结果,由调制器时钟的单个周期隔开。y 轴刻度由数字滤纸对每个样品的称量进行称量。该称重的形状是低通数字滤波器的时域表示。这种情况下的输出数据速率为250 kHz(8 MHz/32 = FMOD/抽取率)。数据就绪信号(每种不同颜色的垂直虚线)之间的时间为4 μs。ADC设置为与sinc5 + sinc1滤波器一起运行,抽取率为32。所有五个转换输出在定义滤波器输出的调制器输入中都有一些重叠,因此没有一个是相互独立的。对于单个ADC输入,每个转换结果共享来自调制器的输入,但滤波器对这些调制器输出的权重不同。

图7.单 ADC 输入、sinc5 和 5 个转换输出周期。

对于多路复用输入情况,为创建每个转换输出而提供的调制器数据对于每个通道必须是独立的。在多路复用器从一个模拟输入通道切换到下一个模拟输入通道之前,滤波器的完全建立时间必须经过。以sinc3型滤波器为例,使用抽取率为32,图8 (a)中说明了一次转换的滤波器建立时间。滤波器完全建立后,数据输出是调制器前96个输出的加权平均值。这相当于ADC输出数据速率的12 μs或三个周期。

图8 (b)显示了多路复用情况下的前三个样本,其中ADC输出的每个样本都完全建立。调制器输出在任何样本之间不重叠。由DRDY(垂直线)之间的时间指示的多路复用速率由滤波器的建立时间决定。该速率通常在数据手册和参数图中描述为完全建立的数据速率。

图8.多路复用ADC、sinc3滤波器和三个转换周期——完全建立的数据

对于sincP滤波器,滤波器的建立时间为滤波器阶数P乘以1/ODR。对于以250 kHz ODR运行的sinc3滤波器,这意味着滤波器的建立时间为3 × 1/250 kHz = 12 μs。相比之下,如果在相同的ODR为250 kHz的情况下使用sinc5滤波器,则滤波器的建立时间为5 × (1/2 50 kHz) = 20 μs。

在通道之间切换的近似速率是 ODR 除以滤波器的阶数,因此 sinc3 为 ODR/3,sinc5 滤波器为 ODR/5。对于直接sinc滤波器来说,这是直接的。对于 sinc5 + sinc1 样式等情况,需要添加步骤。AD7175系列ADC能够在不同样式的滤波器之间进行选择。下一节将演示滤波器类型之间的差异,并提供计算每种情况的建立时间的示例。

让我们计算出多路复用场景的建立时间。过程控制和工厂自动化中的典型模拟输入模块将具有一个前端级,可将±10 V输入调节至AD7175-8的输入范围。然后,AD7175-8将通过每个通道进行多路复用,按顺序转换每个输入或输入对。转换所有通道的时间取决于所使用的滤波器以及通道的数量。

以下示例比较了sinc3滤波器和sinc5 + sinc1滤波器的使用,两者都配置为相同的输出数据速率,我们将看到对比度和计算建立时间的方法。两种滤波器选项,可由AD7175-8的用户选择。

一个。使用 sinc3 滤波器,ODR

为 62.5 kHz 计算建立时间

AD7175 sinc3:ODR = 62.5 kHz 建立时间 = 3 × (1/62.5 kHz) = 48 μs,

通道切换速率 = 1/48 μs = 20.833 kHz

b.使用 sinc5 + sinc1 滤波器,62.5 kHz ODR

计算建立时间。

AD7175 辛克5 + 辛克1: ODR = 62.5 kHz

请注意,有两个组件。sinc5滤波器在4 μs窗口(FMOD = 8 MHz)内取平均值,因此它以250 kHz的速率将数据传递到平均模块。

1. sinc5 = 5 × 1/250 kHz = 20 μs 的建立时间。

这为平均提供了第一个样本。

2.建立sinc1,平均滤波器。

对于 ODR = 62.5 kHz,250 kHz 数据流的平均值为四倍。

其余三个样本

的平均建立时间为3 × 1/250 kHz = 12 μs。

总建立时间 = 20 μs + 12 μs = 32 μs,

通道切换速率 = 1/32 μs = 31.25 kHz。

请注意,对于sinc5 + sinc1滤波器,ADC的10 kSPS及以下数据速率具有单周期建立。这意味着ADC的建立时间= 1/ODR。

表 2 显示了 4 通道多路复用测量与设置 (a) 和 (b) 的比较。使用 sinc5 + sinc1 滤波器可实现更快的每通道采样速率,显示出更短建立时间的优势。请注意,此经验法则仅与转换器有关,如果每个输入之前都有模拟预处理电路,其时间常数比ADC长,则最差情况的建立时间将占主导地位。

这种比较如表2所示:

表 2.4通道多路复用系统(例如,使用AD7175-8)的Sinc5 + Sinc1与Sinc3滤波器的每通道数据速率比较

| 过滤器类型 |

外径 (千赫) |

每通道 建立时间(μs |

转换 四通道的时间 (μs) |

每通道 数据速率 (kHz) |

|

辛克5 + 辛克1 |

62.5 |

32 | 128 | 7.8125 |

|

辛克3 |

62.5 |

48 | 192 | 5.208 |

Σ-Δ型ADC的概述到此结束了,Σ-Δ型ADC是围绕调制器和概念的理论,然后是数字滤波的示例,以及它们对噪声、建立时间的影响,以及测量系统中两者的一些连锁效应。

审核编辑:郭婷

-

转换器

+关注

关注

27文章

8696浏览量

147109 -

adc

+关注

关注

98文章

6496浏览量

544500 -

调制器

+关注

关注

3文章

840浏览量

45143

发布评论请先 登录

相关推荐

请问AD717X数据采集错误是什么原因?

Σ-Δ型ADC拓扑结构基本原理:第二部分

模数转换器(ADC)的基本原理是什么

ADC的基本原理是什么

Σ-Δ型ADC拓扑结构 基本原理

Δ型ADC拓扑结构原理详解(AD717x为例)

Σ-Δ型ADC拓扑背后的基本原理:第1部分

Σ-Δ型ADC拓扑背后的基本原理:第2部分

AD717x:Σ-Δ型ADC拓扑背后的基本原理

AD717x:Σ-Δ型ADC拓扑背后的基本原理

评论