第1部分介绍了 ESD 的基本概念及其与系统设计的关系。

第2部分为 ESD 系统设计提供了战略指导,介绍了用于板载 ESD 保护的工具和组件。

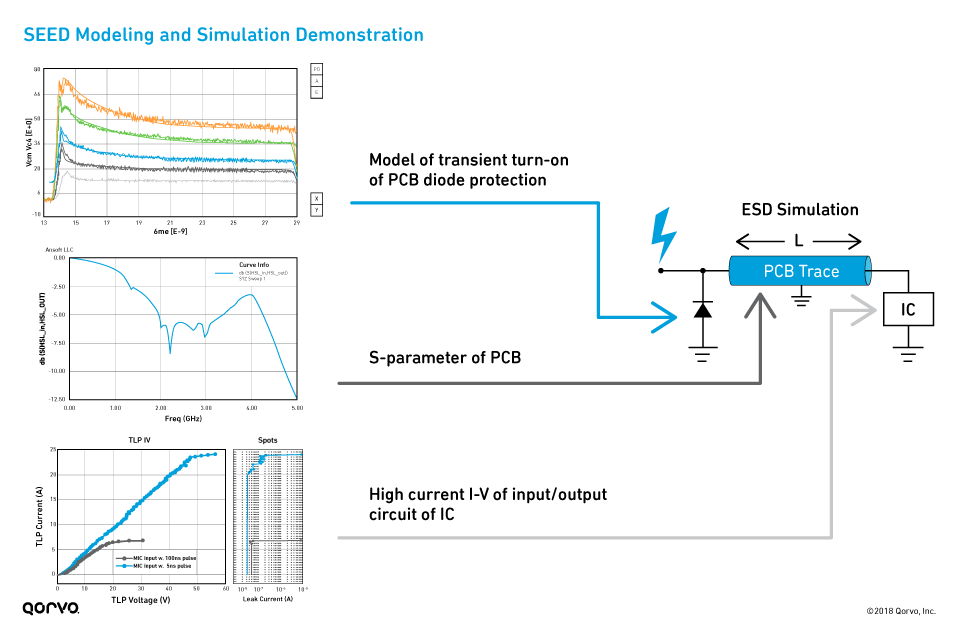

第3部分(本篇博文)将介绍系统高效 ESD 设计 (SEED) 建模威廉希尔官方网站 和 RF 前端 (RFFE) 设计的考虑因素。

综合各种因素

通常,系统设计人员使用反复试验的方法来添加 ESD 保护。那是否存在负面影响呢?仅使用组件级 ESD 规范不足以实现稳健的系统设计。我们的目标是预测最终手机设计的 ESD 性能,以创建一个提供 ESD 保护的万无一失、一次性过关的系统设计。

最佳方法之一是使用模型来仿真IEC 61000-4-2接触放电脉冲,这样您就可以在确定 ESD 性能之后才投入时间和成本,用于实际的原型设计。

为此,我们采用系统高效ESD设计(SEED)方法。如果您有兴趣了解有关 SEED 的更详细信息,可以进一步阅读 ESD 工业委员会白皮书系统级ESD第1部分:常见误区及推荐的基本方法。

SEED 是一种板载和片上ESD保护的协同设计方法,它有助于分析和实现系统级 ESD 稳健性能。该方法要求对 ESD 应力事件期间的外部 ESD 脉冲之间的相互作用、完整的系统级板设计以及设备引脚特性有一个全面的了解。.

板载保护与片上保护

有关一级和二级 ESD 保护的细分以及 RFFE 保护的战略,请参阅本博文系列第2部分。

SEED 建模和仿真的主要步骤

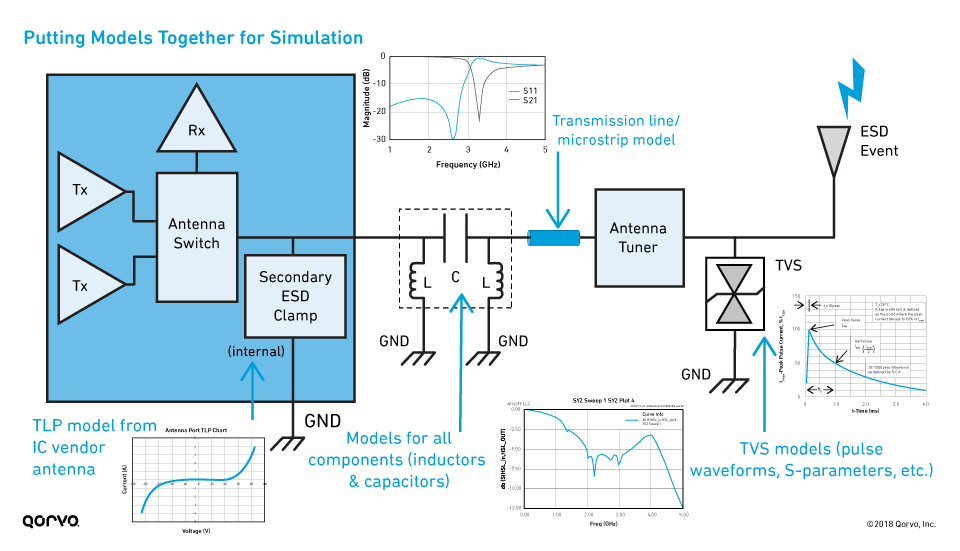

SEED 方法需要对系统的各种组件和轨迹进行建模和仿真。总体来说,使用 SEED 方法的建模和仿真步骤包括:

第 1 步:收集系统信息,例如:

PC 板 Gerber 文件,包括 PC 板材料规格(堆叠文件、传输线规格等)

瞬态电压抑制器(TVS)、电感和电容的器件型号(S‑参数、I-V 特性、ESD 额定值、IV-TLP 特性等)

RF 前端模块 I/O 引脚的片上 ESD 保护模型(IV-TLP 测量、S‑参数、ESD 额定值等)

第 2 步:运行瞬态和 RF 仿真,对 ESD 保护器件在系统级 ESD 应力和正常工作期间的行为进行建模。

建模和仿真工具

当今的 RF 工程师使用多种设计工具。仅举几个例子,包括:

Keysight Technologies高级设计系统(ADS)

National InstrumentsAWR设计环境–Microwave Office

SPICE仿真软件

这些工具均适用于您的 ESD SEED 仿真。

具体步骤:如何进行 SEED 仿真

让我们通过一个简单的示例来说明如何使用 SEED 方法来设计 ESD 保护。

首先,您需要确定系统中所需的隔离阻抗,以确保 IC 引脚的峰值 ESD 电流和电压在片上(次级钳位)保护能力的范围内。这通过利用 IEC 应力模型和板载 TVS 组件的传输线脉冲(TLP)数据(初级钳位)和 IC 接口引脚(次级钳位)创建仿真来完成。

最终,您的目标是确认实现系统 ESD 保护所需的组件。为此,需完成以下步骤:

创建 ESD 脉冲。

加载 Gerber 文件。

将所有其他组件加载到建模软件中。

运行仿真以确定 RFFE 引脚处的 IEC 应力水平。

确定实现板载 ESD 保护所需的组件。

将组件添加到模型中。

重新运行仿真以验证添加的组件是否有效。

通过 ESD 测试后,进行最终的 PC 板布局。

让我们对每一步进行详细阐述。

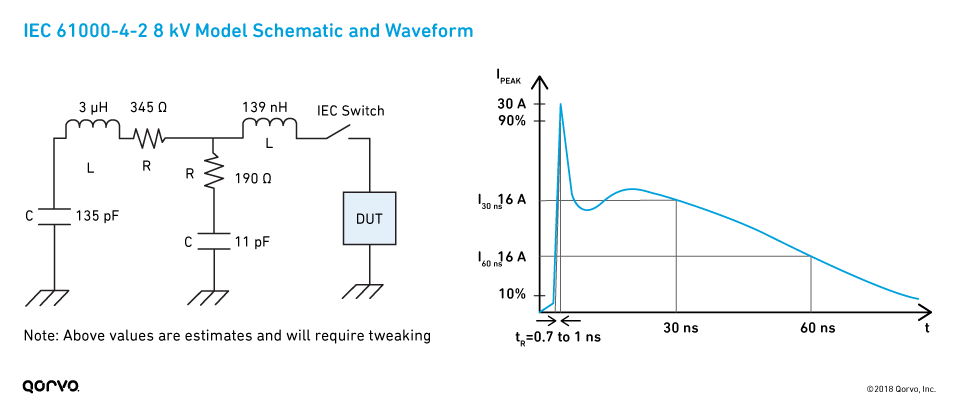

第 1 步:使用 IEC61000-4-2 规范值来创建 ESD 脉冲

将如下所示的RLC(电阻-电感-电容)电路的模型原理图加载到仿真工具中,并验证是否得到如下所示的波形。该模型将仿真 ESD 脉冲。请注意,某些值可能需要调整才能获得精确的波形。

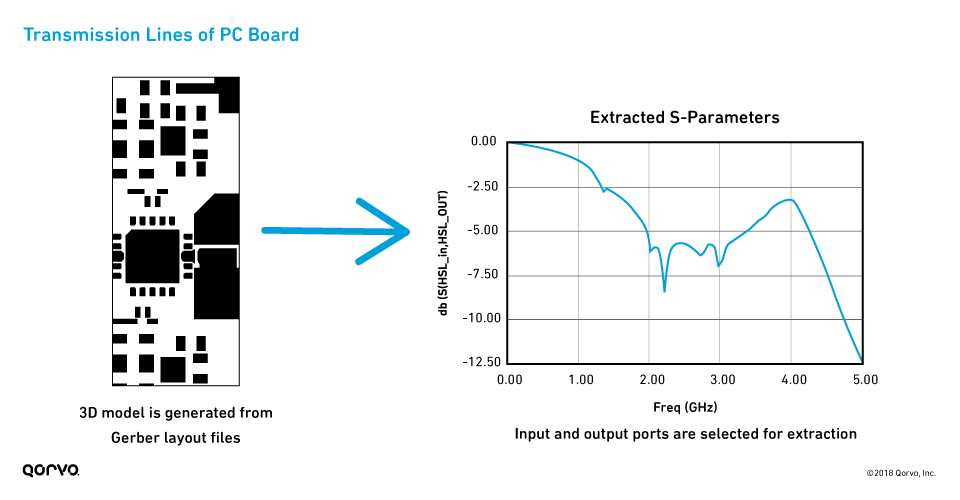

第 2 步:加载 Gerber 文件

接下来,使用 3D Gerber 布局文件来评估 PC 板的走线。将这些文件放入建模软件中。对布局轨迹进行建模,例如微带线的尺寸。

第 3 步:将所有其他组件加载到建模软件中

这些组件包括:

TLP I/O 器件引脚数据

匹配组件

传输线组件

第 4 步:运行仿真

加载完所有组件后,您希望查看结果如何。此时,您要确定 RFFE 引脚的 IEC 应力水平。如果该水平值超出内部 IC 保护的能力,那么您将需要添加板载 ESD 保护,例如隔直电容、TVS 二极管等。

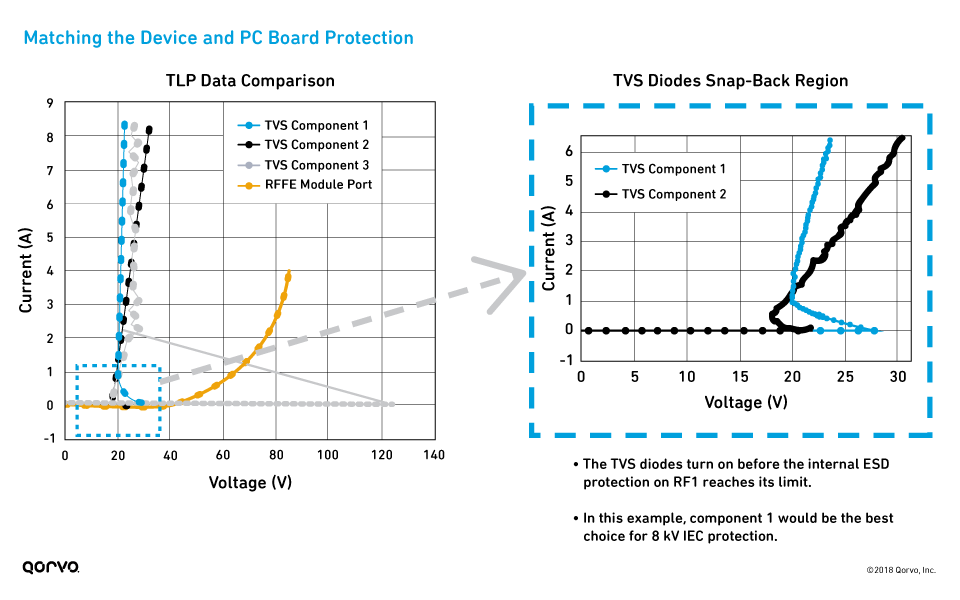

第 5 步:确定实现板载 ESD 保护所需的组件

我们在本系列博文的第 2 部分中介绍了ESD保护的不同组件和战略。比较可用的各个保护组件,以确定最适合您设计的组件。

例如,假设仿真显示您的系统需要额外的板载保护。下图显示了通过比较 TLP 模型的数据查看的几个组件。橙色线是采用 Qorvo RFFE 模块端口的 TLP 模型。其他三个 TLP 模型是正在评估的 TVS 组件。根据以下 TLP 数据,组件 1 和组件 2 是两个最佳选择。它们都符合我们的系统要求;然而,进一步分析了位移回跳区域后,我们选择组件 1,因为它的触发电压更低。触发电压更低意味着 TVS 不太可能通过削弱系统信号性能影响我们的设计。

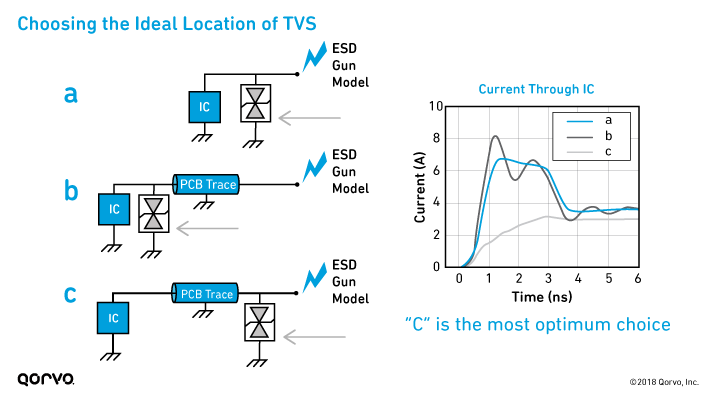

我们选择了 TVS 组件后,将其放置在正确的板载位置也非常重要。如下图所示,将 TVS 移近 ESD 入口点可以最大限度地降低 ESD 能量。PC 板的走线可根据 TVS 位置增加和减少第一个峰值电流的幅度。

第 6 步:将组件添加到模型中

一旦选择了 ESD 保护元件(在我们的示例中为 TVS 二极管),您需要将它们添加到仿真中,如下所示。

第 7 步:重新运行仿真以验证添加的板载 ESD 组件是否有效

现在所有数据都加载到您的仿真中,您可以运行瞬态interwetten与威廉的赔率体系 ,分析 RF 路径的电流/电压曲线,并调整内部引脚(例如模块引脚)上的最小残留值以及系统性能。

注意:紧凑型仿真器支持使用 S 参数数据进行瞬态模拟。S 参数数据也可以在需要时转换为集总模型。

最终目标是您的系统设计能通过 IEC 应力测试。不同的应用将需要不同的组件或战略,而在设计阶段初期对它们进行建模将有助于提高通过 IEC 认证的可能性。

第 8 步:进行最终的 PC 板布局

一旦您的设计通过了仿真,您就可以进行最终的系统 PC 板布局。使用 SEED 的不同之处在于,您直到完成板载 ESD 保护仿真与建模之后才进行系统 PC 板布局——而不是在设计阶段的初期。

使用 SEED 提高通过 ESD 认证的可能性

SEED 能够更好地理解系统性能和 IC ESD 设计功能。IV-TLP 曲线提供有关片上、模块内和板载 ESD 功能的所需信息。将瞬态模拟添加到曲线图上,即可评估片上和板载 ESD 保护器件的整体行为,以及它们在系统级 ESD 应力下的协同表现。这样,从硬件开发的初始阶段就能够放心地构建最佳协同设计——最终可提高效率并降低总体设计成本。

审核编辑黄昊宇

-

ESD

+关注

关注

49文章

2031浏览量

172960 -

RF

+关注

关注

65文章

3053浏览量

166993

发布评论请先 登录

相关推荐

用于优化 ESD RF 前端设计的 SEED 方法(第 3 部分,共 3 部分)

用于优化 ESD RF 前端设计的 SEED 方法(第 3 部分,共 3 部分)

评论