一块好的电路板,除了实现电路原理功能之外,还要考虑 EMI、EMC、ESD(静电释放)、信号完整性等电气特性,也要考虑机械结构、大功耗芯片的散热问题,在此基础上再考虑电路板的美观问题,就像进行艺术雕刻一样,对其每一个细节进行斟酌。

常见PCB布局约束原则

在对 PCB元件布局时经常会有以下几个方面的考虑。

(1)PCB板形与整机是否匹配?

(2)元件之间的间距是否合理?有无水平上或高度上的冲突?

(3)PCB是否需要拼版?是否预留工艺边?是否预留安装孔?如何排列定位孔?

(4)如何进行电源模块的放置及散热?

(5)需要经常更换的元件放置位置是否方便替换?可调元件是否方便调节?

(6)热敏元件与发热元件之间是否考虑距离?

(7)整板 EMC性能如何?如何布局能有效增强抗干扰能力?

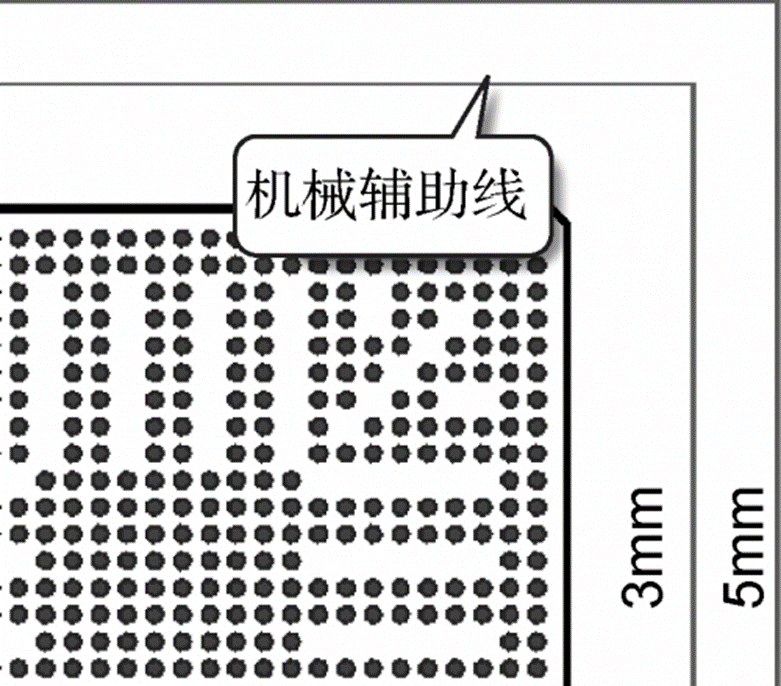

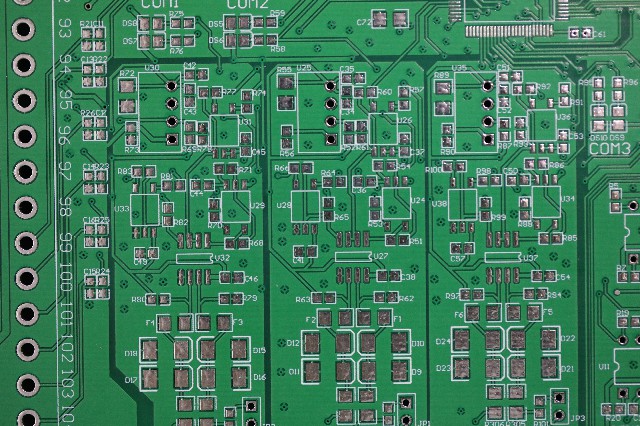

对于元件和元件之间的间距问题,基于不同封装的距离要求不同和 Altium Designer自身的特点,如果通过规则设置来进行约束,设置太过复杂,较难实现。一般是在机械层上画线来标出元件的外围尺寸,如图 9-1所示,这样当其他元件靠近时,就大概知道其间距了。这对于初学者非常实用,也能使初学者养成良好的 PCB设计习惯。

通过以上的考虑分析,可以对常见 PCB布局约束原则进行如下分类。

元件排列原则

(1)在通常条件下,所有的元件均应布置在 PCB的同一面上,只有在顶层元件过密时,才能将一些高度有限并且发热量小的元件(如贴片电阻、贴片电容、贴片 IC等)放在底层。

(2)在保证电气性能的前提下,元件应放置在栅格上且相互平行或垂直排列,以求整齐、美观。一般情况下不允许元件重叠,元件排列要紧凑,输入元件和输出元件尽量分开远离,不要出现交叉。

(3)某些元件或导线之间可能存在较高的电压,应加大它们的距离,以免因放电、击穿而引起意外短路,布局时尽可能地注意这些信号的布局空间。

(4)带高电压的元件应尽量布置在调试时手不易触及的地方。

(5)位于板边缘的元件,应该尽量做到离板边缘有两个板厚的距离。

(6)元件在整个板面上应分布均匀,不要这一块区域密,另一块区域疏松,提高产品的可靠性。

按照信号走向布局原则

(1)放置固定元件之后,按照信号的流向逐个安排各个功能电路单元的位置,以每个功能电路的核心元件为中心,围绕它进行局部布局。

(2)元件的布局应便于信号流通,使信号尽可能保持一致的方向。在多数情况下,信号的流向安排为从左到右或从上到下,与输入、输出端直接相连的元件应当放在靠近输入、输出接插件或连接器的地方。

防止电磁干扰

电感与电感垂直 90°进行布局

(1)对于辐射电磁场较强的元件及对电磁感应较灵敏的元件,应加大它们相互之间的距离,或考虑添加屏蔽罩加以屏蔽。

(2)尽量避免高、低电压元件相互混杂及强、弱信号的元件交错在一起。

(3)对于会产生磁场的元件,如变压器、扬声器、电感等,布局时应注意减少磁力线对印制导线的切割,相邻元件磁场方向应相互垂直,减少彼此之间的耦合。图 9-2所示为电感与电感垂直 90°进行布局。

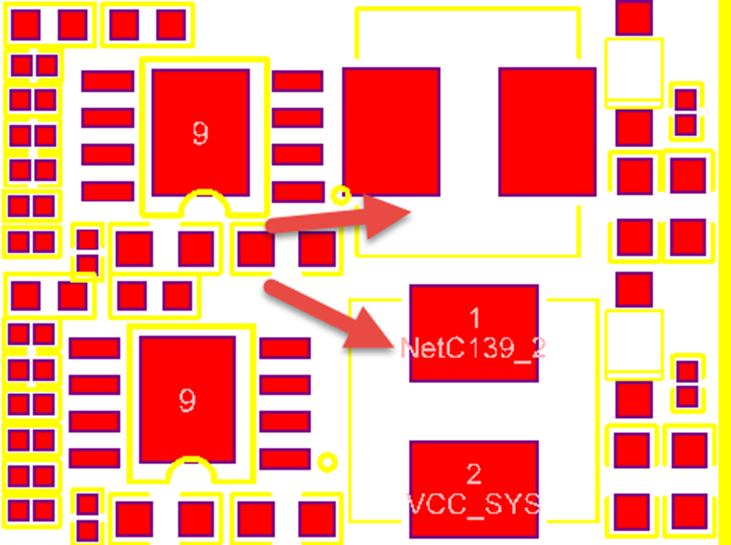

(4)对干扰源或易受干扰的模块进行屏蔽,屏蔽罩应有良好的接地。屏蔽罩的规划如图 9-3所示。

抑制热干扰

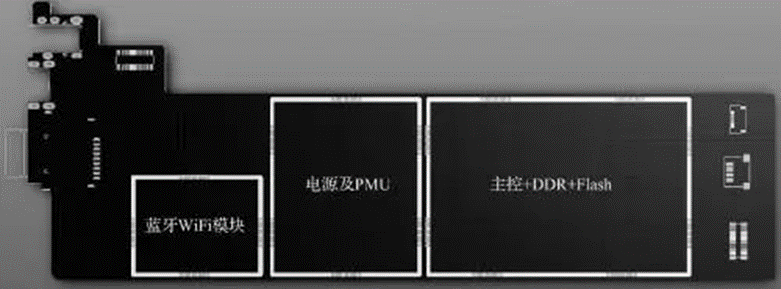

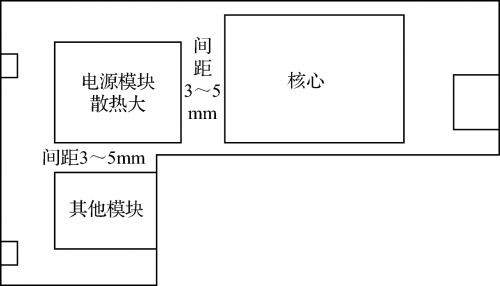

(1)对于发热元件,应优先安排在利于散热的位置,必要时可以单独设置散热器或小风扇,以降低温度,减小对邻近元件的影响,如图 9-4所示。

(2)一些功耗大的集成块、大功率管、电阻等,要布置在容易散热的地方,并与其他元件隔开一定距离。

屏蔽罩的规划

布局的散热考虑

(3)热敏元件应紧贴被测元件并远离高温区域,以免受到其他发热功当量元件的影响,引起误动作。

(4)双面放置元件时,底层一般不放置发热元件。

可调元件布局原则

对于电位器、可变电容器、可调电感线圈、微动开关等可调元件的布局,应考虑整机的结构要求:若是机外调节,其位置要与调节旋钮在机箱面板上的位置相适应;若是机内调节,则应放置在 PCB上便于调节的地方。

审核编辑 黄昊宇

-

pcb

+关注

关注

4319文章

23094浏览量

397761

发布评论请先 登录

相关推荐

和 Dr Peter 一起学 KiCad 4.3:轮廓与约束 (Edge cut板框)

一文让你了解PCB六层板布局

Cadence快板PCB培训

RISC-V迈入HPC市场,性能与生态缺一不可

关于PCB布局布线技巧的104的问题

FPGA物理约束之布局约束

PCB板布局约束原则,缺一不可

PCB板布局约束原则,缺一不可

评论