许多通信、仪器仪表和信号采集系统要求能够同时对多个模数转换器(ADC)上的interwetten与威廉的赔率体系 输入信号进行采样。然后,需要处理采样的数据,期望在这些输入之间同步,每个输入都有自己不同的延迟。对于系统设计人员来说,历来是应对低压数字信号(LVDS)和并行输出ADC的艰巨挑战。

JESD204B提供了一个框架,用于沿一个或多个差分信号对(例如ADC的输出)发送高速串行数据。接口中有一个固有的方案,可在JESD204B规范内实现跨通道的粗略对齐。数据被划分为具有边界的帧,这些帧连续发送到接收器。JESD204B子类1接口通过使用系统参考事件信号(SYSREF)同步发射器和接收器中的内部成帧时钟,可在多个串行通道链路或多个ADC上实现低至采样级的数据对齐。这会为使用JESD204B链路的设备创建确定性延迟。然而,系统设计人员仍必须克服许多挑战才能实现采样同步的完全时序收敛,例如PCB布局考虑因素、匹配时钟以及满足时序、SYSREF周期性和数字FIFO延迟的SYSREF生成。

设计人员必须决定如何在整个系统中创建和分配器件时钟和SYSREF信号。理想情况下,器件时钟和SYSREF应具有相同的摆幅电平和失调,以防止元件输入引脚出现固有偏斜。需要将 SYSREF 事件的更新速率确定为启动时的单个事件或需要同步时随时可能发生的重复信号。考虑到最大时钟和SYSREF信号偏斜,需要仔细的PCB布局,以满足跨电路板、连接器、背板和各种组件的设置和保持时序。最后,数字FIFO设计和跨多个时钟域的信号会在JESD204B发送器和接收器中产生固有的数字缓冲器偏斜,在后端数据处理中必须考虑和消除这些偏差。

系统时钟生成可以来自多个来源,例如晶体、VCO 和时钟生成或时钟分配芯片。虽然特定的系统性能将决定时钟需求,但必须使用多个同步ADC来产生与输入时钟同步的SYSREF信号。这使得时钟源选择成为一个重要的考虑因素,以便能够在特定时间点以已知的时钟边沿锁存此系统参考事件。如果 SYSREF 信号和时钟未相位锁定,则无法实现。

FPGA 可用于向系统提供 SYSREF 事件。但是,除非它还使用并同步发送到ADC的主采样时钟,否则很难将来自FPGA的SYSREF信号与时钟相位对齐。另一种方法是提供来自时钟发生或时钟分配芯片的 SYSREF 信号,该芯片可以将该信号相位对齐到整个系统中发送的多个时钟。使用此方法,SYSREF 事件可以是启动时的一次性事件,也可以是重复出现的信号,具体取决于系统要求。

只要ADC和FPGA的系统内确定性延迟保持不变,除了帮助构建特定系统数据外,可能不需要额外的SYSREF脉冲。因此,时钟对齐的周期性SYSREF脉冲可以被忽略或滤波,直到同步丢失。也可以保留SYSREF发生的标记样本,而无需重置JESD204B链路。

为了启动ADC通道的已知确定性起点,系统工程师必须能够关闭分布在整个系统中的SYSREF事件信号的时序。这意味着必须满足相对于时钟的预期建立和保持时间,而不会违反。使用跨越多个时钟周期的相对较长的SYSREF脉冲可以满足保持时间要求,只要也可以满足到第一个所需时钟的建立时间。仔细注意PCB布局对于保持系统内时钟和SYSREF的匹配走线长度以实现最小偏差至关重要。这可能是实现跨通道同步采样处理最困难的部分。随着ADC编码时钟速率的增加和多板系统变得更加复杂,这项工作只会变得越来越具有挑战性。

系统工程师必须确定每个器件对电路板和连接器组件的时钟板偏斜的 SYSREF。任何剩余的器件间数字和时钟偏斜延迟都需要在FPGA或ASIC中有效消除。后端处理可以改变ADC之间的采样顺序,并引入任何需要的重新调整,以准备数据以进行进一步的同步处理。器件间采样偏斜的校正可以通过延迟最快的数据样本和发射器延迟来实现,以与后端FPGA或ASIC中最慢的数据样本保持一致。对于复杂系统,这可能涉及多个FPGA或ASIC,每个FPGA或ASIC都需要传达其总器件间采样延迟以进行最终对准。通过在JESD204B接收器中引入适当的弹性缓冲延迟以适应每个特定的发送器延迟延迟,器件间采样偏斜可以与整个系统中的已知确定性保持一致。

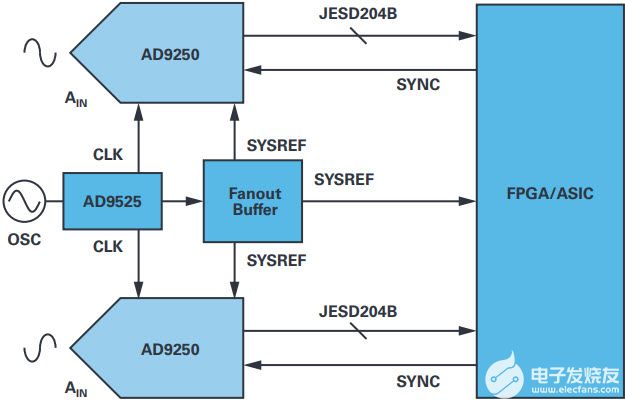

AD9250是ADI公司的250 MSPS 14位双通道ADC,支持子类1实现中的JESD204B接口。该子类允许使用 SYSREF 事件信号在 ADC 之间进行模拟采样同步。AD9525是一款低抖动时钟发生器,不仅提供7路高达3.1 GHz的时钟输出,还能够根据用户配置同步SYSREF输出信号。这两款产品与ADI公司的一系列扇出缓冲器产品相结合,提供了精确同步和对齐发送到FPGA或ASIC进行处理的多个ADC数据的框架。

图1.显示AD9250、AD9525和FPGA的图表。

审核编辑:郭婷

-

adc

+关注

关注

98文章

6497浏览量

544537 -

lvds

+关注

关注

2文章

1043浏览量

65803 -

发送器

+关注

关注

1文章

259浏览量

26818

发布评论请先 登录

相关推荐

JESD204B的系统级优势

JESD204B串行接口时钟的优势

jesd204b ip核支持的线速率

如何让JESD204B在FPGA上工作?FPGA对于JESD204B需要多少速度?

JESD204B协议有什么特点?

通过同步多个JESD204B ADC实现发射器定位参考设计

JESD204B协议介绍

JESD204B标准及演进历程

使用JESD204B同步多个ADC

悄悄告诉你们如何使用JESD204B同步多个ADC!

通过同步多个JESD204B ADC实现发射器定位参考设计

使用JESD204B同步多个ADC

使用JESD204B同步多个ADC

评论