本系列的前一期是从理解数据手册到实际实现以实现预期性能的转变。这包括对模数转换器(ADC)输入信号的电源和信号路由的考虑。最后一期将重点介绍差分信号的优势,现在许多微控制器(MCU)都提供了差分信号。

差分信号是在interwetten与威廉的赔率体系 测量过程中解决噪声的宝贵工具。差分信号的优势在于将噪声作为共模消除的简单性。挑战在于设计一个电路,使差分对的两个导体实际上具有共性噪声。这一挑战延伸到嵌入式硬件工程师和集成电路(IC)设计人员。

在IC设计中,基板噪声是一个挑战。基板充当产生噪声的元件或外设与集成ADC之间的桥梁或介质。同样,在板级,相邻的数字信号可以与模拟走线耦合。这种耦合的强度通常会因不良(高阻抗)接地结构而增强,迫使返回路径较长,从而增加电磁场边缘。对于辐射抗扰度,与无线电的距离相比,差分间距应该相对较小。在这三种情况下,假设噪声与正极和负极导体相等耦合,并且噪声在两个导体上的传播相等。这突出了差分信号对称性的必要性,以便抑制共模信号,例如IC、电路板和应用(系统)级的噪声。

在讨论差分信号的好处之前,重要的是要提到成本。在MCU上,成本是ADC输入引脚数量的两倍。在整个信号链中,构成模拟前端(AFE)的组件也会加倍或复制。与任何设计一样,您必须权衡这些成本与收益。

以下部分说明了在IC级、板级和应用级差分信号的优势,在被测器件(DUT)附近放置Sub-1 GHz无线电。

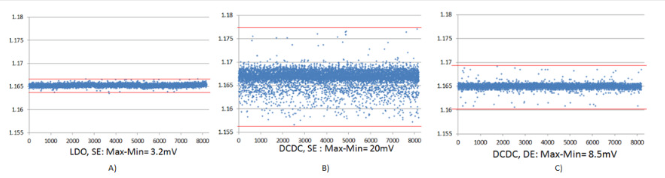

在IC级,电源管理架构会给系统带来噪声,在比较一种架构相对于另一种架构的优势时,应考虑这一点。对于内部电压调节,IC可以使用低压差稳压器(LDO)或DC/DC转换器。虽然DC/DC通常是两者中效率更高的,但图1b显示,相对于图1a中的LDO,DC/DC也贡献了更多的噪声。噪声等同于ADC返回的最小和最大电压之差的增加。在图1a和图1b中,ADC测量直流电压约为250KSPS,持续32ms。DC/DC稳压器的转换结果变化是LDO的六倍以上。

图 1:具有单端测量的内部 LDO 稳压器 (a);具有单端测量的内部 DC/DC 稳压器 (b);带差分端测量的内部 DC/DC 稳压器 (c)

比较图1b和1c,如果在差分模式下使用DC/DC稳压器进行相同的测量,则总噪声会降低,LDO和DC/DC性能之间的差异很小。图1显示了以伏特而不是最低有效位(LSB)为单位的性能,垂直轴转换为伏特,因为差分的LSB是单端的两倍,以考虑对有符号结果(负电压)的支持。差分测量中的方差小于单端实现中方差的一半,表明ADC将来自DC/DC的大部分噪声视为共模噪声。

被测直流电压被视为差分输入,其中Vss是ADC的负输入。因此,即使信号本身是单端信号,在差分模式下进行测量也能降低噪声,而且在使用DC/DC稳压器时还可以降低噪声。这是一个非常好的消息,使工程师能够利用DC/DC的优势,同时消除相关的噪声。

来自内部稳压器的噪声只是一种可能的噪声源。其他可能的噪声源可以是相邻的数字信号,例如I2C 或串行外设接口 (SPI) 通信,或脉宽调制 (PWM) 波形。我们建议使这些信号尽可能远离ADC引脚,如果可能的话,在ADC测量期间保持非活动状态。大多数IC制造商通过创建专用模拟引脚,有意使数字信号远离模拟。然而,在较小的封装中,某些数字功能可能与模拟引脚多路复用,或者数字输入/输出(I/O)引脚可能与模拟引脚相邻。

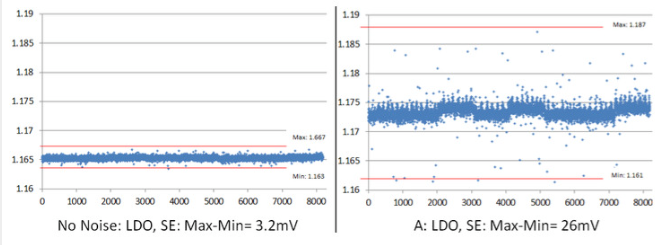

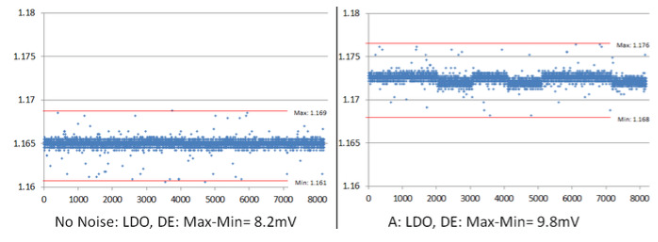

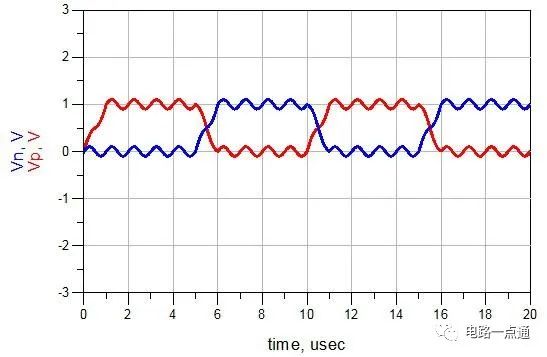

作为实验,让我们将DUT模拟输入紧邻48MHz时钟输出(全轨到轨摆幅)定位,以表示数字噪声源。如图2和图3所示,与差分相比,单端测量增加相邻时钟输出时噪声增加幅度更大。在单端情况下,测量的电压连接到模拟输入。差分模式下的互补输入保留在通用I/O (GPIO)模式下,并主动驱动低电平,即器件的数字源电源电压(DVSS)。在差分情况下,互补输入从外部连接到器件的模拟源电源电压(AVSS)。

虽然与单端示例相比很小,但差分结果表明噪声仍然存在。目视检查显示,与差分对的正极和负极之间的分离相比,时钟相对接近差分测量的正极。因此,相对耦合将不相等,噪声也不会完全显示为共模。

该实验是在四层PCB上进行的,第三层提供几乎完全坚固的接地层,因此返回电流可以直接跟随走线下方。第二层提供基准电压,并分为多个位置,使信号和接地层返回路径之间的耦合复杂化,并可能产生噪声介质以影响测量,这可能进一步解释噪声的存在

图 2:从相邻时钟感应到单端 ADC 输入的串扰 A 与无噪声的关系

图 3:从相邻时钟感应到差分 ADC 输入的串扰 A 与无噪声的关系

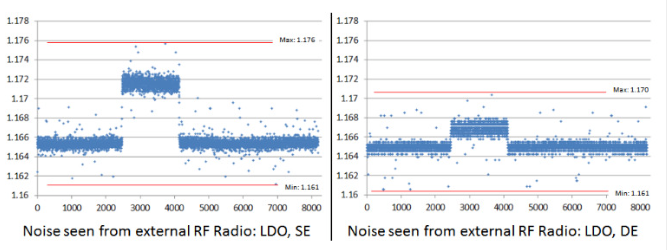

在最后一个实验中,一个以50kB(868MHz,2GFSK,2kHz偏差)传输100个随机数据包的评估模块引入了无线电信号。EVM 放置在 DUT 附近,因此 MCU(和 ADC)距离 EVM 的 PCB 天线约 6 厘米。图4再次显示,差分配置的抗扰度优于单端。关键是能量均匀耦合在差分ADC的正输入和负输入上,因此信号作为共模被抑制理想情况下,在图4所示的差分测量中不会看到噪声,因此这种偏离预期值得讨论的潜在原因。

图4:附近无线电信号引起的噪声

时钟和Sub-1 GHz无线电实验之间最显着的区别是相对耦合面积。就时钟而言,耦合区域与时钟走线与ADC输入线平行的位置最相关。在这种并行运行之后,信号发散:ADC信号脱离板外到电压源进行测量,而时钟终止于另一个接收输入。

正是具有最小屏蔽的板外连接为无线电能量耦合到ADC提供了一种潜在的方式。此外,ADC正输入和负输入之间的任何电气长度差异都可能导致耦合噪声为差分噪声,而不是共模噪声。最小化ADC正输入和负输入之间电气长度差异的一种有效方法是设计对称的信号路径。

本节中的测试旨在显示差分信号提供的改进范围。改进发生在应用程序或实现级别。来自邻近无线电的干扰也适用于需要电磁兼容性 (EMC) 的蓝牙和 Wi-Fi 应用。在电路板层面也有明显的改进,来自相邻数字信号的交叉耦合(串扰)。最后,在IC级甚至可以看到改进,选择噪声稳压器可以实现低功耗操作,并减轻ADC性能的下降。

虽然差分信号是实现数据手册中ADC性能的宝贵工具,但了解数据手册参数必须是优先事项。MCU中有许多与ADC性能相关的配置和依赖关系,这使得理解数据手册性能与应用要求相关的困难。

本系列讨论了一些主要的性能依赖性,并提供了一些趋势,以帮助揭开MCU数据手册和集成ADC性能的神秘面纱。有了这种理解,开发人员可以为传感器应用做出更明智的MCU选择,并实现完全实现集成ADC性能的设计。

审核编辑:郭婷

-

ldo

+关注

关注

35文章

1925浏览量

153261 -

adc

+关注

关注

98文章

6469浏览量

544297 -

无线电

+关注

关注

59文章

2137浏览量

116390 -

差分信号

+关注

关注

3文章

367浏览量

27674

发布评论请先 登录

相关推荐

介绍差分信号的优势

介绍差分信号的优势

评论