引言

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA威廉希尔官方网站 交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:快速实现基于FPGA的脉动FIR滤波器,VHDL,脉动阵列,PE处理单元,FIR滤波器

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1628文章

21711浏览量

602752

原文标题:快速实现基于FPGA的脉动FIR滤波器,VHDL,脉动阵列,PE处理单元,FIR滤波器

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何区分IIR滤波器和FIR滤波器

IIR(无限脉冲响应)滤波器和FIR(有限脉冲响应)滤波器是数字信号处理领域中两种非常重要的滤波器类型。它们在许多应用中都发挥着关键作用,如

iir滤波器和fir滤波器的优势和特点

IIR滤波器和FIR滤波器是数字信号处理领域中两种非常重要的滤波器类型。它们各自具有独特的优势和特点,适用于不同的应用场景。本文将介绍IIR

基于matlab FPGA verilog的FIR滤波器设计

今天和大侠简单聊一聊基于matlab FPGA verilog的FIR滤波器设计,话不多说,上货。

本次设计实现8阶滤波器,9个系数

发表于 07-04 20:11

matlab与FPGA数字信号处理系列 Verilog 实现并行 FIR 滤波器

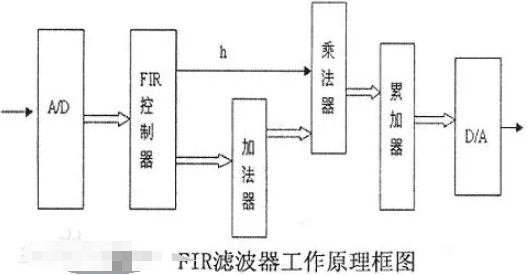

在 FPGA 实现 FIR 滤波器时,最常用的是直接型结构,简单方便,在实现直接型结构时,可以选择串行结构/并行结构/分布式结构。

并行结构

发表于 05-24 07:48

DSP教学实验箱_DSP算法实验_嵌入式教程:4-3 有限冲激响应滤波器(FIR)算法(CCS显示)

一、实验目的

了解FIR滤波器的特点,掌握程序算法生成滤波器系数的方法,并实现FIR滤波器滤除高

发表于 05-16 09:30

Vivado 使用Simulink设计FIR滤波器

型滤波器,是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应是有限长的,因而滤波器是稳定的系统。因此,FIR

发表于 04-17 17:29

基于多速率DA的根升余弦滤波器的FPGA实现

处理威廉希尔官方网站

和分布式算法的FPGA实现威廉希尔官方网站

,使得计算量大幅减少,处理速度得到较大提高,而且使得FPGA资源利用更合理。1、根升余弦

发表于 03-25 14:21

Vivado经典案例:使用Simulink设计FIR滤波器

FIR(Finite Impulse Response)滤波器:有限长单位冲激响应滤波器,又称为非递归型滤波器,是数字信号处理系统中最基本的

AD6620的FIR滤波器是什么类型的滤波器呢?

请问AD6620的FIR滤波器是什么类型的滤波器呢?它的功能是什么呢?可不可以直接从AD6620的输出中进行符号同步的时钟提取呢?谢谢!!!

发表于 12-22 07:00

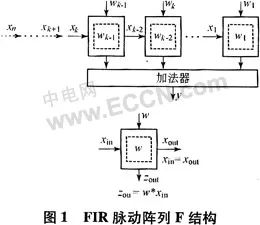

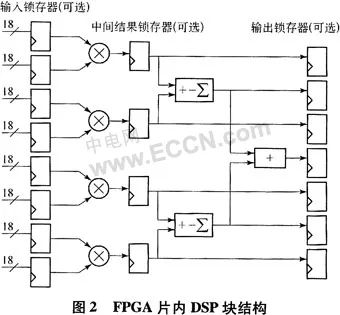

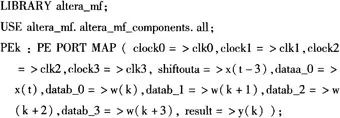

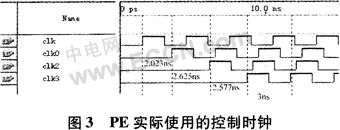

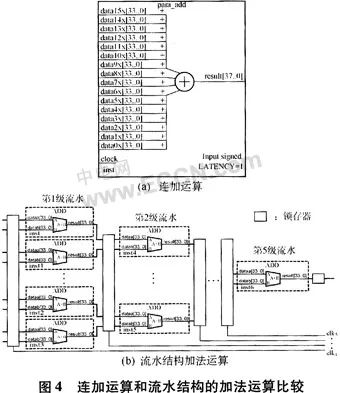

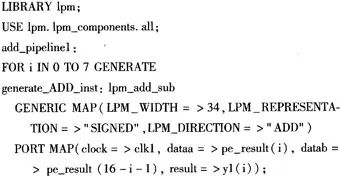

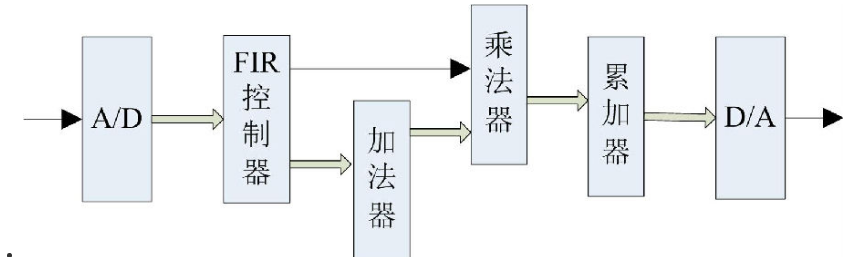

快速实现基于FPGA的脉动FIR滤波器,VHDL,脉动阵列,PE处理单元,FIR滤波器

快速实现基于FPGA的脉动FIR滤波器,VHDL,脉动阵列,PE处理单元,FIR滤波器

评论