在航空电子设备中,将软件集中到一个硬件平台中被认为是一种很好的做法。事实上的标准 ARINC653 根据排除和缓解硬件资源冲突的分区模型描述了它如何正常工作。随着此模型的成功和多核处理器 (MCP) 的出现越来越多,证书颁发机构已开始扩大其对使用多核处理器的接受程度。

CAST-32 方法为多核处理器打开了大门。..

关于这一点,认证机构软件小组(CAST),一个由认证和监管机构代表组成的国际小组(EASA,FAA),发表了一篇名为CAST-32的论文,描述了允许在机载系统中使用多核处理器的条件。从本质上讲,本文确定了可能对系统安全产生影响的主要主题,在大多数情况下,事实证明确定性是关键。CAST-32的最终结论是可以使用多核处理器,但范围仅限于最多两个活动内核。

。..但随后的开发实际上允许有效地利用它们

随着CAST-32文件CAST-32A(2016)的更新,这种情况发生了变化。现在可以在机载系统中并行使用处理器的所有内核。该文件明确允许使用多个内核,只要提交认证的组织(申请人)可以为上述问题提供最先进的解决方案。这些问题涉及硬件设计的各个方面以及软件体系结构的问题。后者需要通过适当的操作系统打下坚实的基础。高级操作系统已经将多核支持紧密地整合到其分区管理中。

规划的挑战

CAST-32A 定位文件的“规划”部分讨论了与处理器、架构、操作系统和工具选择相关的所有主题。它始于申请人确定MCP的责任。此外,CAST-32A要求申请人注意软件架构(包括IMA考虑),资源分区模型和要使用的开发工具。

最大的挑战:管理共享处理器缓存而不发生冲突

CAST-32A最具争议的讨论主题被称为“干扰信道和资源使用”。它让申请人来识别应用程序之间的干扰,定义资源使用情况,并评估对整个系统的确定性行为的影响。共享处理器缓存和主内存带宽的影响这两个问题正在挑战申请人构建系统。

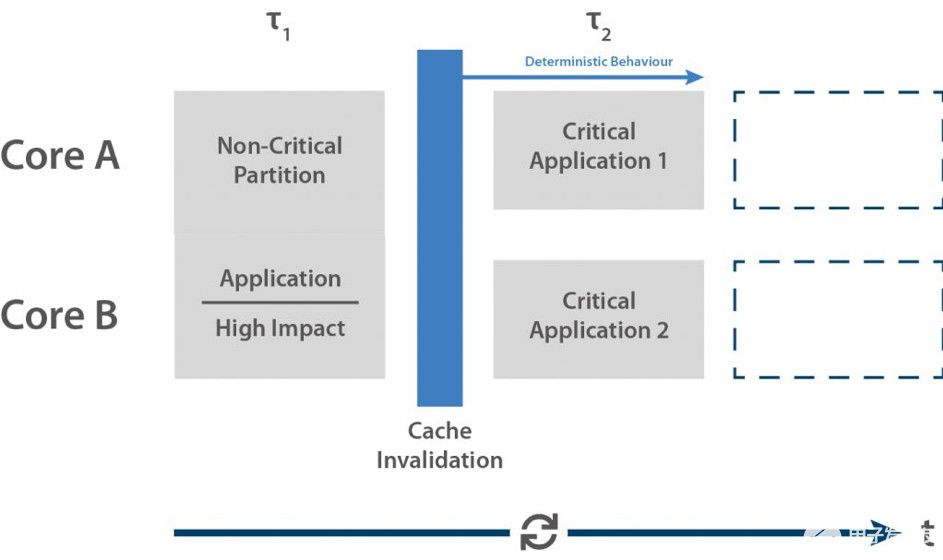

由于高级缓存在处理器内核之间共享,因此 CPU 的硬件必须处理同步问题。此外,共享缓存的状态可能会受到错误应用程序的影响,从而严重影响安全关键分区的性能。

及时处理任务的内存冲突解决方案

为了应对最坏的情况,符合 CAST-32A 标准的操作系统必须提供缓存带宽监控,以便关闭错误的应用程序。除了这些在运行时适用的威廉希尔官方网站 方法之外,申请人应该有可能(几乎)消除架构级别的缓存影响。最明显的方法是增加时间分区窗口的安全裕度,以便即使共享缓存永久不稳定,也可以满足最坏情况执行时间 (WCET)。这样做时,性能将受到重大影响。相反,申请人可以将应用程序分成具有相同软件级别的组。通过确保安全关键流程并行运行,缓存可以在关键时间范围开始时失效。这应该类似于单核处理器上的情况,其中应用程序按顺序调度,在关键安全应用程序启动时执行资源清理。

另一个干扰源是主内存总线。即使内存区域被划分并因此相互保护,对总线的访问也需要一定的时间。一个应用程序对内存总线的密集使用是以并行运行的应用程序为代价的。本主题与共享缓存讨论非常相似,缓解措施几乎相同。

细粒度锁定和清晰的前景

当在不同内核上执行的应用程序同时进入内核空间时,也可能发生争用,从而可能访问相同的数据结构。传统上,对整个内核内存的访问受全局锁保护,一次只允许一个内核执行操作系统服务。这在威廉希尔官方网站 上可能已经足够,但在可扩展性方面并不令人满意。为了减少这种干扰通道的影响,一个兼容良好的操作系统必须使用细粒度锁定,这大大降低了应用程序同时请求同一锁的概率。

除了识别干扰信道外,CAST-32A论文还要求对每个内核的资源使用情况进行分析。例如,申请人仍然需要在合理条件下确定安全任务的WCET,并且最终必须确定安全裕度。这同样适用于存储区域大小的分析。一个好的操作系统必须通过提供有关内存预算和执行时间的信息来支持用户。

总结

证书颁发机构团队 (CAST) 小组勾勒出在航空电子系统中使用多个处理器内核的方法。他们的定位文件CAST-32A提到了硬件设计的各个方面以及软件架构的问题。通过PikeOS操作系统,SYSGO公司提供了主要的构建块之一,将强大的资源和时间分区扩展到具有多个内核的CPU,完美地应用了CAST-32A论文中描述的需求。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19281浏览量

229789 -

航空电子

+关注

关注

15文章

490浏览量

45226

发布评论请先 登录

相关推荐

盛显科技:拼接处理器连接大屏方法是什么?

TMS320C6674多核固定和浮点数字信号处理器数据表

TMS320C6672多核固定和浮点数字信号处理器数据表

TMS320C6678多核固定和浮点数字信号处理器数据表

SM320C6678-HIREL多核固定和浮点数字信号处理器数据表

嵌入式微处理器有哪些部分 嵌入式微处理器有哪些区别

嵌入式微处理器体系结构有几种 嵌入式微处理器分为哪几种类型

主流嵌入式微处理器的结构与原理是什么 常见的嵌入式微处理器类型包括

多核异构通信框架(RPMsg-Lite)

用于多核处理器的可配置多轨PMU TPS650860数据表

CAST-32方法为多核处理器打开了大门

CAST-32方法为多核处理器打开了大门

评论