一、

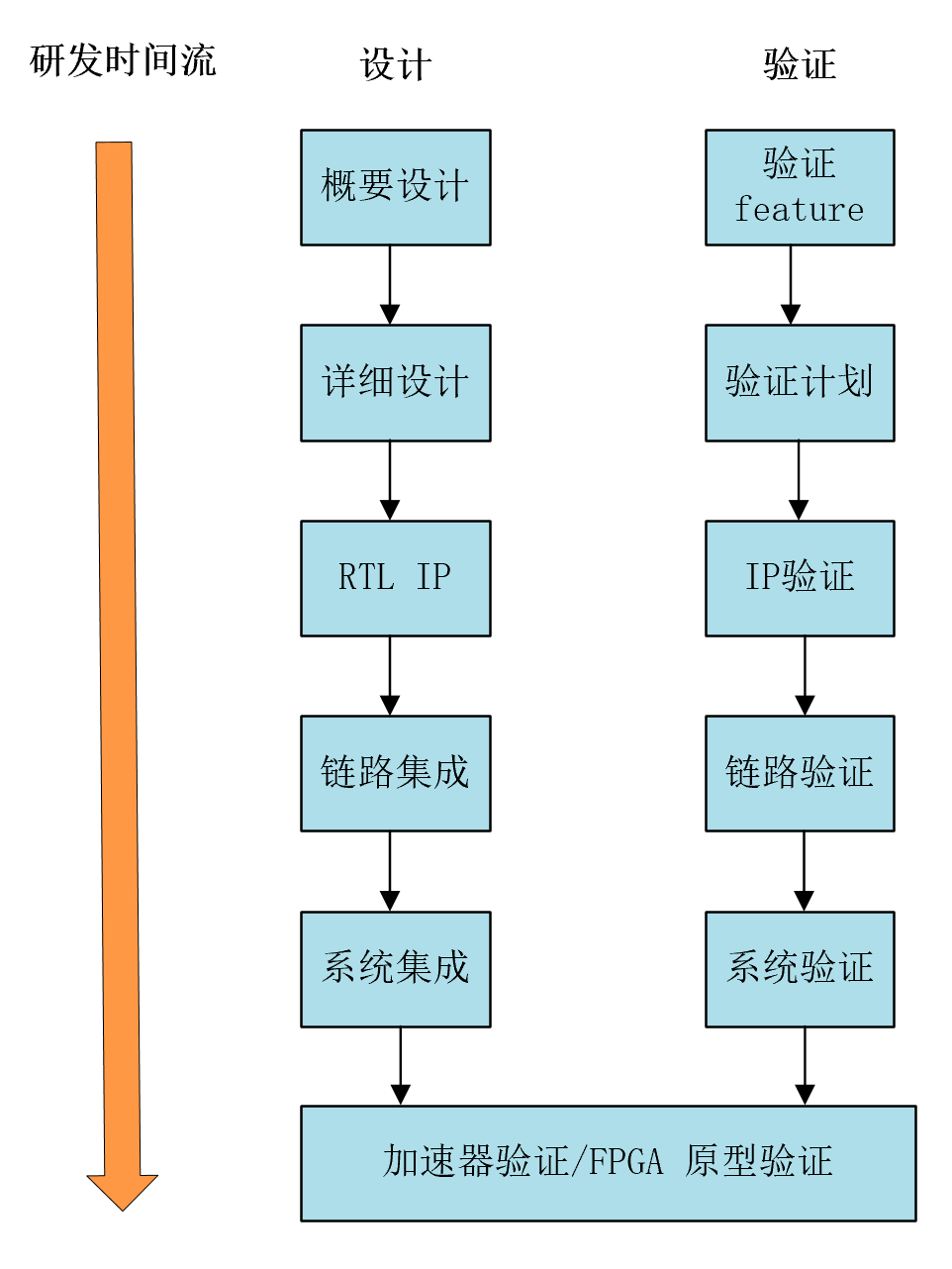

经典的设计与验证流程

可以看到设计与验证永远是同步节奏,即使因为一些客观原因,导致验证稍微慢于设计节奏,最终也会回到同步的节奏上。

这样的理想状态就对设计工程师有一定要求,比如拿到设计需求,就然后开始概要设计文档,其中就包括整体的模块对外接口,关键时序,整体的架构设计等。验证工程师拿到概要设计,就可以开始进行验证feature规划。

详细设计文档,设计要完成整体的模块的控制流,数据流、memory需求规格,状态机,关键电路,关键时序设计等。验证拿到详细设计文档,就可以进行验证case规划,验证计划文档编写。

理想的状态下设计拿着自己的详细设计文档就可以直接行云流水式的写代码。写代码真体力活。而这段时间验证就可以进行验证平台搭建和验证case设计。

设计代码写完,编译通过,lint清除,将一些低级错误扼杀在摇篮里。验证平台也搭建好,设计与验证对接,一起调试第一条case。第一条case通过,环境OK,代码OK。开始循序渐进debug。

验证验出bug,提给设计,设计修改,上传版本管理库,验证up,进行回归。完全正确,调试下一条case。

IP验证到一定feature成熟,释放一个版本给链路验证同事,验证多个IP配合的场景和当前版本成熟的feature,很少会出现在链路上验出IP级的bug(当然也有)。

链路验证到一定feature成熟阶段,释放版本给系统验证同事,验证多个链路配合场景和当前版本的成熟feature。系统验证成熟到一定feature。然后再上硬件加速器验证和FPGA原型验证。

整个理想的过程,一气呵成,在系统验证和加速器/FPGA原型验证上,会比较顺利,不会因为模块级的bug卡住验证进度,因为在大系统里面调试效率非常低,基本就只剩过case。

理想很丰满,现实很骨感。

现实情况是

设计人员写完代码才写文档,导致验证迟迟没有设计文档,无法开始验证计划和验证环境搭建。最终整体项目时间delay1-2个月。

设计人员不写文档,直接写代码,边写边想,设计架构没有经过评审,和上下游交互接口和时序都对不上,代码写完也是要修改重新写,最终整体项目delay1-2个月。

项目delay了,设计着急了,在IP验证尚未完全时就开始链路验证,系统验证。出现问题,debug效率低下,一天发现一个低级错误,链路验证和系统验证仿真时间长。你为什么总在加班?

设计着急了,在链路验证和系统验证尚未完全时,就开始加速器/FPGA原型验证,编译一个版本要一天,效率更低下。你为什么总在加班?

最终,项目还是delay,所有人也还是要加班完成。所以做芯片是有章法可循,业界多少年总结出来的血泪经验,不遵守是要吃亏的。

设计工程师与验证工程师是好朋友

设计工程师和验证工程师是永远的好朋友,你们是共同在完成一个工程,产品,砖。验证的case和验证完备性是要两个人共同的努力的成果。

有一个验证,发现一个case fail了,打电话给设计,case xxx fail了,看下什么原因。设计跑出来看了下,回个电话,是你平台的原因,修改下,case pass了。设计与验证是好朋友。

有一个验证,发现一个case fail了,打电话给设计,case跑一次贼慢 ,波形我已经跑好了,直接在我们的共享窗口上看下吧,设计看出了问题,本地修改了下,回个电话,我上传了,你up下再跑一下。晚上下班前回归下case。设计与验证是好朋友。

又有一个验证,因为一些个人原因,验证平台没有及时搭建起来,delay与设计,但设计代码已经写完了,没有平台和case验,跑到验证办公位后面,站在身后监工,没你平台,我可搞不了。设计与验证是好朋友。

还有一个验证,没有发现任何bug,设计打电话说,我改了一行代码,没有任何影响,就是代码风格变了下,这样写覆盖率更好收,占用资源更小。我要提个问题单记录一下,这造成了我回归的工作量。设计与验证是好朋友。

突然有一个设计,代码迟迟不愿意给验证,说我代码bug太多了,我要自己先验下,验证没法开展工作,然后过了一阵子,找验证说,我过了一百多条冒烟case。拿去给你验吧。验证:你这代码给我都八时了,等着项目delay吧。设计与验证是好朋友。

流程死的,人是活的

并不是所有的设计都要走繁重的流程,我做了个xxx设计,先进行概要设计评审,详细设计评审,代码review,验证feature评审,验证计划评审,验证环境搭建,最后规划了10个case,覆盖率达到100%。这么个破玩意儿,两个人整两个月的时间。

有设计说,就这,那我还不如自己验,你给我搭个平台,我自己跑case,收覆盖率,上FPGA原型验证。两周搞定。流程是死的,人是活的。但你需要分清什么情况下怎么做才是对的。

审核编辑 :李倩

-

工程师

+关注

关注

59文章

1570浏览量

68516 -

架构设计

+关注

关注

0文章

31浏览量

6924

原文标题:设计工程师与验证工程师如何合作?

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

芯华章发布FPGA验证系统新品HuaProP3

【「数字IC设计入门」阅读体验】+ 数字IC设计流程

ALVA Systems 创新 AI/AR 威廉希尔官方网站 实现检修设备作业流程高效验证

芯华章生态战略亮相DAC,发布全流程敏捷验证管理器FusionFlex,并联合华大九天推出数模混合仿真解决方案

芯华章为产业提供覆盖RISC-V全流程的验证方案

大规模 SoC 原型验证面临哪些威廉希尔官方网站 挑战?

电源功率模组: 完整的设计和验证流程解决四个维度的设计挑战

E-Val Pro Plus有线验证解决方案,功能升级,优化制药流程,确保安全性和合规性!

fpga原型验证流程

珠海南方集成电路设计服务中心引进芯华章全流程验证工具

虹科方案丨冻干机全面验证和监测解决方案

经典的设计与验证流程

经典的设计与验证流程

评论