半导体各领域的发展难度与日俱增,验证可能是整个发展过程中最具挑战性的阶段。多年来,研究显示在验证上投入的时间和资源所占的百分比会随着新时代芯片的出现而增加。因此整体上,验证的快速成长超过芯片开发和芯片制造中的其他阶段。电子设计自动化(EDA)产业将人工智能(AI)的力量应用到验证过程的各个步骤,以应对这样的情况。

三大验证关键挑战

芯片验证工具、过程或方法,常常和快速找到更多程序错误画上等号。然而,实际验证上所考虑的因素其实更加广泛。验证工程师主要关心下列三个层面:结果的质量(QOR)、达成结果所需的时间(TTR),以及达成结果所需的成本(COR)。

QOR不难理解,验证团队会希望能找到所有的程序错误。找出的程序错误数量十分重要,但程序错误的类型和复杂度也同样关键。如果因为一些没发现的程序错误而造成系统宕机或芯片故障,那么即使找到99.9%的程序错误也只是徒劳。目前没有方法能准确知道什么时候能找到所有程序错误,不过,已有一些方法能帮助验证团队决定何时能宣告成功并将芯片投片量产。在interwetten与威廉的赔率体系 方面,功能性和结构性的覆盖方法(Coverage Metrics)最为常见。达到高度覆盖能在设计的正确性上建立信心,而未能覆盖的部分则能作为良好准则,告诉团队还需要进行的额外测试。在静态和形式(Formal)分析方面,检查和验证的电路特性百分比是主要的数据,而未能百分之百验证的特性则可当作分析深度的有界验证(Bounded Proof)信息。

基于许多原因,TTR也极具重要性。每个芯片计划都有一个目标出货日期,而这日期取决于市场机会和竞争压力。相关人员将依照该日期规划时程,但是如果接近收敛的时间来得比预期还慢,投片量产以及接下来的产品出货时间都会因此产生延迟。这不仅会造成利润损失,在最坏的情况下,还会让芯片在出货前就失去竞争力。因此,验证工具需要能够快速进行测试和分析,并具备平稳的收敛过程及迅速的除错功能,才有办法赶上紧迫的时程。若时程落后,一般的应对措施是扩编验证团队。然而,在一个工程计划中增加更多人员并不一定会减少完工所需的时间。

资源也包含在COR的三个层面内。增加更多工程师不仅会增加计划成本并减少终端产品的潜在利润,取得更多运算服务器或是租借云端服务器也都会增加成本。此外,每次启动额外的模拟或是形式验证都会产生更多需要分析的结果。如果这些额外的验证测试相较于既有测试是多余的话,这些增加的非必要调试时间可能反而降低验证效率。最后,每次芯片re-spin都会在预算中增加一笔可观的COR并造成TTR延迟,所以高QOR非常关键(图1)。

图1 QOR、TTR、COR三层面重点

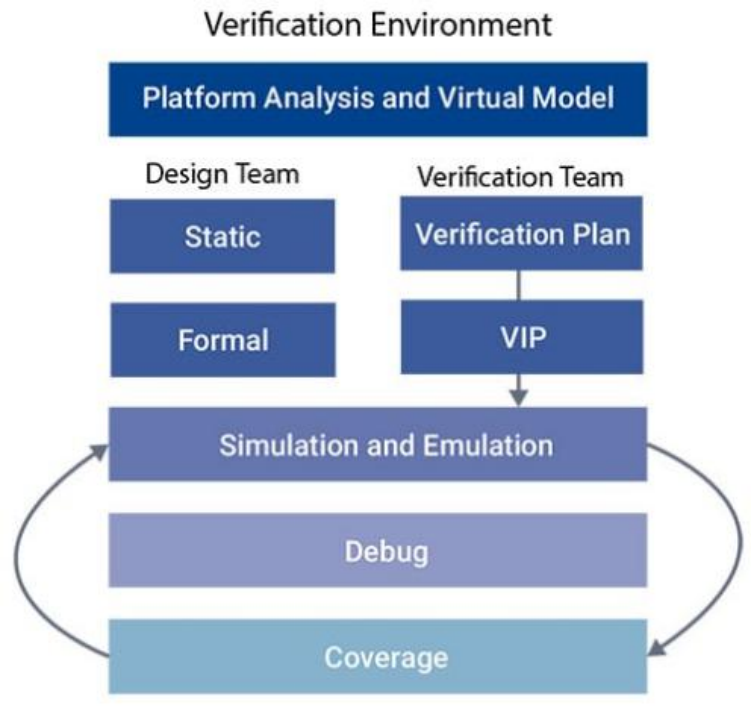

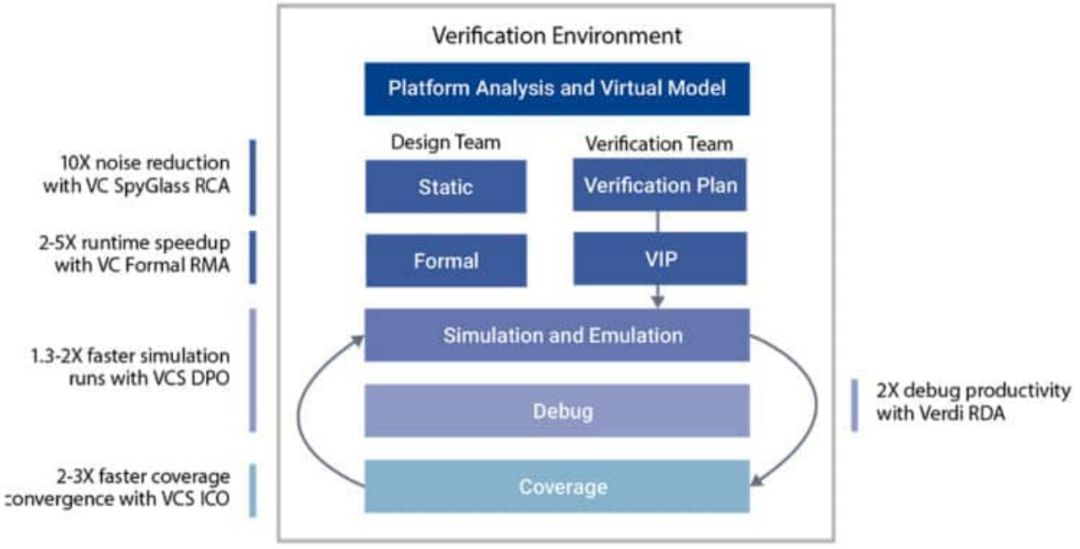

AI威廉希尔官方网站 多数皆以机器学习(ML)为基础,可以大幅度改善芯片验证的三个层面。图2显示典型验证流程。在设计者将RTL编程写入之前,架构团队就会建立一个芯片的虚拟模型并分析系统效能。

当关键决定下达时,设计团队就会开发RTL模型; 这些过程最好能通过整合开发环境(IDE)完成,并搭配强大的代码检测工具(Language Linting)以捕获其他会消耗时间和资源的编码错误,并在计划后期修复。标记的错误修复后,通常会由设计者来执行验证的第一步,也就是启动静态验证工具来侦测设计中的结构错误。形式验证(Formal Verification)工具则能提供更深入的分析,尝试证明关于RTL设计的关键性质。

这些工具也可能由设计者启动,尽管熟悉formal的专家也可能参与其中。同时,验证团队开发出能执行一系列测试的测试平台(Testbench)和模型来达成验证计划的目标,这通常会运用到现有的验证IP(VIP)。

这些测试主要通过模拟来完成,不过近几年硬件仿真平台的使用也越来越普遍。如前述,覆盖方法是判断验证进度的主要方法,而覆盖收敛(Coverage Closure)则是高度迭代的过程,通常是验证时程中耗时最久的一部分。

图2 验证流程概略

AI威廉希尔官方网站 在静态验证的应用

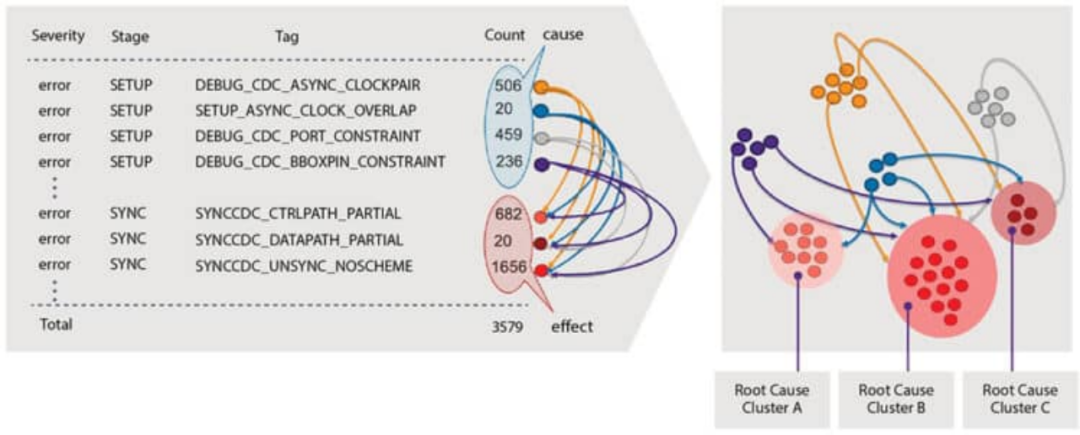

随着静态验证可提供的检查类型增加,在芯片验证中的重要性也越来越高。当代的静态解决方案包含针对跨时脉域(Clock Domain Crossing, CDC)、跨重置域(Reset Domain Crossing, RDC)以及低功率设计结构的精密检查。透过这样丰富的分析阵列,以一个典型计划中能发现的所有程序错误而言,其中大约10%会在这个阶段就被侦测到并修复。静态工具的主要问题在于它们通常会回报好几千个潜在的违规,很容易造成干扰。其中有些可藉由微调输入设定来解决,如选取哪种违规回报为错误、哪种违规仅是警告。发生干扰的主要原因是单一底层设计(Underlying Design)的缺失所导致的相关违规。例如,频率逻辑中的程序错误可能会导致使用该时钟的任一正反器(Flip-flop)产生违规回报。就除错效率而言,设计者必须专注在特殊的问题上,一旦这些问题获得解决,便能消除多数违规。

根本原因分析(Root-cause Analysis, RCA)就是一款能达到上述要求的AI赋能威廉希尔官方网站 。如图3所示,各个击破过程中的第一步就是使用机器学习方法并根据共同特征进行违规丛集。在刚刚提到的范例中,所有与时脉逻辑程序错误相关的违规都会整合成单一丛集,其目的为让设计者将每个丛集视为一种违规并进行修复,如此便可修正丛集中的所有违规。数以千计的违规通常会减少至几十个丛集,这样能节省设计者大量的时间和精力。丛集法使用的是非监督式的机器学习算法,因此可以在没有用户引导下自行运作。它能识别违规的因果关系、随着计划进度学习,并执行RCA,进而减少计划团队的负担。此外,其具有的图像显示和现成可用的Tcl指令文件能引导设计者找到每一个丛集中违规的根本原因。

图3 静态分析中的违规丛集

新思科技的静态验证解决方案VC SpyGlass平台,以及其全面性静态低功率的验证解决方案VC LP,能提供包括前述甚至更多的功能。SmartGroup威廉希尔官方网站 能执行先进的丛集法来大幅减少待检验的违规数量,而RCA可加速每个丛集的除错速度。针对违规提出的建议修正可能是对RTL的设计进行改变,不过通常是细微的区别或添加设计限制文件(Constraints File)。基于机器学习的群集法和RCA的组合能在一般典型芯片计划中提供10倍的调试效率并改善静态验证。

AI威廉希尔官方网站 在形式验证的应用

虽然以测试平台为基础的模拟为人熟知并且广泛应用在验证威廉希尔官方网站 上,但还是有其限制。除非模拟刺激(Simulation Stimulus)触发程序错误并以可观察到的方式改变预期结果,设计上的程序错误便无法被侦测到并进一步修复。因此,总是有某些程序错误会被遗漏。形式验证提供针对一组属性的设计综合分析,不需要stimulus; 该分析会考虑每一个可能的合法输入序列,可以侦测到在模拟中难以被激发的深层程序错误,这通常占所有程序错误中的20%。形式验证还可以证明在给定的电路特性(Property)不存在更多的错误,为模拟或仿真提供很高的可信度。

形式验证工具通常在幕后有好几十个解算装置(Solver)或引擎来处理好几百或好几千个在设计上需要验证的电路特性。它能处理的形式验证工具效能和设计尺寸皆取决于引擎效能和引擎的编排。在过去20年里,formal的威廉希尔官方网站 已经进步许多。最近,AI和机器学习威廉希尔官方网站 的采用大大改善收敛性和效能。

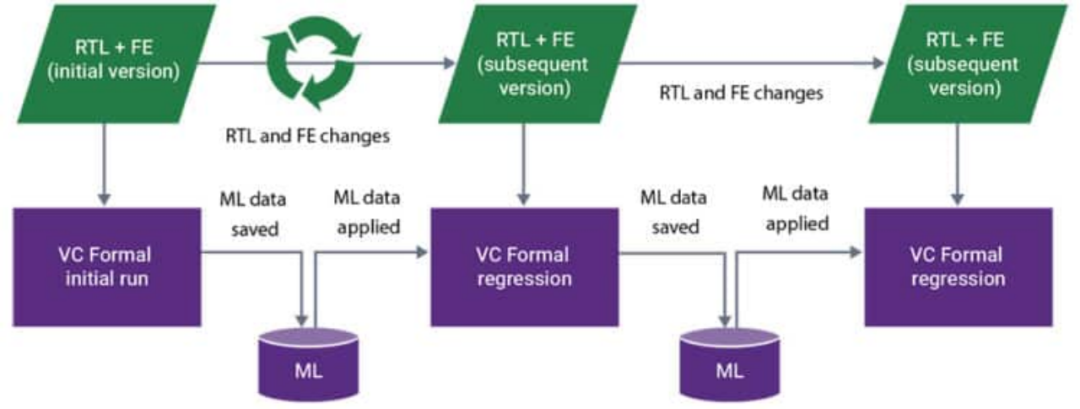

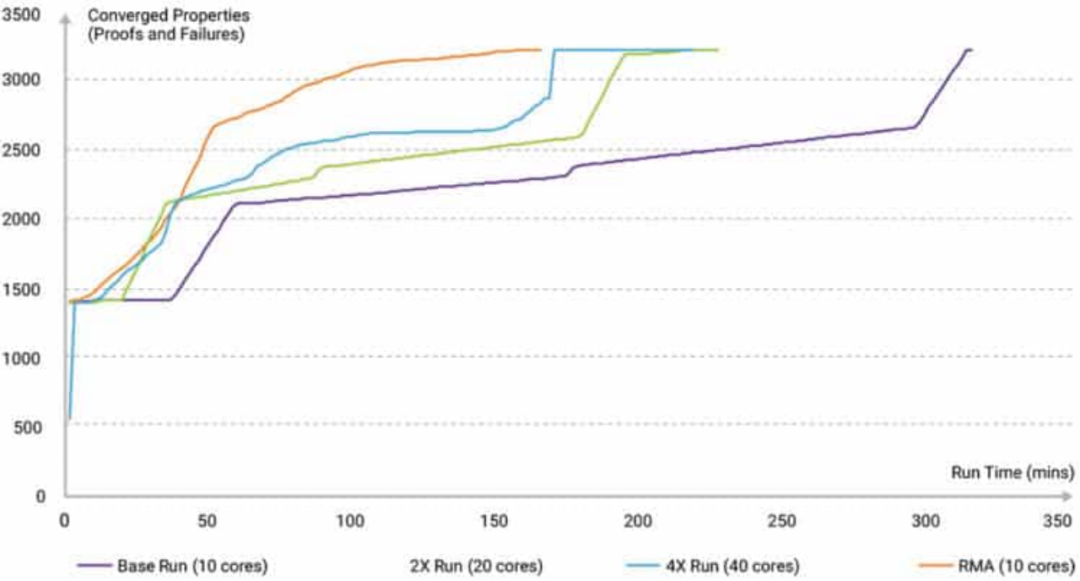

新思科技VC Formal是业界第一款形式验证工具,并将机器学习应用在引擎编排、回归和除错程序。引擎编排的目的是在实际运算资源和时间的限制下,指派正确的引擎到正确的电路特性上,以达到最短的运作时间和最佳的收敛演算。VC Formal在处理每一个电路特性时,都会使用实时加强学习,从有效和无效的方法中学习,并在下一组动作中指导编排,这称为智能策略选择(Smart Strategy Selection)。除此之外,针对每一个电路特性下达的决定都会在执行结束时储存在数据库中,后续的执行可以运用前次执行的学习成果,找出更好的结果,这称为回归模式加速器(Regression Mode Accelerator, RMA)。当RTL设计或形式测试平台在设计和验证的过程中需要修正时,形式验证通常会在每晚或是每周的回归过程中执行,以确保这些改变在设计上不会产生新的程序错误。

如图4所示,每次接续的VC Formal执行都会读取前一次执行的设计内容和学习数据库来决定可安全维持的电路特性状态,并决定哪些电路特性因为这些改变而需要重新执行、哪些不能判定的电路特性应该需要更多时间和编排资源。即使是那些需要重新验证的电路特性,前次执行中的学习也会指导编排过程并使第二次执行更快速。比较基准(Benchmark)的数据显示这些机器学习威廉希尔官方网站 可以提升10倍以上的验证速度和额外的收敛能力,并减少TTR和COR,同时还能改善QOR。图5以一项真实设计作为范例来说明这些好处。

图4 VC Formal中的回归模式加速

图5 RMA加速电路特性收敛

AI威廉希尔官方网站 在模拟的应用

运作时间性能对模拟回归也至关重要,这可能包含数以千计的测试并通过执行来验证所有在RTL设计和测试平台上的编程改变。模拟会保留在芯片验证的核心部位,约占所有已发现程序错误的65%。有时候为了修复程序错误而在设计上做的改变不仅无法正常运作,甚至还会引发新问题。因此,频繁进行回归程序来快速侦测问题是确保计划按部就班进行的关键。影响模拟和回归效能的因素中,至少有两项与AI相关的改善有关。

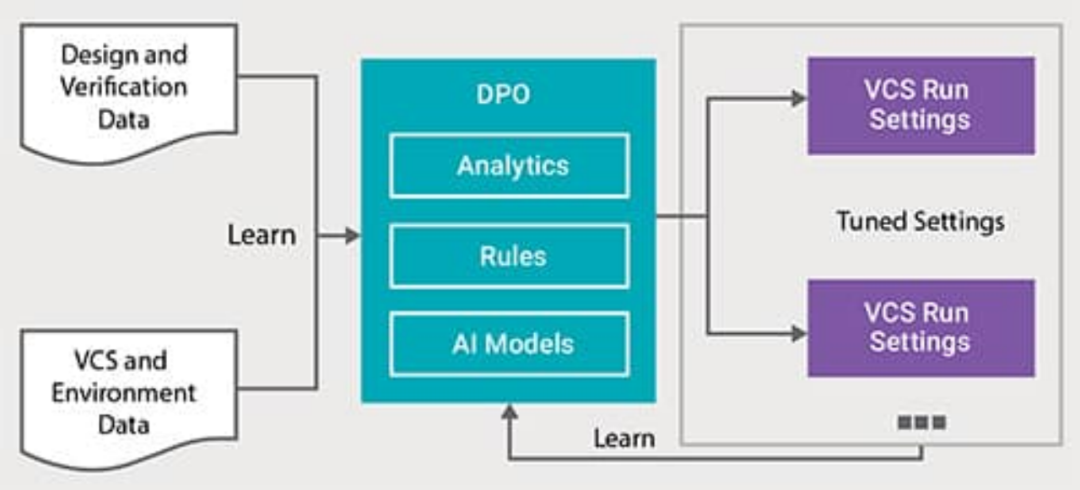

第一项因素为模拟和回归执行的设定。当代模拟器具有许多选项和开关,对效能有着重大影响,验证工程师需要时间和专业知识来为特殊的设计和测试平台进行模拟器的设定优化。随着程序演化,可能会需要对设定做一些调整来维持最佳效能。使用机器学习威廉希尔官方网站 来学习和维持模拟器选项和开关的自动化过程,可以改善回归效能和效率。新思科技VCS模拟器中的动态性能优化(Dynamic Performance Optimization, DPO)威廉希尔官方网站 是AI在模拟性能上的一种应用。它利用机器学习和以规则为基础的AI威廉希尔官方网站 ,从前几次的回归执行中学习并自动调整VCS设定来优化效能,如图6所示。该过程是自动的,所以不需要用户输入。不过,若验证工程师有相关需要,还是可以控制该流程的某些面向。例如,他们可以只在某几天打开学习模式,并在期间内使用相同设定执行回归。相较于采用模拟器设定的手动验证,DPO大致上可提供快上1.3~2倍的模拟执行。

图6 VCS中的动态效能优化

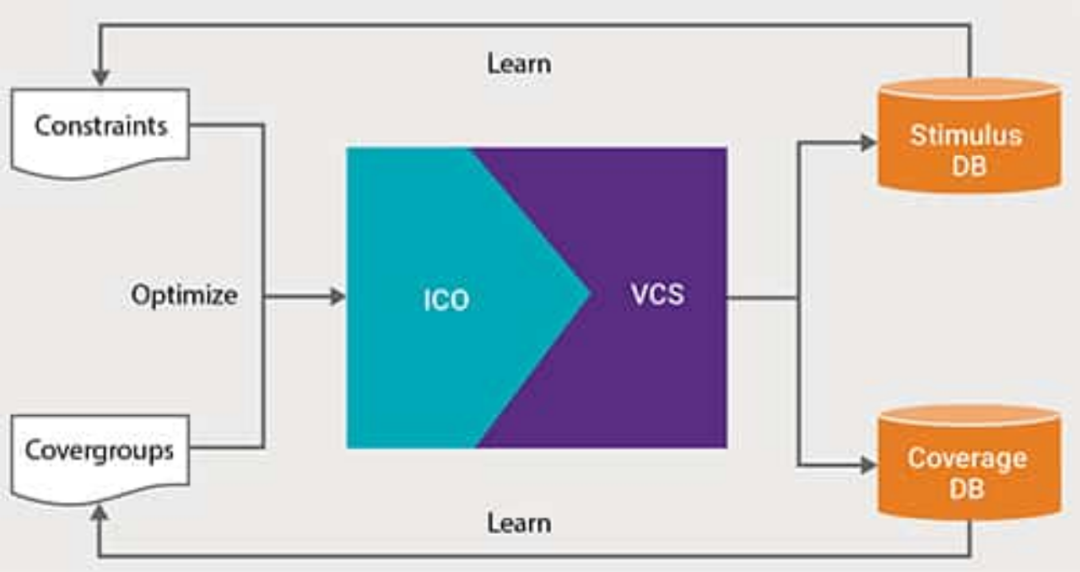

在整体回归效能中受影响最大的部分是收敛所需的时间。以往验证工程师会检查模拟报告来判定未达到的覆盖部分,接着变更测试或编写新的测试来尝试覆盖设计上错失的部分。藉由随机限制(Constrained-random)的测试平台,他们更有可能修改测试平台的限制,将产生的自动stimulus聚焦在遗漏的覆盖范围上,但是这还是需要相当大的人力,并将浪费相当多的时间复制已覆盖的范围。改善这种状况是验证过程中另一种AI与机器学习的应用,而VCS也提供了一套解决方案。智能覆盖优化(Intelligent Coverage Optimization, ICO)能优化随机限制stimulus的统计质量并对影响覆盖范围的测试问题提出见解(图7)。在最近的芯片计划中,ICO已经证明能以2~3倍的速度加速收敛覆盖范围。验证团队可以在更短的时间内达到更大的整体覆盖范围,缩短时程并节省资源。

图7 VCS中的智慧覆盖优化

AI威廉希尔官方网站 在调试的应用

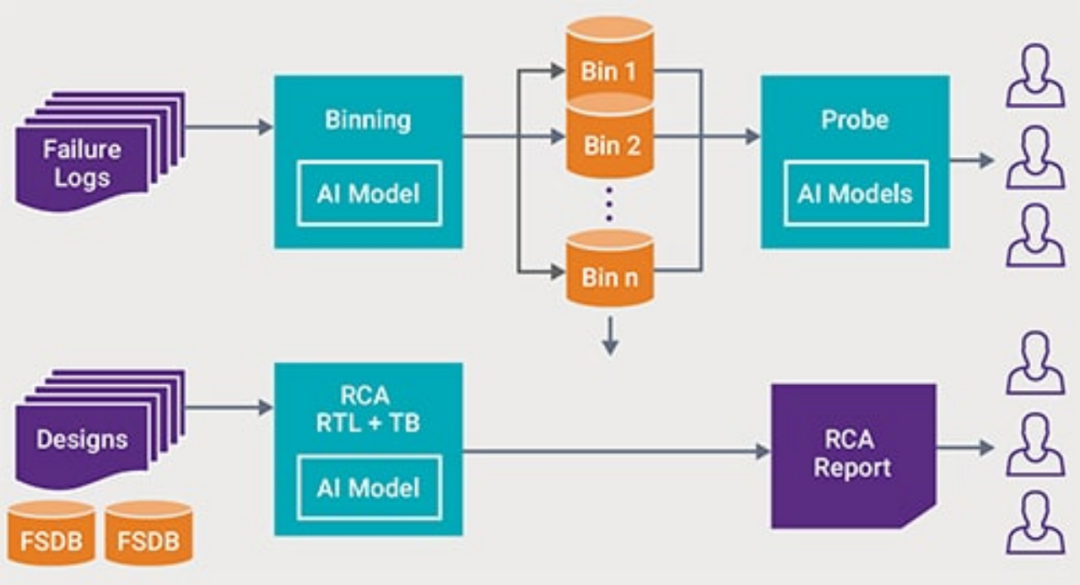

如前所述,模拟回归会在计划中执行无数次。每次回归失败,验证团队都必须检查报告并找出失败的原因。当程序错误被修复或是新增功能需要再次进行测试时,RTL和测试平台程序都会不断地改变,回归失败是家常便饭。手动处理日常的回归失败对验证工程资源是巨大的负担。幸运的是,AI与机器学习再一次提供解药。即使模拟测试失败的原因通常比静态违规的原因更复杂,但依旧适用相同的自动RCA原则。

新思科技Verdi自动调试系统中的回归除错自动化(Regression Debug Automation, RDA)功能会自动丢弃、探查和发现回归失败的根本原因(图8)。RDA会利用AI分类和分析原始的回归失败并辨别在设计和测试台上失败的根本原因。RDA能减少RCA的所需时间,并能提升整体调试效能2倍左右。

图8 Verdi中的回归调试自动化

AI多方位助力芯片验证

AI和机器学习威廉希尔官方网站 每天都在芯片设计和验证流程上寻找更多的应用。特别是在验证领域,AI和机器学习可以在静态验证加速失败分析、改善形式验证的效能、让模拟更有效率、加速收敛并让模拟调试更迅速、更简单。图9总结优化这些程序后对验证团队和整体芯片计划的好处。

图9 AI/ML为验证流程带来的好处

AI与机器学习能提供更好的QOR、更短的TTR和更低的COR来解决关键挑战,可应用于芯片设计诸多面向。

审核编辑:郭婷

-

eda

+关注

关注

71文章

2755浏览量

173219 -

AI

+关注

关注

87文章

30763浏览量

268917 -

人工智能

+关注

关注

1791文章

47208浏览量

238301

原文标题:借力EDA,AI芯片全速优化验证过程

文章出处:【微信号:ICViews,微信公众号:半导体产业纵横】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

翱捷科技完成5G RedCap实验室和外场关键威廉希尔官方网站 验证

是德科技助力三星电子验证FiRa 2.0安全测距测试用例

小鹏AI科技日:图灵AI芯片40天完成2791项验证

盘古22K开发板

解决验证“最后一公里”的挑战:芯神觉Claryti如何助力提升调试效率

解锁SoC “调试”挑战,开启高效原型验证之路

快速部署原型验证:从子卡到调试的全方位优化

形式验证如何加速超大规模芯片设计?

ALVA Systems 创新 AI/AR 威廉希尔官方网站 实现检修设备作业流程高效验证

大规模 SoC 原型验证面临哪些威廉希尔官方网站 挑战?

三大验证关键挑战 AI多方位助力芯片验证

三大验证关键挑战 AI多方位助力芯片验证

评论