一个packed structure有很多的bits组成,这些bit在物理上连续存储。packed structure只允许包含packed数据类型。

struct packed signed {

byte BE; //2-state

int addr; //2-state

int data; //2-state

} pStruct; //signed, 2-state

在上面的例子中,我们显式地将packed struct声明为“signed”。

如果一个packed structure中的所有数据类型都是2-state,structure作为一个整体被视为一个2-state向量。

如果一个packed structure中的存在一个数据的数据类型是4-state,structure作为一个整体被视为一个4-state向量。

一个unsigned structure示例:

struct packed unsigned {

integer addr; //4-state

logic [31:0] data; //4-state

int burst; //2-state

} upStruct; //unsigned, 4-state

在上面的例子中,成员中存在4-state变量,所以整个结构体被视为一个4-state变量。

module SU;

struct packed {

bit [7:0] intr; //packed struct

logic [23:0] addr;

} SUR;

initial begin

SUR.intr = 'hFF;

$display($stime,,, "SUR = %h",SUR);

$display($stime,,, "SUR Intr = %h",SUR.intr);

//Assign by position

SUR = '{'h00,'hFF_FF_FF};

$display($stime,,, "SUR = %h",SUR);

//Assign by name

SUR = '{intr:'h01, addr:'hf0f0f0};

$display($stime,,, "SUR = %h",SUR);

//Assign default

SUR = '{default:'h123456};

$display($stime,,, "SUR = %h",SUR);//Assign default

SUR = '{default:'h78};

$display($stime,,, "SUR = %h",SUR);

SUR = 0;

SUR = SUR+'h12; //Arithmetic operation.

// packed structure can be used as a vector

$display($stime,,, "SUR = %h",SUR);

end

endmodule

仿真log:

0 SUR = ffxxxxxx 0 SUR Intr = ff 0 SUR = 00ffffff 0 SUR = 01f0f0f0 0 SUR = 56123456 0 SUR = 78000078 0 SUR = 00000012 V C S S i m u l a t i o n R e p o r t

在这个例子中,我们给结构体中的单个成员赋值(通过名称或者位置索引),也可以将结构体作为一个整体赋值和算术运算。

给整个结构体赋值需要使用‘{…},这个{}在这里不是连接的含义,而是结构体中各个成员的集合。

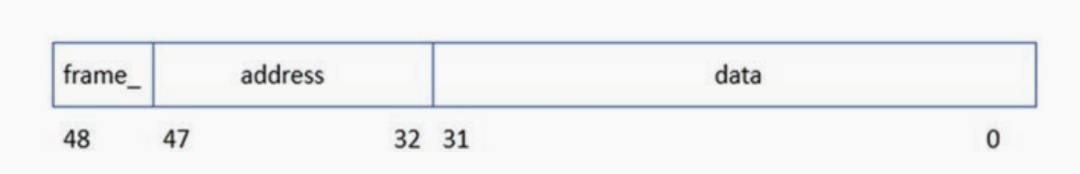

下面是一个packed结构体,以及其在内存中的存放示意图。

struct packed {

logic frame_;

logic [15:0] address;

logic [31:0] data;

} control;

审核编辑:汤梓红

-

Verilog

+关注

关注

28文章

1351浏览量

110078 -

System

+关注

关注

0文章

165浏览量

36930 -

结构体

+关注

关注

1文章

130浏览量

10840

原文标题:SystemVerilog中的Packed Structure

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SystemVerilog中的“const”类属性

基于事件结构的SystemVerilog指称语义

SpinalHDL中Bundle数据类型的转换

SystemVerilog中$cast的应用

unpacked数组和packed数组的主要区别

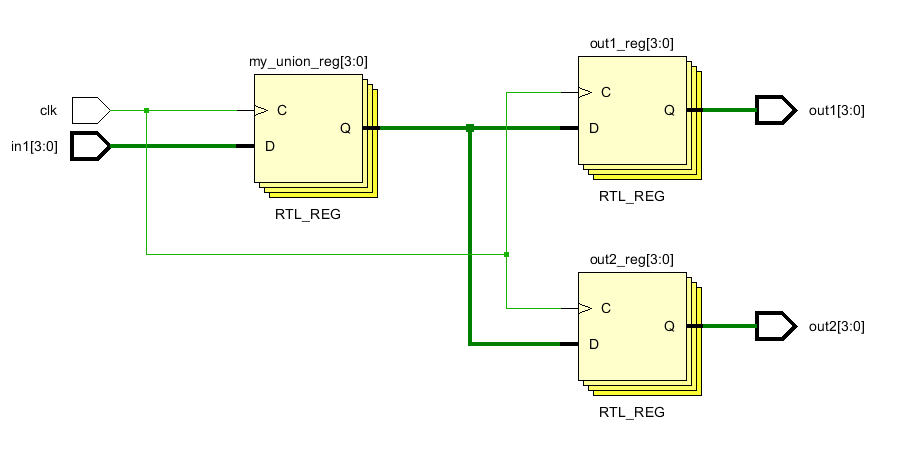

SystemVerilog中的Packed Union

SystemVerilog中的Semaphores

SystemVerilog中至关重要的结构体和自定义类型

Systemverilog中的Driving Strength讲解

SystemVerilog中的Packed Structure

SystemVerilog中的Packed Structure

评论