VHDL、Verilog和SystemVerilog的比较

简介

各种硬件描述语言 (HDL) 在过去几年中不断增强,确定哪种语言适合哪种设计的复杂性也随之增加。许多设计人员和组织正在考虑是否应该从一种 HDL 切换到另一种HDL。

本文比较了三种通用 HDL 的威廉希尔官方网站 特性:

VHDL (IEEE-Std 1076):一种由多种验证和综合(实现)工具支持的通用数字设计语言。

Verilog (IEEE-Std 1364):一种通用数字设计语言,支持多种验证和综合工具。

SystemVerilog:Verilog 的增强版本。

语言的“感觉”

每个 HDL 都有自己的风格和特点。以下描述提供了每种语言的整体“感觉”。文章末尾的表格提供了更详细的功能比较。

VHDL

VHDL 是一种强类型且类型丰富的语言。源自 Ada 编程语言,其语言要求比 Verilog 更冗长。额外的冗长旨在使设计自我记录(所谓的更严谨)。此外,强类型需要额外的编码才能从一种数据类型显式转换为另一种数据类型。

VHDL 的创建者强调明确的语义和易于从一种工具移植到另一种工具的设计。因此,作为语言和工具实现的产物,竞争条件不是 VHDL 用户关心的问题。

已经开发了几个相关的标准来增加语言的实用性。今天的 VHDL 设计都依赖于 IEEE-Std 1164(std_logic 类型),并且许多还依赖于标准的 Numeric 和 Math 包。相关标准的开发是 VHDL 作者的另一个目标:即产生一种通用语言并允许开发可重用的包以涵盖语言中未内置的功能。

VHDL 没有在语言中定义任何仿真控制或监视功能。这些功能取决于工具。

由于缺乏语言定义的仿真控制命令以及 VHDL 的用户定义类型功能,VHDL 社区通常依赖交互式 GUI 环境来调试设计问题。

Verilog

Verilog 是一种弱类型和有限类型的语言。它的传统可以追溯到 C 编程语言和称为 Hilo 的旧 HDL。

Verilog 中的所有数据类型都在语言中预定义。Verilog 承认所有数据类型都有位级表示。支持的数据可以在 Verilog 中自由混合。

Verilog 中的仿真语义比 VHDL 中的更加模糊。这种模糊性为设计人员在应用优化方面提供了更大的灵活性, 但如果不遵循编码准则,它也可能(并且经常会)导致竞争条件 。有可能在不同供应商的工具上甚至在同一供应商工具的不同版本上产生不同结果的设计。

与 VHDL 的创建者不同,Verilog 的作者认为他们为设计人员提供了语言所需的一切。语言的范围更有限,加上缺乏打包能力,即使不是不可能,也很难开发语言中尚未包含的可重用功能。

Verilog 在语言中定义了一组基本的仿真控制能力(系统任务)。

由于这些预定义的系统任务和缺乏复杂的数据类型,Verilog 用户经常运行批处理或命令行仿真,并通过查看仿真结果数据库中的波形来调试设计问题。

SystemVerilog

SystemVerilog 的父级显然是 Verilog,但该语言还受益于称为 Superlog 的专有 Verilog 扩展以及 C 和 C++ 编程语言的特点。

SystemVerilog 通过添加丰富的用户定义类型系统来扩展 Verilog。它还添加了强类型功能,特别是在用户定义类型领域。但是,VHDL 中类型检查的强度仍然超过了 SystemVerilog。而且,为了保持向后兼容性,SystemVerilog 为内置的 Verilog 类型保留了弱类型。

由于 SystemVerilog 是一种比 Verilog 更通用的语言,它提供了定义和打包该语言中尚未包含的可重用功能的能力。

SystemVerilog 还增加了针对测试台开发、基于断言的验证以及接口抽象和封装的功能。

强类型的优点和缺点

强类型的好处是在验证过程中尽早发现设计中的错误。在分析/编译源代码的过程中有很多都是强类型发现的问题,在仿真过程中可能会发现更多问题。

强类型的缺点是性能成本。由于工具必须对源代码进行检查,因此编译速度往往较慢。

当启用运行时检查时,仿真也会由于检查开销而变慢。此外,由于设计人员在编写代码时必须编写类型转换函数并插入类型转换或显式声明的转换函数,因此设计人员的工作效率在编写代码阶段可能会降低。

1,000,000 元的问题是:强类型的好处是否超过成本?

这个问题没有一个正确答案。一般来说,VHDL 语言设计者想要一种安全的语言,能够在流程的早期捕获尽可能多的错误。Verilog 语言设计者想要一种设计者可以使用的语言——用来快速编写模型。SystemVerilog 的设计者正试图通过在增强领域提供强类型来提供两全其美,同时不会显着影响代码编写和建模效率。

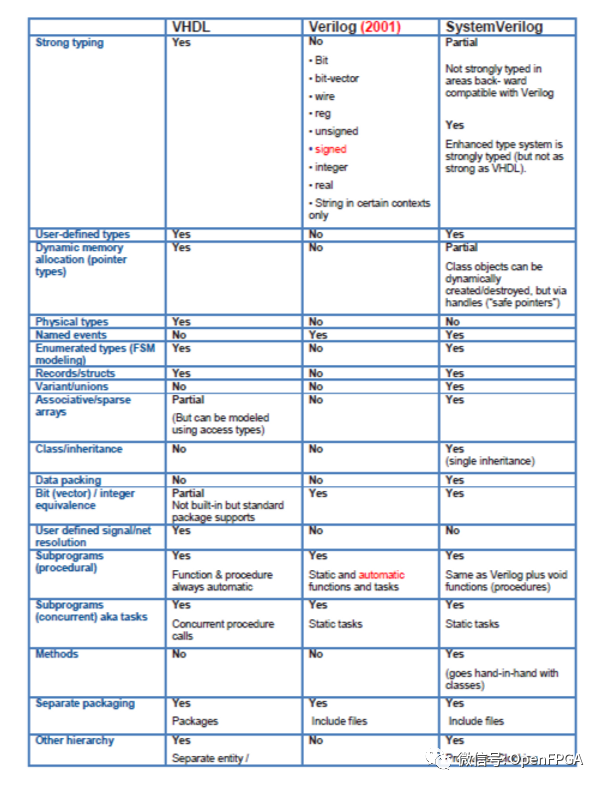

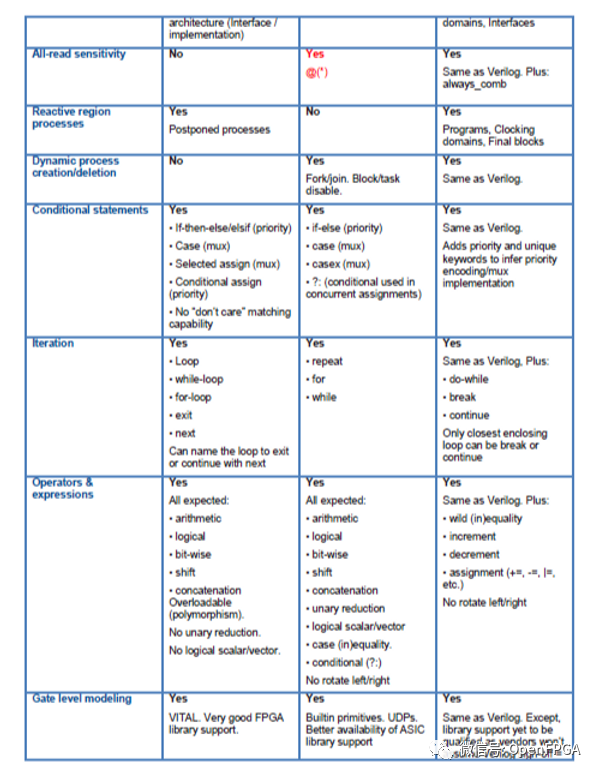

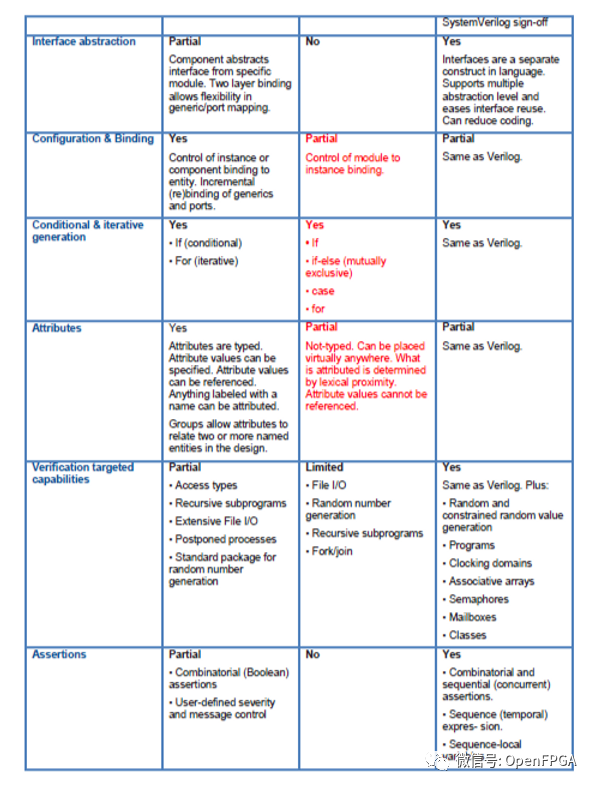

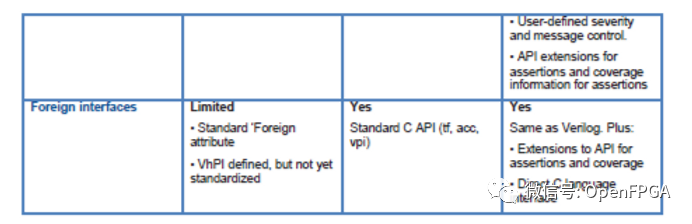

语言特征比较

下表显示了三种 HDL 的逐个特性比较。请注意,红色字体将 Verilog 2001 功能与 Verilog 1995 功能区分开来。

总结

除了上面的语言特性比较之外,这里还有一些需要考虑的最后几点:

SystemVerilog 是一个新兴的标准,仍在不断发展。SystemVerilog 拥有一系列引人注目的功能,是当前 Verilog 用户可能的迁移路径。但是目前一些综合工具支持的还不是支持的特别好~

对于VHDL 用户,许多SystemVerilog 和Verilog 2001 增强功能已经以VHDL 语言提供。还有一项新的 VHDL 增强工作正在进行中,它将为该语言添加测试平台和扩展的断言功能(SystemVerilog 将在这两个领域提供超过 VHDL 2002 的价值)。考虑到更改流程和工具的成本以及培训所需的投资,必须非常慎重地考虑是否放弃 VHDL(应该都不会)。

-

硬件

+关注

关注

11文章

3315浏览量

66203 -

HDL

+关注

关注

8文章

327浏览量

47378 -

仿真控制

+关注

关注

0文章

4浏览量

6565

原文标题:VHDL、Verilog和SystemVerilog的比较

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

硬件描述语言(HDL)编码威廉希尔官方网站 :xilinx verilog语法技巧

寄存器用厂家distributed ram描述是否比"HDL通用寄存器描述...

Verilog HDL入门教程(全集)

基于模型设计的HDL代码自动生成威廉希尔官方网站 综述

Verilog HDL综合实用教程

Verilog HDL华为入门教程

Verilog HDL入门教程

Verilog HDL入门教程之Verilog HDL数字系统设计教程

Verilog HDL入门教程

详细介绍基于HDL的FPGA开发流程

HDL是什么_HDL语言的特点

Verilog HDL语言威廉希尔官方网站 要点

通用HDL的威廉希尔官方网站

特性

通用HDL的威廉希尔官方网站

特性

评论