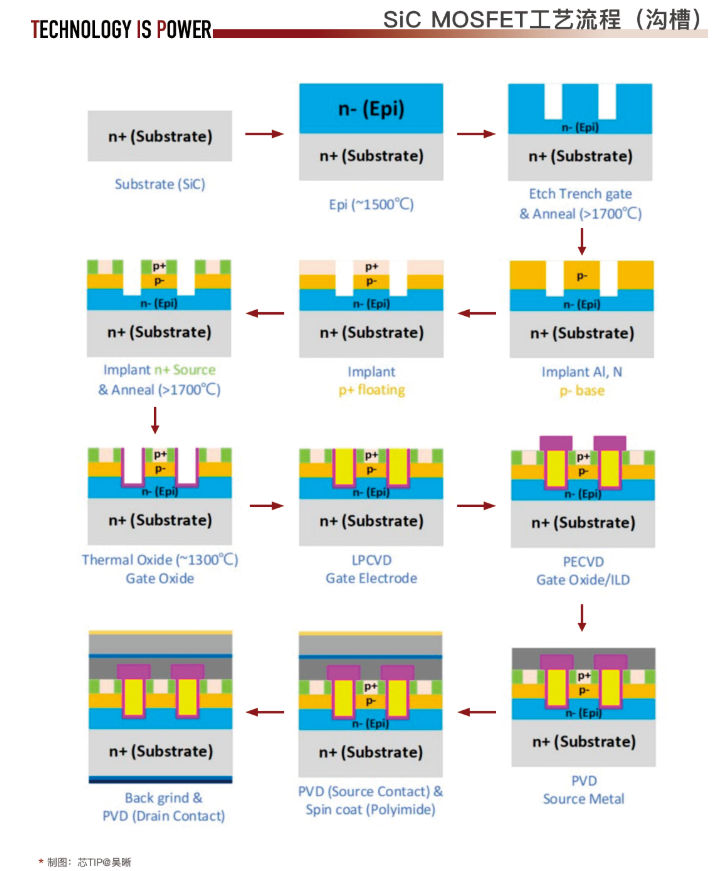

^1.沟槽型SiC MOSFET 工艺流程

在提高 SiC 功率器件性能方面发挥重要作用的最重要步骤之一是器件制造工艺流程。SiC功率器件在用作n沟道而不是p沟道时往往表现出更好的性能;为了获得更高的性能,该器件需要在低电阻率的 p 型衬底上外延生长。

然而,目前市场上商用p型4H-SiC衬底具有相对较高的电阻率(约2.5Ω-cm),比n型衬底的电阻率高出约两个数量级。如果使用高电阻率的p型衬底,n沟道SiC器件的优势就会减弱。因此,由于目前无法获得具有低电阻率的 p 型衬底的问题,通过在商业 n+ 衬底上生长层来研究反向生长以提高性能。

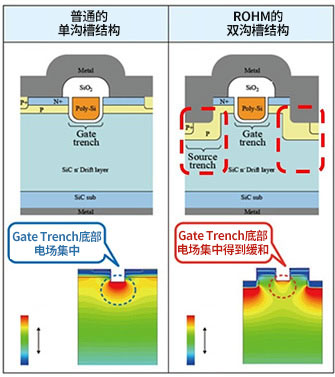

为了进一步提高器件的性能,还考虑了器件的沟槽设计工艺。沟槽结构在Si-MOSFET中得到了广泛的应用,在SiC-MOSFET中也备受关注。沟槽式SiC MOSFET在差分体二极管的导通电阻和器件的导通电阻方面都没有表现出退化,即使在连续的电流应力500小时后也是如此。此外,由于沟槽设计没有JFET区域,沟槽SiC MOSFET的导通电阻比传统设计低。

在沟槽MOSFET的制造工艺步骤中,p基的注入步骤和沟槽的形成步骤可以互换,即先进行p基注入,然后制作沟槽结构,或者先制作沟槽,然后再进行p基注入。上图为首先进行沟槽的制造流程。

工艺步骤如下:

首先,在n+衬底上外延生长n-漂移区;然后,在通过使用Al或N的注入物对结构进行开槽后,开槽的栅极区被用来制作p基区。随后,进行p+注入形成屏蔽区,然后进行n+注入以定义源漏区。在注入步骤之后,将得到的结构暴露在高温下进行热氧化,退火后形成栅氧化物,然后沉积栅电极、源极金属和漏极金属。最后,该结构涂有聚酰亚胺层作为保护性钝化层。为了通过减少 SiC 衬底和外延层中存在的缺陷数量来提高器件的性能,采用了各种离子注入和热氧化工艺方法。

SiC器件的性能、可靠性和稳定性也取决于SiC晶圆的质量,而SiC元件的良率间接影响制造成本。SiC晶圆的总缺陷主要是本征材料缺陷和外延生长造成的结构缺陷。这些缺陷充当复合中心并显着降低厚漂移区的载流子寿命。不同的优化工艺参数,例如 C+ 离子注入/退火、热氧化/退火或沟槽设计,可以将这些缺陷减少到大约 10^11 cm-3 的非常低的水平。

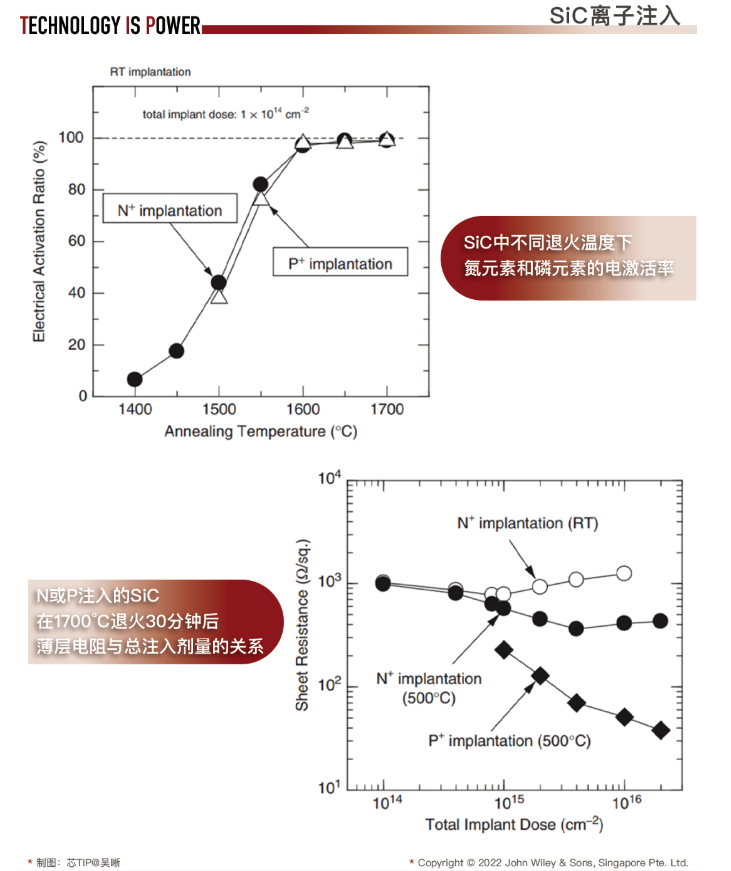

2.SiC离子注入

离子注入是制造几乎所有类型的 SiC 器件的重要工艺。通过离子注入可以实现对n型和p型导电率的大范围掺杂控制。由于 SiC 中掺杂剂的扩散系数非常小,因此在注入后的退火过程中,大部分注入过程中的扩散杂质可以忽略不计。

但是,如果注入过程中对晶格的破坏接近于非晶态,则晶格很难恢复。因此,通常使用高温(~500°C)注入,特别是当注入剂量非常高时。此外,有必要在非常高的温度(>1700°C)下进行注入后退火,以实现晶格恢复和高电激活率。这种高温退火可能会导致不一致的硅蒸发和粗糙的表面。

图中上半部分内容显示了电激活率对注入氮 (N) 或磷 (P) 的 SiC 的退火温度的依赖性;注入在室温 (RT) 下进行。1300℃以下退火温度的活化率非常小(<10%),需要1600~1700℃高温退火才能获得近乎完美的活化率(>95%)。

图中下半部分内容显示了在 1700°C 退火 30 分钟的 N 或 P 注入 SiC 的薄层电阻与总注入剂量之间的关系。当注入剂量相对较低(<3 × 10^14 cm-2)时,无论注入温度(RT 或 500°C)如何,N+ 注入类型的薄层电阻都没有显着差异。在 RT 注入的情况下,注入剂量下的薄层电阻约为 0.7-1 × 10^15 cm-2,并且随着注入剂量的进一步增加而增加。在这个高剂量区域,常温注入造成的晶格损伤非常严重。活化退火后,注入区含有高密度的堆垛层错和3C-SiC晶粒。

另一方面,观察到薄层电阻随着热注入剂量的增加而降低。氮注入区域的最大薄层电阻在 300 Ω/sq. 时几乎饱和,这可能受到 N 原子在 SiC 中相对较低的溶解度的限制。通过热注入 P,薄层电阻可以进一步降低到 30-50 Ω/sq。由于 P 的溶解度极限较高,这个过程是可能的。

审核编辑:汤梓红

-

MOSFET

+关注

关注

146文章

7148浏览量

213076 -

功率器件

+关注

关注

41文章

1757浏览量

90403 -

SiC

+关注

关注

29文章

2797浏览量

62586

原文标题:沟槽型SiC MOSFET 工艺流程及SiC离子注入

文章出处:【微信号:DT-Semiconductor,微信公众号:DT半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

铒离子注入碳化硅后的射程分布和射程离散

SiC-MOSFET的应用实例

沟槽结构SiC-MOSFET与实际产品

SiC功率器件SiC-MOSFET的特点

浅析SiC-MOSFET

如何改良SiC器件结构

4H-SiC离子注入层的欧姆接触的制备

中车时代电气SiC产业化基地离子注入工艺设备威廉希尔官方网站 调试完成

沟槽结构SiC-MOSFET与实际产品

沟槽型SiC MOSFET工艺流程及SiC离子注入

沟槽型SiC MOSFET工艺流程及SiC离子注入

评论