高性能计算需要高性能I/O。一段时间以来,业界一直在努力改进高带宽的远程解决方案。去年Intel和Xilinx都推出了56G I/O的FPGA。长距离112G SerDes PHY已经公布,随着即将推出的5纳米节点的出现,状态可能会更好。再往前看,超过112G的行业路线图充满了不确定性。对于跨度几十米或更长的距离,将使用光通信代替电信号通信。不幸的是,这些产品往往是反向相关的。距离物理裸片越远,传输的成本就越高。同样,较高的数据传输速率通常会牺牲密度,因此单片硅光子芯片被视为信息处理的更好的解决方案。

在过去的十年中,大量实现高集成度的方法被大量商业引入。诸如TSMC CoWoS和Samsung I-Cube之类的硅中介层以及诸如Intel的EMIB,这些封装威廉希尔官方网站 可将多个管芯紧密地集成在同一芯片上。市场上的首批产品通过将DRAM芯片直接封装在CPU旁边,从而提高了带宽并降低了功耗,进而实现了高带宽DRAM。除了内存之外,还需要付出巨大的努力来支持将多个利基用途的芯片(在这种情况下更合适地称为小芯片)结合在一起在封装上,以增强芯片的功能。尽管今天,大多数基于小芯片的设计仅涉及自己开发的小芯片,未来的设计可能会合并多个公司的裸片。此类工作中最早的就是英特尔的Stratix 10 FPGA系列,该系列由包含多个AIB链接的单片FPGA芯片组成。英特尔能够提供多种具有不同功能的小芯片。最近,OCP宣布成立自己的工作组,以推动整个行业的小芯片标准。

Ayar Labs是一家位于加利福尼亚州的硅光子学初创公司。该公司在A轮融资中筹集了2400万美元。Ayar采取了不寻常的方法来追求处理器市场而不是网络。他们的前提很简单–将光学器件尽可能靠近计算芯片,以实现更好的带宽和能效。换句话说,要实现近乎单片的光子集成,获得与其他封装组件相当的每比特传输能量效率,同时实现可以跨越几十到几百米的远程通信。

TeraPHY

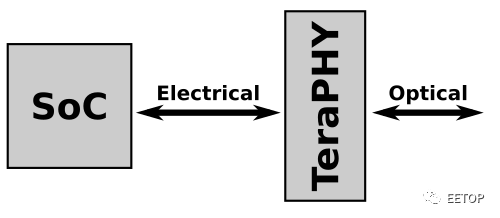

Terabit PHY,简称TeraPHY,是Ayar实验室的第一款产品。这是一个原型光子学芯片,它被设计成与CPU、GPU或FPGA一起集成在包中的系统中。re只是一个小问题——光学和电子并不完全相互通信。秘诀是什么?Ayar的设计利用了GlobalFoundries的45nm RF SOI(绝缘体上的射频硅)工艺,该工艺允许他们开发集成光学元件和光学器件周围的复杂电路的单片集成设计。简而言之:这使他们可以在一侧提供电气I / O接口,在另一侧提供光接口。

英特尔已经开发了一个广泛的芯片架构围绕其层10 FPGA家族。但所有这些芯片都是内部研发的。好消息是,该架构使用AIB接口在主FPGA芯片和各种芯片之间进行通信。作为DARPA ERI项目的一部分,该接口也被作为开放标准开放,因此它不再是英特尔或EMIB的专利。Stratix 10多芯片体系结构使其本身具有TeraPHY提供的功能——用TeraPHY小芯片替换掉一个电子收发器模块,只要接口是兼容的,就可以了。这是Ayar Labs选定的路线。

电信号接口

对于TeraPHY,Ayar集成了AIB接口的24个通道。实际上,每列允许的最大通道数为24个通道(以及AUX块)。每个通道代表一组信号。在当前的凸点间距为55微米时,这意味着二十个发送数据信号和二十个接收数据信号。其运行速度高达2GT/ s。Ayar说,对于他们的TeraPHY小芯片,总接口带宽为960Gbps,这表明他们使用的是1GT/s AIB基本规格,而不是2GT/s AIB Plus规格。

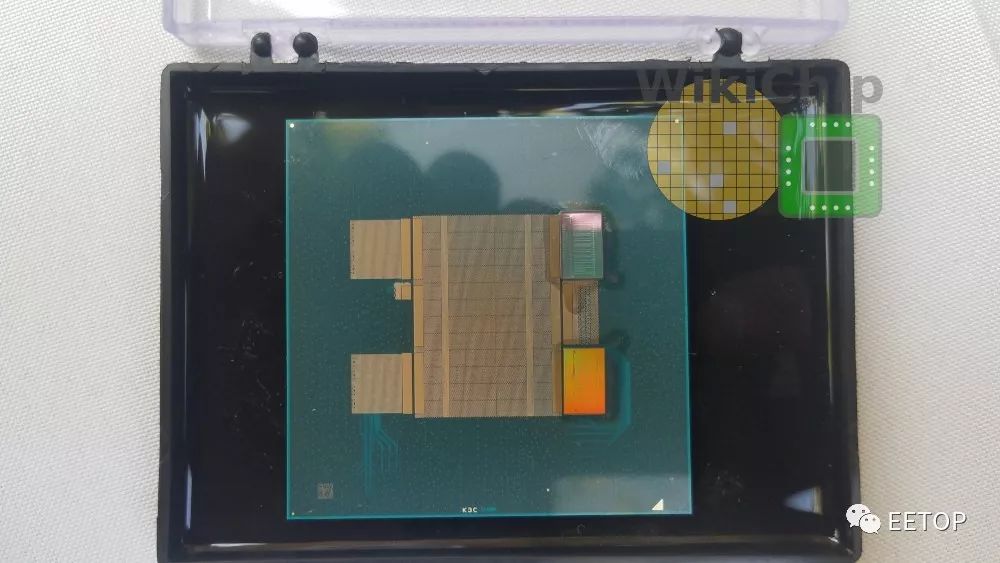

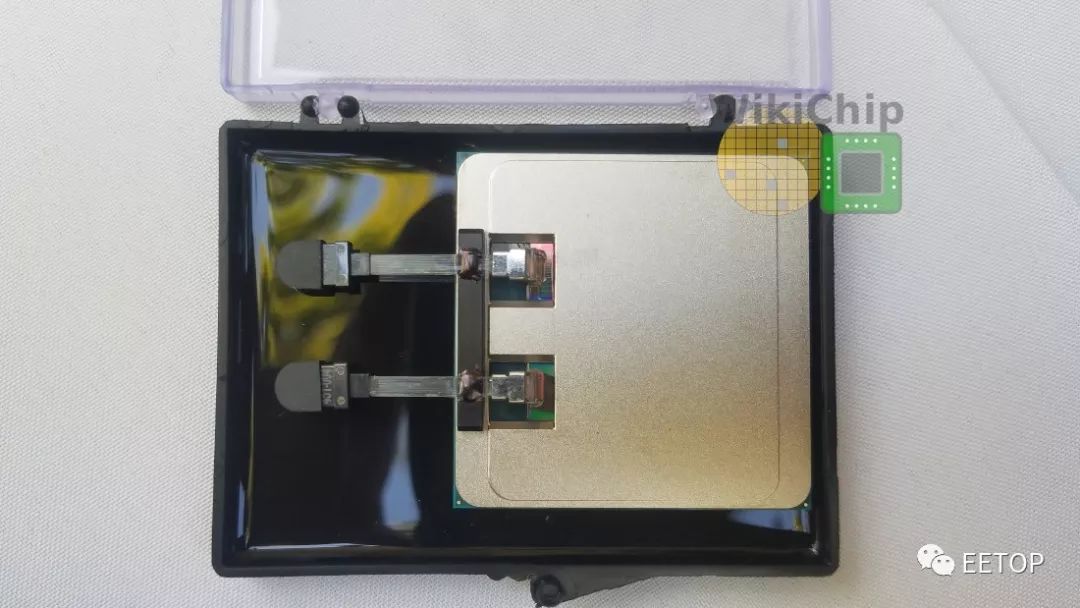

由于AIB接口使用的凸点间距很小,因此可以在硅上使用。在Stratix 10案例中,这意味着使用英特尔的EMIB威廉希尔官方网站 。在下面未完成的封装中,大型Stratix 10 FPGA芯片的右侧有两个TeraPHY小芯片。

EMIB的位置在所有管芯的边缘清晰可见。请注意,FPGA的另一端可能还有其他小芯片。

光信号I/F

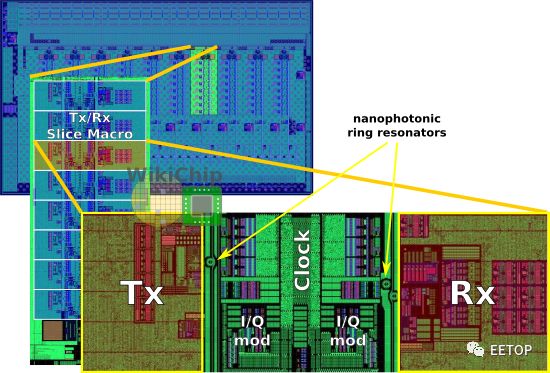

位于AIB接口和光接口之间的是可配置的交叉胶连逻辑,该逻辑将AIB通道映射到光通道。交叉开关允许一对多连接。单个电信号通道可以通过多个光接口发送,反之亦然。TeraPHY小芯片集成了十个光子宏对,一个宏用于发送,一个宏用于接收。

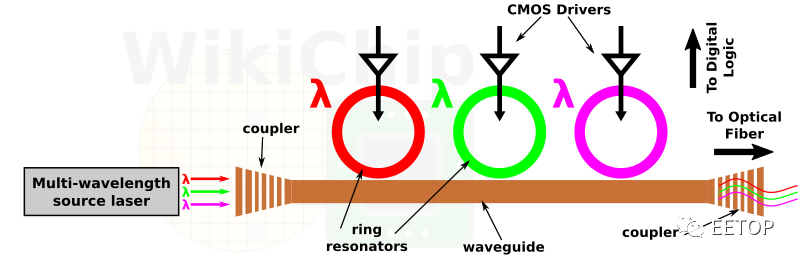

芯片内的光穿过波导。由于光的特性,多种波长的光可以沿着同一波导传播而不会互相干扰。波分复用(WDM)威廉希尔官方网站 用于将多个这样的波长引入到波导中,以增加可以在同一光纤链路上传输的数据量。为了实现这一目标,Ayar在同一波导上使用了多个微环形谐振器,使用来自波导的不同波长将数据与光或电进行数据转换。各个低功率硅光子环形谐振器锁定在它们工作的特定波长上。这些环形谐振器由CMOS驱动器驱动,该驱动器与管芯上的数字逻辑的复位相接口。

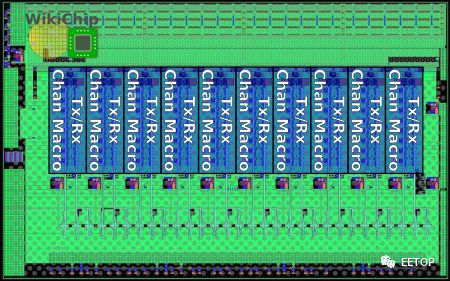

每个宏对中包含一组PLL,TRXSlice和其他使它们全部工作所需的逻辑。如果查看GDSII截图,则可以得出八个TRX切片,每个波长一个。设计每个宏中的各种PLL,以便可以将数据速率配置为高达2x的增量。当前的TeraPHY小芯片允许的数据速率为16 Gbps,25.6 Gbps和最高32Gbps。由于每个波导有八个波长,因此您正在查看每个宏的128 Gbps至256 Gbps的可配置聚合带宽。

当前的TeraPHY小芯片包含10个宏对。这意味着它能够在所有光学宏上提供高达2.56 Tb/s的聚合带宽。这比AIB链接上的所有功能要多得多。目前尚不清楚它们为什么如此不平衡,但是由于可以将单个AIB信道路由到多个光信道,因此在进行此类通信时可能存在拓扑。例如,一个SoC将流量路由到其他两个SoC。值得补充的是,由于在接收端不需要纠错,因此它在光通道上使用NRZ调制格式。

为了与英特尔建立伙伴关系,将两个TeraPHY集成到Stratix 10 FPGA中。这意味着每个FPGA的总光带宽为5.12 Tbps。两个小于50平方毫米的小芯片令人印象深刻!

那么,如何从芯片上物理地取出它呢?输入或输出波导终止于光栅耦合器,光栅耦合器是在其顶表面上具有脊和凹槽的设备,允许光以某个特定角度从波导中散射出去。在这里,将光纤拉到足够近的距离,使其能够收集散射的光。

对于Intel Stratix 10 FPGA,光线从顶部散出。换句话说,TeraPHY组件涉及通过芯片背面对齐和粘合光纤。光纤连接器从盖子顶部直接穿过一个开口,直达TeraPHY小芯片。

英特尔FPGA产品战略与创新副总裁文斯·胡(Vince Hu)表示:“我们看到的数据中心工作负载激增,它们对带宽的需求不满足,而且需要在机架级距离上连接设备。”“做到这一点的最佳方法是使用光学互连,并使用Ayar Labs小芯片,我们可以在低延迟和低功耗的情况下实现很高的带宽。”

由于AIB的延迟极低,仅为3ns左右,因此通过AIB到TeraPHY并通过AIB的往返通信的延迟不到10 ns,而每米的延迟大约为5 ns。光纤(取决于整个系统的配置),最长可达2公里。TeraPHY的总能源效率略低于5 pJ / bit。该数字包含AIB接口,交叉开关和光学宏块。

SuperNova激光

值得一提的是该芯片的工作温度。由于FPGA的功率高达300瓦,而TeraPHY又增加了4.7W,因此该芯片的热量可能会很高– Ayar报告的数字可能高达90摄氏度。GlobalFoundries 45 RF SOI已经满足1级(-40ºC至+125ºC)和Ayar自己的TeraPHY小芯片的要求,该设计通过能够跟踪和管理热量变化的额外控制调谐逻辑来承受这些温度。不幸的是,对于光源(激光器),它可能会遭受这些温度的影响,这可能会影响设备的可靠性。

为此原因,Ayar Labs还开发了一种称为SuperNova的外部激光器。SuperNova当前支持八个和十六个波长。波长被多路复用并放大到八个或十六个输出端口上。换句话说,Ayar当前的SuperNova激光器总共支持256个通道,总带宽为8.192 Tbps。激光的功率效率为1-2 pJ / bit。

潜在的路线图改进

Ayar Labs TeraPHY小芯片显示出集成光子学的潜力。对于同类产品而言,这一数字令人印象深刻。Stratix 10上的第一代AIB接口在第一代EMIB的55微米微凸点间距上的能效约为0.85pJ / bit。英特尔最近谈论了很多计划,将这个数字降低多达0.5 pJ / bit或更多。能源效率的提高与更高密度的微型凸块相结合,应该能够以与当前原型机相似的功率获得更高的带宽。此外,Ayar当前的TeraPHY小芯片利用WDM以便在同一波导上以八个波长发送八个比特。即使我们假设他们不会再添加任何渠道,它们实际上可以使TeraPHY小芯片上的波长数量增加一倍,从而使光I/O带宽增加一倍。Ayar的SuperNova激光器已经支持16种波长。在Supercomputing 2019上,Ayar Lab宣称将于于2020年第一季度开始送样。

审核编辑 :李倩

-

处理器

+关注

关注

68文章

19274浏览量

229734 -

芯片

+关注

关注

455文章

50761浏览量

423368 -

接口

+关注

关注

33文章

8586浏览量

151083

原文标题:带宽高达5.12 Tbps!FPGA首次集成光子芯片,即将送样

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA首次集成光子芯片,即将送样

FPGA首次集成光子芯片,即将送样

评论